CN100423221C - 测试电子装置用电接触元件的制造方法及所制得的电接触元件 - Google Patents

测试电子装置用电接触元件的制造方法及所制得的电接触元件 Download PDFInfo

- Publication number

- CN100423221C CN100423221C CNB028277597A CN02827759A CN100423221C CN 100423221 C CN100423221 C CN 100423221C CN B028277597 A CNB028277597 A CN B028277597A CN 02827759 A CN02827759 A CN 02827759A CN 100423221 C CN100423221 C CN 100423221C

- Authority

- CN

- China

- Prior art keywords

- groove

- electric contacts

- tip portion

- header portion

- sacrificial substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R3/00—Apparatus or processes specially adapted for the manufacture or maintenance of measuring instruments, e.g. of probe tips

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R1/00—Details of instruments or arrangements of the types included in groups G01R5/00 - G01R13/00 and G01R31/00

- G01R1/02—General constructional details

- G01R1/06—Measuring leads; Measuring probes

- G01R1/067—Measuring probes

- G01R1/06711—Probe needles; Cantilever beams; "Bump" contacts; Replaceable probe pins

- G01R1/06716—Elastic

- G01R1/06727—Cantilever beams

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R1/00—Details of instruments or arrangements of the types included in groups G01R5/00 - G01R13/00 and G01R31/00

- G01R1/02—General constructional details

- G01R1/06—Measuring leads; Measuring probes

- G01R1/067—Measuring probes

- G01R1/06711—Probe needles; Cantilever beams; "Bump" contacts; Replaceable probe pins

- G01R1/06733—Geometry aspects

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R1/00—Details of instruments or arrangements of the types included in groups G01R5/00 - G01R13/00 and G01R31/00

- G01R1/02—General constructional details

- G01R1/06—Measuring leads; Measuring probes

- G01R1/067—Measuring probes

- G01R1/073—Multiple probes

- G01R1/07307—Multiple probes with individual probe elements, e.g. needles, cantilever beams or bump contacts, fixed in relation to each other, e.g. bed of nails fixture or probe card

- G01R1/07342—Multiple probes with individual probe elements, e.g. needles, cantilever beams or bump contacts, fixed in relation to each other, e.g. bed of nails fixture or probe card the body of the probe being at an angle other than perpendicular to test object, e.g. probe card

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/40—Forming printed elements for providing electric connections to or between printed circuits

- H05K3/4092—Integral conductive tabs, i.e. conductive parts partly detached from the substrate

Abstract

本发明公开了一种用于测试电子装置的电接触元件的生产方法以及一种通过形成具有尖端部分和横梁部分的电接触元件来生产的电接触元件。该方法包括限定沟槽之后,在该沟槽中进行一次或多次各向异性蚀刻,从而增加沟槽的深度,并使沟槽的内表面变得圆滑。该由接触元件包括横梁部分和尖端部分。其中横梁部分具有多阶梯构形,包括宽度逐级增加的三个条形部分,其每个部分通过凸起以另一端与电子元件相连;并且尖端部分与横梁部分中第一部分的自由端整体形成。

Description

技术领域

本发明涉及用于测试电子装置的电接触元件的制造方法和由该方法制造的电接触元件,更具体地,本发明涉及制造一种电接触元件的方法,所述电接触元件能够通过与电子装置接触来测试该电子装置,以确定该电子装置是否处于正常状态,本发明还涉及由这种方法制造的电接触元件。

此外,本发明涉及一种电接触元件的制造方法,该电接触元件由于存在靠手(armrest)而增大物理作用力,而能够电测试电子装置,本发明还涉及由该方法制造的电接触元件。

背景技术

一般来说,通过进行一系列半导体制造过程在半导体衬底上获得半导体芯片,所述半导体制造过程包括氧化过程、扩散过程、离子注入过程、蚀刻过程、金属化过程等。在半导体衬底上制备的芯片通过电衰减分类(EDS)测试分成正品和次品。然后只有正品放在切片和封装过程中。

此时,在EDS测试中,使诸如探针板的电接触元件与半导体芯片的一个基座接触,来对其施加电信号,然后通过检测对所施加的电信号的电信号响应,可以确定该芯片是否处于正常状态。

同时,在通过进行一系列平板显示装置制造过程制造的平板显示装置如液晶显示器中,使电接触元件与平板显示装置的预选部分接触,来对其施加电信号,然后通过检测对所施加的电信号的电信号响应,确定该LCD板是否处于正常状态。

目前,已经努力进行研发,以确保用于测试半导体芯片或诸如LCD的平板显示器等的正常性的常规电接触元件符合最近的发展趋势,即在高度集成的半导体装置如1G DRAM中间距变小的趋势,使常规电接触元件具有快速响应速度,以便用于高频段中,具有足够的强度,以便不会由于反复接触而磨损,保持预定的接触电阻,以具有优异的导电性,以及具有足够的过驱动(over-drive)(OD)特性。

具体地,已经努力进行研究和开发,以保证当电接触元件反复与高度集成的半导体装置接触时,在电接触元件上产生的颗粒最少,电接触元件具有优异的导电性,多个电接触元件的尖端部分可以同时与半导体芯片基座接触以满足过驱动方案的需要。

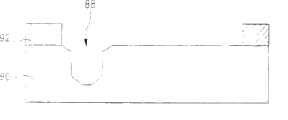

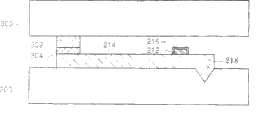

如图1所示,在常规的电接触元件中,诸如其上已经形成预定电路图案的印刷电路板(PCB)等电子元件(10)的端子与立柱部分12连接。立柱部分12与横梁部分14连接,而横梁部分14又与尖端部分16连接。

此时,立柱部分12、横梁部分14和尖端部分16单独提供并且相互之间通过粘合剂连接。横梁部分14具有恒定宽度的条形构形。

具体地,尖端部分16具有棱柱形状的构形,其具有四个角和一个尖角状末端。

因此,电接触元件的尖端部分16通过恒定的物理作用力F反复与半导体芯片基座接触,并具有希望的OD特性,以便将恒定的电信号施加到半导体芯片上,从而确认该半导体芯片是否处于正常状态。

但是,常规的电接触元件问题在于:由于尖端部分具有尖角状末端,并且电接触元件的尖端部分通过恒定的物理作用力F反复与半导体芯片的基座(pad)接触,尖端部分可能刺入基座上形成的氧化物膜并损坏基座,由此当进行诸如引线连接等的后续半导体制造过程时有缺陷部分必然增大。

此外,由于常规电接触元件在其侧面有多个角,当尖端部分与半导体芯片的基座接触时,尖端容易被磨损并且其本身产生颗粒,这会污染高度集成的半导体芯片。

同时,由于电接触元件的尖端部分具有有尖角的末端,在该尖端部分与半导体芯片基座之间的接触区域只能减小,从而减小导电性。

而且,当电接触元件必须通过恒定的物理作用力F与半导体芯片基座接触以保证希望的OD特性时,由于尖端部分长度短,因此难以合适地调节OD特性。

也就是说,当多种电接触元件提供在探针卡上并布置以限定预定的轮廓时,由于电接触元件的尖端部分长度短,难以适当地调节该多种电接触元件的高度,以获得希望的OD特性。

由于尖端部分的结构或构形方面的发展也可能产生上述问题。

即原来具有钨质针形构形的尖端部分已经发展成具有V形或棱柱形构形。棱柱形尖端部分已经发展成为具有截头棱柱形构形。

钨质针形尖端部分的缺点在于:在弄尖尖端部分的末端时,由于弄尖末端的工作手工进行,破坏了尖端部分的重复性和生产率。同时,由于棱柱形和截头棱柱形尖端部分有带角的角部,并且尖端部分反复与半导体装置的基座接触,尖端部分可能在角部被磨损。所以,必须减小或除去角部的锐度。

因此,如上所述,当反复进行多个电子器件的测试时,由于在尖端部分的有尖角的末端和角部产生的颗粒的存在,必须经常洗涤尖端部分,结果不能快速连续地进行测试。

此外,在最近开发的高频型电子装置明显受到噪声影响时,由于尖端部分被磨损,所以不能均匀地形成接触点,从而必然降低测试的可靠性。

由于这一原因,需要在短时间内进行测试,以提高生产率。

此外,由于横梁部分具有条形构形,所以不能完全符合最近的发展趋势,即在高度集成的半导体器件中间距变小的趋势。同时,当电接触元件通过物理作用力F与半导体芯片基座接触时,应力集中在横梁部分上的某点处并且横梁部分可能被破坏。

另外,由于在横梁部分和尖端部分之间的连接区域小,当电接触元件通过恒定物理作用力F与半导体芯片基座接触时,应力集中到连接区域上并且尖端部分可能被破坏。

此外,当在常规电子器件测试设备中必须增大施加到尖端部分上的恒定物理作用力以便保证希望的OD特性并且在半导体芯片基座上形成的氧化物膜可能被刺穿时,由于常规电接触元件所具有的各种不利因素而产生问题。

具体来说,当为了增大恒定物理作用力F而必须缩短横梁部分的长度时,如果缩短横梁部分的长度,难以获得希望的OD特性,并且过大的应力可能局部施加到横梁部分上,因此横梁部分可能被破坏。

发明内容

因此,本发明致力于解决在相关技术中产生的问题,本发明的一个目的是提供一种用于测试电子装置的电接触元件的制造方法,它能够克服常规技术的问题,因为常规电接触元件的尖端部分在其边上有若干个角部,当该尖端部分与半导体芯片的基座接触时,尖端部分被磨损并且本身产生颗粒,本发明还提供用所述方法制备的电接触元件。

本发明的另一个目的是提供一种用来检测电子装置的电接触元件的制造方法,它能够克服常规技术的问题,因为常规电接触元件的尖端部分具有一个有尖角的尖端,降低导电性,本发明还提供用所述方法制备的电接触元件。

本发明的另一个目的是提供一种用来检测电子装置的电接触元件的制造方法,它能够克服常规技术的问题,因为常规电接触元件的尖端部分具有一个有尖角的尖端,当尖端部分通过恒定的物理作用力与半导体芯片基座反复接触时,尖端部分刺穿基座上形成的氧化物膜并损坏该基座,当进行诸如引线连接过程等后续半导体制造过程时废品比例增大,本发明还提供用所述方法制备的电接触元件。

本发明的另一个目的是提供一种用来检测电子装置的电接触元件的制造方法,其中增大尖端部分的长度以便容易实现希望的OD特性,本发明还提供用该方法制备的电接触元件。

本发明的另一个目的是提供一种用来检测电子装置的电接触元件的制造方法,它能够完全符合最近的趋势,即诸如高度集成的半导体芯片等电子装置中所要求的间距变小的趋势,本发明还提供用所述方法制备的电接触元件。

本发明的另一个目的是提供一种用来检测电子装置的电接触元件的制造方法,它能够克服常规技术的问题,当常规电接触元件的尖端部分通过恒定的物理作用力反复与半导体芯片基座接触时,应力集中在横梁部分上的某点处,并且横梁部分被损坏,本发明还提供用所述方法制备的电接触元件。

本发明的另一个目的是提供一种用来检测电子装置的电接触元件的制造方法,它能够克服常规技术的问题,由于在常规电接触元件的横梁部分与尖端部分的连接区域小,当电接触元件通过恒定物理作用力反复与半导体芯片的基座接触时,应力集中到小的连接区域上并且尖端部分被损坏,本发明还提供用所述方法制备的电接触元件。

本发明的另一个目的是提供一种用来检测电子装置的电接触元件的制造方法,该电接触元件相对于其横梁部分和尖端部分具有改善的重复性,本发明还提供用所述方法制备的电接触元件。

本发明的另一个目的是提供一种用来检测电子装置的电接触元件的制造方法,它能够减小由于装置的基座上形成的颗粒和划痕产生的损坏,并且具有增大了接触区域的尖端部分,从而改善生产率,本发明还提供用所述方法制备的电接触元件。

本发明的另一个目的是提供一种用来检测电子装置的电接触元件的制造方法,该电接触元件由于存在靠手而能够通过增大其物理作用力来电检测电子装置,以确定电子装置是否处于正常状态,本发明还提供用该方法制备的电接触元件。

为了实现上述目的,根据本发明的一个方面,提供了一种用于检测电子装置的电接触元件的制造方法,即在消耗性的衬底上限定一个其中要形成尖端部分的沟槽,形成保护膜图案使得该保护膜图案定出将要在其中形成横梁部分的开口区并且与所述沟槽相连通,向所述开口区中填充导电材料,除去消耗性衬底和保护膜图案以形成具有尖端部分和横梁部分的电接触元件,该方法包括以下过程:在限定沟槽后,在沟槽内进行一次或多次各向异性的蚀刻,以增大沟槽的深度并使沟槽内表面变圆滑。

根据本发明的另一个方面,在沟槽内进行一次或多次各向异性蚀刻以增大沟槽深度并使沟槽内表面变圆滑的过程通过反应性离子蚀刻(RIE)法进行。

根据本发明的另一个方面,横梁部分具有多阶梯构形,其包括与尖端部分连接的第一条形部分,与第一部分连接的第二条形部分,第二部分的宽度大于第一部分,与第二部分连接的第三条形部分,第三部分的宽度大于第二部分。作为替代的方案,横梁部分具有之字形构形,其包括与尖端部分连接的第一条形部分,与第一部分连接并且之字形弯曲一次或多次的第二之字形部分,以及与第二部分连接的第三条形部分。

根据本发明的另一个方面,尖端部分的末端具有截头多边形棱柱形或截头圆锥形构形,并具有圆滑的末端表面。作为替代的方案,尖端部分的末端具有柱状构形,并具有圆滑的末端表面,在尖端部分的近端(proximal end)附近形成凸出部分。

根据本发明的另一个方面,提供一种用于测试电子装置的电接触元件的制造方法,即在消耗性衬底上限定将要在其中形成尖端部分的沟槽,形成第一保护膜图案使得第一保护膜图案定出将要在其中形成横梁部分的第一开口区,并且该开口区与所述沟槽相通,向第一开口区中填充导电性材料,除去消耗性衬底和第一保护膜图案,以形成具有尖端部分和横梁部分的电接触元件,所述方法包括以下过程:在限定沟槽后,在沟槽中进行一次或多次各向异性蚀刻以增大沟槽的深度并使沟槽内表面变圆滑;向由第一保护层在消耗性衬底上定出的预定厚度的第一开口区中填充导电性材料,以形成尖端部分和横梁部分,然后整平第一所得产品上表面;在经过整平过程的第一所得产品上形成第二保护膜图案使得第二保护膜图案定出将要在其中形成靠手的第二开口区,该第二开口区靠近将要在其中形成尖端部分的沟槽;向由第二保护层在第一所得产品上限定了预定厚度的第二开口区中填充导电性材料,以形成所述靠手,然后整平第二所得产品的上表面;除去第二保护膜图案、第一保护膜图案和消耗层,制成具有尖端部分、横梁部分和靠手的电接触元件。

根据本发明的另一个方面,尖端部分的末端具有截头多边形棱柱形、截头圆锥形或柱形构形,并具有圆滑的尖端表面,在尖端部分的近端附近形成凸出部分。

根据本发明的另一个方面,提供一种用于测试电子装置的电接触元件,包括:具有多阶梯构形的横梁部分,该横梁部分包括第一条形部分、与第一部分连接并且宽度大于第一部分的第二条形部分,和至少一段与第二部分相连并且宽度大于第二部分的第三条形部分,第三部分在其另一端通过一个凸起(bump)与一个电子元件相连;所述电接触元件还包括在与横梁部分的第一部分的自由端相应的位置处在消耗性衬底上限定的沟槽,其通过使用第一保护膜图案作为蚀刻掩模进行一次或多次第一各向同性蚀刻而形成,其形成方式使得沟槽的下表面变圆滑;所述电接触元件还包括尖端部分,其通过在除去第一保护膜图案后在消耗性衬底上涂敷第二保护膜图案、向沟槽中填充导电性材料、整平所得产品的上表面、通过湿法蚀刻除去消耗性衬底和第二保护膜图案而形成。

根据本发明的另一个方面,提供一种用于测试电子装置的电接触元件,包括:具有多个之字形构形的横梁部分,该横梁部分包括通过一个凸起与电子元件连接的第一条形部分、与第一部分连接并且之字形弯曲一次或多次的第二之字形部分,和与第二部分相连的第三条形部分;所述电接触元件还包括在与横梁部分的第三部分的自由端相应的位置处在消耗性衬底上限定的沟槽,其通过使用第一保护膜图案作为蚀刻掩模进行一次或多次第一各向同性蚀刻而形成,其形成方式使得沟槽的下表面变圆滑;所述电接触元件还包括尖端部分,其通过在除去第一保护膜图案后在消耗性衬底上涂敷第二保护膜图案、向沟槽中填充导电性材料、整平所得产品的上表面、通过湿法蚀刻除去消耗性衬底和第二保护膜图案而形成。

根据本发明的另一个方面,通过进行一次或多次各向异性蚀刻,所述沟槽具有截头多边棱柱形、截头圆锥形或柱形段,并具有倾斜的沟槽侧表面。

根据本发明的另一个方面,尖端部分的末端具有柱形构形,并具有圆滑的末端表面,在尖端部分的近端附近形成第一和第二凸出部分(projection)。

根据本发明的另一个方面,提供一种用于测试电子装置的电接触元件,包括:在其表面上用具有预定厚度的第一光刻胶形成的消耗性衬底;通过使第一光刻胶图案化限定的第一开口区,用于使尖端部分可以在其中形成;使用第一光刻胶图案作为蚀刻掩模可以在其中形成尖端部分的沟槽,该沟槽经过各向异性蚀刻过程使尖端部分圆滑,在消耗性衬底上形成的第一光刻胶图案通过灰化除去;之字形弯曲一次或多次的之字形横梁部分和靠手,其通过向消耗性衬底上由第二光刻胶图案定出的第二开口区中填充用于形成尖端和横梁部分的导电性材料到预定厚度并通过化学气相沉积(CVD)、物理气相沉积(PVD)或镀膜法进行、整平所得产品的上表面,并除去第二光刻胶图案和第三光刻胶图案而形成;在电子元件的端部上形成的立柱部分,以具有预定尺寸的凸起;以及连接装置,用于立柱部分与横梁部分的一端连接,该横梁部分的所述端与在其上形成靠手的一端相对;其中在通过湿法蚀刻除去消耗性衬底时,在横梁的之字形部分的上表面上形成所述靠手。

根据本发明的另一个方面,提供一种用来检测电子装置的电接触元件,其包括:在其表面上用具有预定厚度的第一光刻胶形成的消耗性衬底;使第一光刻胶形成图案所限定的第一开口区,用于在其中形成尖端部分;用于使用第一光刻胶作为掩模在其中形成尖端部分的沟槽,该沟槽经过各向异性蚀刻过程使所述尖端部分圆滑,在消耗性衬底上形成的第一光刻胶图案通过灰化除去;之字形弯曲一次或多次的之字形横梁部分和靠手,其通过向消耗性衬底上由第二光刻胶图案定出的第二开口区中填充用于形成尖端和横梁部分的导电性材料到预定厚度并通过化学气相沉积、物理气相沉积或镀膜法、整平所得产品的上表面,并除去第二光刻胶图案和第三光刻胶图案而形成;在电子元件的端部上形成的立柱部分,以具有预定尺寸的凸起;以及连接装置,用于立柱部分与横梁部分的一端连接,该横梁部分的所述端与在其上形成靠手的一端相对;其中在通过湿法蚀刻除去消耗性衬底时,在之字形横梁部分的之字形部分上和电子元件表面上分别形成靠手,使得这些靠手相互间隔预定的距离。

根据本发明的另一个方面,在用之字形弯曲一次或多次的之字形部分形成横梁部分的情况下,所述靠手在之字形部分上的希望位置与电子元件表面上的相应位置之间形成。

根据本发明的另一个方面,在与尖端部分相对的横梁部分上形成所述靠手。

根据本发明的另一个方面,在横梁部分的之字形部分上的一点与电子元件表面上的相应位置之间形成所述靠手,所述一点最靠近尖端部分。

附图说明

在结合附图阅读以下详细描述后,本发明的上述目的和其他特征及优点将会变得更清楚,其中:

图1a和1b是说明用来检测电子装置的常规电接触元件的截面图和透视图;

图2-10b是解释根据本发明的第一实施方案制造用于检测电子装置的电接触元件的方法的截面图;

图11a是说明根据本发明的用来检测电子装置的电接触元件的横梁部分的平面图;

图11b是说明根据本发明的用来检测电子装置的电接触元件的另一种横梁部分的平面图;

图12-18b是解释根据本发明的第二实施方案制造用来检测电子装置的电接触元件的方法的截面图;

图19-25b是解释根据本发明的第三实施方案制造用来检测电子装置的电接触元件的方法的截面图;

图26是说明根据本发明的第一实施方案,通过制造用来检测电子装置的电接触元件的方法制造的第一电接触元件的透视图;

图27是说明根据本发明的第一实施方案,通过制造用来检测电子装置的电接触元件的方法制造的第二电接触元件的透视图;

图28是说明根据本发明的第一实施方案,通过制造用来检测电子装置的电接触元件的方法制造的第三电接触元件的透视图;

图29是说明根据本发明的第一实施方案,通过制造用来检测电子装置的电接触元件的方法制造的第四种电接触元件的透视图;

图30是说明根据本发明的第二实施方案,通过制造用来检测电子装置的电接触元件的方法制造的第五种电接触元件的透视图;

图31是说明根据本发明的第二实施方案,通过制造用来检测电子装置的电接触元件的方法制造的第六种电接触元件的透视图;

图32是说明根据本发明的第二实施方案,通过制造用来检测电子装置的电接触元件的方法制造的第七种电接触元件的透视图;

图33是说明根据本发明的第二实施方案,通过制造用来检测电子装置的电接触元件的方法制造的第八种电接触元件的透视图;

图34是举例说明根据本发明的用来检测电子装置的电接触元件的一种布置的平面图;

图35是举例说明根据本发明的用来检测电子装置的电接触元件的另一种布置的平面图;

图36是表示施加到用来检测电子装置的常规电接触元件的条形横梁部分的应力分布的图;

图37是表示施加到根据本发明的用来检测电子装置的电接触元件的之字形横梁部分的应力分布的图;

图38a和38b是说明根据本发明的第四实施方案的用来检测电子装置的电接触元件的截面图和透视图;

图39a和39b是说明根据本发明的第五实施方案的用来检测电子装置的电接触元件的截面图和透视图;

图40a和40b是说明根据本发明的第六实施方案的用来检测电子装置的电接触元件的截面图和透视图;

图41a-41f是说明图38a-40b中所示的电接触元件的横梁部分的横截面图;

图42a-42i是解释制造图38a和38b中所示的用来检测电子装置的电接触元件的方法的截面图;

图43a-43d是解释制造图39a和39b中所示的用来检测电子装置的电接触元件的方法的截面图;

图44a-44d是解释制造图40a和40b中所示的用来检测电子装置的电接触元件的方法的截面图;

图45a是表示通过模拟施加到根据本发明的用来检测电子装置的电接触元件的横梁部分上的应力分布所获得的结构的图;

图45b是表示通过模拟施加到用来检测电子装置的常规电接触元件的横梁部分上的应力分布所获得的结构的图。

具体实施方案

现在更详细描述本发明的优选实施方案,其一个实例在附图中说明。在可能的情况下,在全部图和说明书中使用相同的附图标记表示相同或类似的部分。

图2-10b是解释根据本发明的第一实施方案制造用来测试电子装置的电接触元件的方法的截面图。

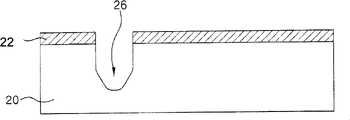

在根据本发明的这一实施方案的方法中,如图2所示,在用具有固定取向例如(100)的硅制造的消耗性衬底20的整个表面上形成具有预定厚度的第一保护膜22。第一层保护膜22包含诸如光刻胶的薄膜和氧化物膜。此时,通过旋涂法形成所述光刻胶,在旋涂法中,将光刻胶倾倒在消耗性衬底20上,同时旋转消耗性衬底20,氧化物膜通过常规热氧化法形成。

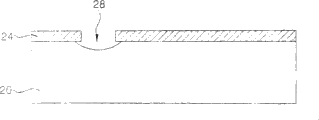

然后,如图3所示,通过进行本领域中熟知的光刻过程,形成具有第一开口区(未标记)的第一保护膜图案24。

此时,通过在第一保护膜22上涂敷光刻胶、曝光和显影其上已经实现电路图案的丝网(reticle),来形成包含光刻胶的第一保护膜图案24。此外,通过在第一保护膜22上涂敷光刻胶、通过曝光和显影所得产品来制备光刻胶图案、使用该光刻胶图案作为蚀刻掩模进行湿法或干法蚀刻来形成包含氧化物膜的第一保护膜图案24。

然后,如图4a所示,通过使用第一保护膜图案24作为蚀刻掩模进行第一蚀刻过程,在消耗性衬底20上形成将要在其中形成尖端部分的沟槽。

此时,第一蚀刻过程包括使用化学药品的湿法蚀刻过程,在所述化学药品中,以预定比例混合氢氧化钾(KOH)和去离子水。当采用化学药品进行湿法蚀刻时,将具有固定取向的消耗性衬底20各向异性蚀刻,以形成具有截头多边形棱柱形或截头圆锥形构形的沟槽26。

此外,如图4b所示,第一蚀刻过程可以包含采用化学药品的湿法蚀刻过程,在该化学药品中,氢氟酸(HF)、硝酸(HNO3)和醋酸(CH3COOH)以预定比例混合。通过采用化学药品进行的湿法蚀刻过程,将具有诸如(100)的固定取向的消耗性衬底20各向同性蚀刻,以形成具有柱形例如方柱构形且底面圆滑的沟槽28。

此时,由于化学药品的各向同性蚀刻特性,消耗性衬底在第一开口区的上端和在第一保护膜图案24之下也被蚀刻。

然后,如图5a所示,在消耗性衬底20上施加的第一保护膜图案24用作蚀刻掩模,其通过第一各向异性蚀刻过程形成的侧面倾斜的具有截头多边形棱柱形或截头圆锥形构形的沟槽26限定。在这种状态下,采用SF6、C4F8和O2气体以预定比例混合的气体混合物实施第二蚀刻过程。

此时,第二蚀刻过程是一种深槽蚀刻,通过所谓Bosh法的反应性离子蚀刻(RIE)来实施。通过进行第二蚀刻过程,由第一蚀刻过程形成的、并且具有截头多边形棱柱形或截头圆锥形构形的沟槽26的深度增大到30μm~500μm,同时沟槽26的底面变得圆滑。

进一步详细地描述,在通过SF6的各向同性蚀刻特性进一步蚀刻沟槽26具有30μm~500μm的深度后,具有截头多边棱柱形或截头圆锥形构形的沟槽26的内表面的角度减小到预定的程度,并且沟槽26的底部表面变得圆滑。

这里,应注意的是,第二蚀刻过程可以进行一次或多次。

同时,如图5b所示,使用施加到消耗性衬底20上的第一保护膜图案24作为蚀刻掩模,该图案用第一蚀刻过程形成的具有圆滑内表面的柱形构形的沟槽28限定。在这种状态下,采用SF6、C4F8和O2气体以预定比例混合的气体混合物进行第二蚀刻过程。

此时,第二蚀刻过程是一种深槽蚀刻,通过所谓Bosh法的RIE来进行。通过进行第二蚀刻过程,第一蚀刻过程所确定的沟槽深度增加至30μm~500μm。因此,沟槽28得以进一步加深,其底表面变得圆滑。

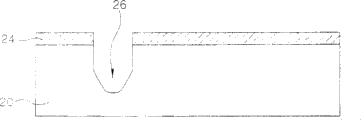

这里,应注意的是,第二蚀刻过程可以进行一次或多次。接着,如图6a所示,除去第一保护膜图案24之后,通过第二蚀刻过程在具有截头多边棱柱形或截头圆锥形构形、且底面圆滑的沟槽26所限定的消耗性衬底20的整个表面上形成第二保护膜图案30,该图案包含具有预定厚度的光刻胶并限定第二开口区(未编号)。作为替代的方案,如图6b所示,除去第一保护膜图案24之后,通过第二蚀刻过程在具有柱形构形且底面圆滑的沟槽28所限定的消耗性衬底20的整个表面上形成第二保护膜图案31,该图案包含具有预定厚度的光刻胶并限定第二开口区(未编号)。

此时,通过涂敷光刻胶、曝光和显影形成第二保护膜图案30。第二保护膜图案30和31的形成能够在消耗性衬底上限定出第二开口区,从而使横梁部分在第二开口区中形成,使第二开口区分别和沟槽26和28相通。

随后,如图7a所示,在消耗性衬底20上形成第二保护膜图案30之后,通过进行CVD、PVD或镀膜过程将导电物质32填充到第二开口区中,为了具有预定的厚度,整平所得产品的上表面。作为替代的方案,如图7b所示,在形成第二保护膜图案的消耗性衬底20上通过CVD、PVD或镀膜法形成具有预定厚度的导电材料34后,整平所得产品的上表面。

此时,导电材料由镍合金等制成,可以通过化学机械磨光、腐蚀法和研磨等方法将已经形成到材料的消耗性衬底20的上表面整平。

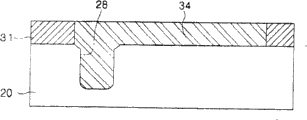

接着,如图8a所示,在第二保护膜图案30(参见图7a)从经过整平步骤的消耗性衬底20上表面除去时,在沟槽26中形成尖端部分,在第二开口区中形成横梁部分36。作为替代的方案,如图8b所示,随着第二保护膜图案31(参见图7b)从经过整平步骤的消耗性衬底20上表面的除去,在沟槽28中形成尖端部分,在第二开口区中形成横梁部分38。

此时,通过使用化学药品进行湿法蚀刻或进行诸如灰化之类的干法蚀刻,除去第二保护膜图案31(参见图7b)。

为了完全符合最近的发展趋势,即在高度集成的半导体器件中间距变小的趋势,如图11a中所示,横梁部分36和38的每一个都具有多阶梯构形,该构形包括与沟槽26和28中形成的尖端部分的每一个相连的第一条形部分40;与第一部分40相连且宽度大于第一部分40的第二条形部分42;以及与第二部分42相连且宽度大于第二部分42的第三条形部分44。

另外,如图11b所示,横梁36和38的每一个可以具有之字形构形,该构形包括与沟槽26和28中形成的尖端部分相连的第一条形部分46;与第一部分46相连且之字形弯曲一次或多次的第二之字形部分48;以及第三条形部分50。

此时,第三部分40、50可以与沟槽26、28中形成的各个尖端部分相连。同样,之字形横梁部分38的第二之字形部分48的弯曲角度为30°~170°,优选约90°。应注意的是,第二部分48可以之字形弯曲一次或多次。在横梁36和38的每一个中,从凸起位置至尖端部分位置,宽度减小,因此容易符合最近的趋势,即在高度集成的半导体器件中间距变小的趋势。

接着,如图9a所示,在由具有截头多边棱柱形或截头圆锥形构形、且底面圆滑的沟槽26所限定的消耗性衬底20上形成的横梁部分36通过凸起62的媒介与电子元件60相连,该电子元件上具有电路图案。作为替代的方案,如图9b所示,在由具有柱形构形且底面圆滑的沟槽28所限定的消耗性衬底20上形成的横梁部分38通过凸起66的媒介与电子元件64相连,该电子元件上具有电路图案。

此时,消耗性衬底20上形成的横梁部分36、38分别和电子元件60、64相互连接,其连接方式使得凸起62、66置于横梁36、38和电子元件60、64之间后,通过焊接、钎焊、镀膜、导电粘合剂等使凸起62、66和横梁部分36、38相连接。

最后,如图10a所示,在由具有截头多边棱柱或截头圆锥形构形、且底面圆滑的沟槽26所限定的消耗性衬底20通过湿法蚀刻等方法除去后,可以使横梁部分36得以自由,从而完成用于测试电子装置的电接触元件35。作为替代的方案,如图10b所示,在由具有柱形构形、且圆滑底面的沟槽28所限定的消耗性衬底20通过湿法蚀刻等方法除去后,使横梁部分38得以游离,从而完成用于测试电子装置的电接触元件39。

随后,将详细描述根据本发明的第一实施方案的测试电子装置的电接触元件的生产方法生产的电接触元件,以及电接触元件的横梁部分和尖端部分。

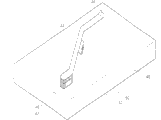

图26是说明根据本发明的第一实施方案的制造用来检测电子装置的电接触元件的方法制造的第一电接触元件的透视图。

在根据本发明的用于测试电子装置的第一电接触元件中,如图26所示,电子元件100的末端(未编号)通过凸起媒介102且通过连接部分104与电接触元件106横梁部分的第三部分108相连,电子元件100例如是其上具有预定电路图案的印制板电路(PCB)。

此时,电接触元件106具有的横梁部分具备多阶梯构形,该构形包括第一条形部分112;和第一部分112相连、宽度大于第一部分112的第二条形部分110;以及和第二部分110相连、宽度大于第二部分110的第三条形部分108。

横梁部分的第一部分112自由端整体和尖端部分114相连接,该尖端部分通过恒定的物理作用力和半导体芯片基座相接触。

这里,尖端部分114具有截头四棱柱构形,并具有圆滑末端表面。从OD特性上说,尖端部分114的长度延长到30μm~500μm。在该优选实施方案中,尖端部分长度为100μm。

因此,由于电接触元件106的尖端部分114具有四棱柱构形,并具有圆滑末端表面,当尖端部分114反复与半导体芯片的基座相接触时,可以防止尖端部分114磨损,防止其自身产生颗粒。

同时,由于尖端部分114的末端表面是圆滑的,当电接触元件106的尖端部分114通过恒定的物理作用力反复与半导体芯片的基座相接触时,可以防止尖端部分114刺穿基座上形成的氧化膜,防止损坏基座,从而可以防止在进行诸如引线焊接过程等后续半导体制造过程时缺陷比例增加。

另外,由于尖端部分114的末端表面是圆滑的,尖端部分114和半导体芯片基座之间的接触面积增加,可以改善导电性。

并且,由于尖端部分114的长度为30μm~500μm,在该优选的实施方案中为100μm,因此易于调整OD特性。

此外,由于电接触元件106的横梁部分具有多阶梯的构形,因此可以符合最近的趋势,即在高度集成的半导体器件中间距变小的趋势,其中的多阶梯构形包括和尖端部分114相连的第一条形部分112;和第一部分112相连、宽度大于第一部分112的第二条形部分110;以及和第二部分110相连、宽度大于第二部分110的第三条形部分108。

也就是说,如图34所示,从第三部分108至第一部分112,横梁部分的宽度减小,因此许多电接触元件106可以放射性地彼此邻接,与半导体装置的基座300相接触。这种方式符合最近的趋势,即在高度集成的半导体器件中间距变小的趋势。

图27是说明根据本发明的第一实施方案,通过制造用来检测电子装置的电接触元件的方法制造的第二电接触元件的透视图。

如图27所示,本发明的第二电接触元件115特征在于:第一电接触元件106的尖端部分114替换为尖端部分116,该尖端部分在其近端形成凸出部分118近端和具有柱形构形并具有圆滑末端表面的末端。

这里,从OD特性上说,尖端部分116的长度延长到30μm~500μm。在该优选实施方案中,尖端部分116长度为100μm。

由于在第二电接触元件115的尖端部分116的近端附近形成凸出部分118,因此除了由第一电接触元件106获得的工作效应外,当尖端部分116通过恒定的物理作用力和半导体芯片基座相接触时,可以将施加在尖端部分116近端的应力分散,防止尖端部分116断裂。

图28是说明根据本发明的第一实施方案,通过制造用来检测电子装置的电接触元件的方法制造的第三电接触元件的透视图。

在本发明的第三电接触元件120中,第一电接触元件106的横梁部分替换为具有之字形构形的横梁部分。换句话说,如图28所示,该横梁部分具有第一条形部分122;与第一部分122相连的之字形第二部分124;以及与第二部分124相连的第三条形部分126。

此时,横梁部分的第二之字形部分124的弯曲角度为30°~170°,优选约90°。应注意的是,第二部分48可以之字形弯曲一次或多次。

在之字形的横梁部分中,由于从凸起102的位置至尖端部分114,宽度减小,因此可以用这种方式生产横梁部分,从而容易符合最近的趋势,即在高度集成的半导体器件中间距变小的趋势。

结果,由于第三电接触元件120的横梁部分具有之字形构形,因此除了第一电接触元件106所获得的工作效应外,当尖端部分114通过恒定的物理作用力和半导体芯片基座相接触时,由于从凸起102至尖端部分114之间横梁部分的长度增加,可以将施加在横梁上的应力分散,从而防止横梁部分由于应力集中施加而断裂。

图36是表示模拟施加到用来检测电子装置的常规电接触元件的条形横梁部分的应力分布的图;图37是表示模拟施加到根据本发明的用来检测电子装置的电接触元件的之字形横梁部分的应力分布的图;

参照图36和37,对于常规条形横梁部分来说,在横梁上距离凸起约0.4mm的位置上施加达到500×106Pa的危险应力。对于本发明的之字形横梁部分来说,可以确证应力均匀地分布在横梁部分的整个区域上。

另外,从图35中可以容易地看出,由于具有之字形构形的横梁部分的第三电接触元件从凸起102位置至尖端部分114的位置的宽度减小,可以容易地符合最近的趋势,即在高度集成的半导体器件中间距变小的趋势。

也就是说,因为从第一部分122至第三部分126,横梁部分的宽度减小,如图35所示,多个电接触元件120可以相互放射性地邻接排列,以便与半导体装置的基座302接触。用这种方式可以符合最近的趋势,即高度集成的电子装置中间距变小的趋势。

图29是说明根据本发明的第一实施方案,通过制造用来检测电子装置的电接触元件的方法制造的第四种电接触元件的透视图。

本发明第四种电接触元件121特征在于:第一电接触元件106的横梁部分替换为具有之字形构形的横梁部分,该横梁部分具有第一条形部分122、与第一部分相连的第二第二之字形部分124以及与第二部分124相连的第三条形部分126。第四种电接触元件121特征还在于:第三部分126上提供有尖端部分116,该尖端部分具有周围形成凸出部分118的近端,以及具有柱形构形并具有圆滑末端表面的末端。

因此,第四种电接触元件121可以同时实现由第二电接触元件115的尖端部分116所获得的工作效应,和第三电接触元件120的横梁部分所获得的工作效应。

下文将详细描述根据本发明的第二实施方案生产测试电子装置的电接触元件的方法。

图12至18b是截面图,这些图用于解释根据本发明的第二实施方案生产测试电子装置的电接触元件的方法。

在本发明该实施方案的方法中,首先,如图12所示,在由固定取向的硅(100)制成的消耗性衬底60的整个表面上形成具有预定厚度的第一保护膜。第一保护膜包括诸如光刻胶之类的薄膜和氧化膜。通过进行与上述第一实施方案相同的光刻过程,限定了第二开口区(未编号)比第一实施方案中的第一开口区大的第一保护膜图案62。

然后,通过使用第一保护膜图案62作为蚀刻掩模实施第一蚀刻过程。对消耗性衬底60进行各向异性蚀刻,以限定沟槽64,该沟槽具有截头多边棱柱构形,或具有截头圆锥构形。沟槽64的侧面倾斜有预定的角度。

此时,对消耗性衬底60进行各向同性蚀刻的第一蚀刻过程包括采用包含氢氧化钾(KOH)等的化学药品进行的湿法蚀刻过程。

然后,如图13所示,除去第一层保护膜图案62之后,在消耗性衬底60的整个表面上形成具有预定厚度的第二层保护膜,该膜包括诸如光刻胶之类的薄膜、氧化膜等。在该膜上,通过进行与形成第一保护膜图案62情况相同的光刻过程,形成第二保护膜图案66,从而使沟槽64的两侧端封闭,只有沟槽64的中央部分是开放的。

随后,如图14a所示,通过采用第二保护膜图案66作为蚀刻掩模进行第二蚀刻过程,进一步加深沟槽64。

此时,第二蚀刻过程包括采用化学药品进行湿法蚀刻,化学药品中氢氧化钾(KOH)和去离子水以预定的比例相混合。当采用化学药品实施湿法蚀刻时,沟槽64得以各向异性地蚀刻,以确定沟槽68,该沟槽具有截头多边棱柱形或截头圆锥形构形,因而沟槽68进一步加深。

另外,如图14b所示,第二蚀刻过程包括采用化学药品进行的湿法蚀刻过程,该化学药品中氟化氢(HF)、硝酸(HNO3)和醋酸(CH3COOH)以预定的比例混合。通过采用化学药品实施湿法蚀刻,沟槽64得以各向同性地蚀刻,以确定沟槽70,该沟槽具有柱形构形,并具有圆滑的底面。

此时,在第二开口区的上端和第二保护膜图案66的下方附近对消耗性衬底60进行各向同性蚀刻。

然后,如图15a所示,使用涂敷在消耗性衬底60上的第二保护膜图案66作为蚀刻掩模,其中通过第二蚀刻过程用具有截头棱柱形构形的沟槽68限定该图案。这种状态下,再次进行第三蚀刻过程。

此时,第三蚀刻过程包括与本领域公知的第一实施方案相同的RIE过程。通过进行第三蚀刻过程,进一步增加了由第二蚀刻过程所形成的沟槽68的深度。应注意的是,第三蚀刻过程可以进行一次或多次。

具体地,以与第一实施方案相同的方式,使具有截头多边棱柱形构形或截头圆锥构形的沟槽底面变得圆滑。

同时,如图15b所示,使用涂敷在消耗性衬底60上的第二保护膜图案66作为蚀刻掩模,其中通过第二蚀刻过程用具有截头圆锥构形、且底面圆滑的沟槽70限定该图案。这种状态下,再次进行第三蚀刻过程。

此时,第三蚀刻过程包括与本领域公知的第一实施方案相同的RIE过程。通过进行第三蚀刻过程,进一步增加了由第二蚀刻过程所形成的沟槽70的深度,从而限定在其近端具有凹陷的柱形沟槽70。

这里,应注意的是,第三蚀刻过程可以进行一次或多次。

接着,如图16a所示,除去第二保护膜图案66(参见图15a)之后,通过第三蚀刻过程在沟槽68所限定的消耗性衬底60的整个表面上形成第三保护膜图案72,该图案包含预定厚度的光刻胶,并限定出第三开口区(未编号),其中的沟槽具有截头多边棱柱形或截头圆锥形构形,且底面圆滑。作为替代的方案,如图16b所示,除去第二保护膜图案66(参见图15b)之后,通过第三蚀刻过程在沟槽70所限定的消耗性衬底60的整个表面上形成第三保护膜图案72,该图案包含预定厚度的光刻胶,并限定出第三开口区(未编号),其中的沟槽70具有近端凹陷的柱形构形。

此时,可以通过形成第二保护膜图案66时所用的相同方法形成第三保护膜图案72。第三保护膜图案72的形成能够在消耗性衬底60上限定出第三开口区,从而使横梁部分在第三开口区中形成,且第三开口区分别和沟槽68、70相通。

随后,如图17a所示,通过进行CVD、PVD或镀膜过程,将导电材料73以预定厚度的量填充到第三保护膜图案在消耗性衬底60上所限定的第三开口区之后,整平所得产品的上表面。作为替代的方案,如图17b所示,通过进行CVD、PVD或镀膜过程,将导电材料74以预定厚度的量填充到第三保护膜图案72在消耗性衬底60上所限定的第三开口区之后,整平所得产品的上表面。

此时,导电材料73和74由镍合金等制成,可以通过CMP、深腐蚀(etchback)和研磨等方法将导电材料73和74所得产品的上表面整平。

接着,如图18a所示,随着第三保护膜图案72从经过整平步骤的消耗性衬底60上表面的除去,形成横梁部分76的方式使其与尖端部分相连。作为替代的方案,如图18b所示,在第三保护膜图案72从经过整平步骤的消耗性衬底60上表面除去时,形成横梁部分78并使其和尖端部分相连。

此时,通过采用化学药品进行湿法蚀刻过程和诸如灰化等的干法蚀刻过程除去第三保护膜图案。

以和第一实施方案相同的方式,横梁部分76和78的每一个都具有多阶梯构型,该构形包括与沟槽68和70中形成的各个尖端部分相连的第一条形部分、宽度大于第一部分的第二条形部分以及宽度大于第二部分的第三条形部分。可选地,横梁部分76和78的每一个都具有之字形构形,该构形包括与沟槽68和70中形成的各个尖端部分相连的第一条形部分、第二之字形部分以及第三条形部分。

同样,与第一实施方案一样,进行一个过程,借助凸起媒介并通过连接,使消耗性衬底60上形成的横梁部分76、78与其上具有所需电路图案的电子元件相连。然后,通过湿法蚀刻等方法除去消耗性衬底60,用于测试电子装置的电接触元件即得以完成。

下文中,将详细描述根据本发明的第二实施方案的用来测试电子装置的电接触元件的生产方法生产的电接触元件。

图30是说明根据本发明的第二实施方案通过制造用来检测电子装置的电接触元件的方法制造的第五电接触元件的透视图。

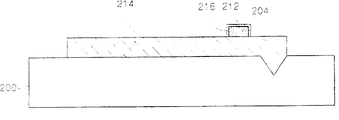

在本发明用来测试电子装置的第五个电接触元件206中,用与第一电接触元件106的相同方法,如图30所示,电子元件200的末端(未编号)通过凸起媒介202且借助连接部分204与电接触元件206相连,电子元件100例如是其上具有预定电路图案的印制板电路(PCB)。

此时,电接触元件206具有多阶梯构形的横梁部分,该构形包括第一条形部分212;与第一部分212相连、宽度大于第一部分的第二条形部分210;以及与第二部分210相连、宽度大于第二部分210的第三条形部分208。

具体地,从图30可以容易地看出,本发明中第五种电接触元件206特征在于:尖端部分215整体提供在横梁部分的第三条形部分的自由端,通过恒定的物理作用力和半导体芯片基座相接触,尖端部分215具有附近形成凸出部分214的近端,和具有四棱柱形构形并具有圆滑末端表面的末端。

此时,由于OD特性,尖端部分212的长度延长到30μm~500μm。在该优选实施方案中,尖端部分长度为100um。

因此,除了由第一电接触元件获得的工作效应外,在第五种电接触元件206中,当电接触元件206通过恒定的物理作用力和半导体芯片的基座相接触时,由于凸出部分(projection)214的存在,有可能将施加到尖端部分215近端的应力分散,以防尖端部分215断裂。

图31是说明根据本发明的第二实施方案,通过制造用来检测电子装置的电接触元件的方法制造的第六种电接触元件的透视图。

本发明的第六种电接触元件特征是:上述的第五种电接触元件206的尖端部分215替换为尖端部分216,其中第一凸出部分在近端周围形成,与第一凸出部分220相连、截面面积比第一凸出部分220小的第二凸出部分在尖端部分216的中间部分形成,与第二凸出部分218相连、截面面积小于第二凸出部分218的末端具有柱形构形,其末端表面圆滑。

因此,在第六种电接触元件207中,由于第一凸出部分220和第二凸出部分218的存在,当电接触元件207通过恒定的物理作用力与半导体芯片基座相接触时,有可能更有效地将施加到尖端部分216近端的应力分散,以防尖端部分216断裂。

图32是说明根据本发明的第二实施方案,通过制造用来检测电子装置的电接触元件的方法制造的第七种电接触元件的透视图。

本发明的第七种电接触元件230特征是:上述的第五种电接触元件206的横梁部分替换为呈之字形构形的横梁部分,其具有第一条形部分232、和第一部分232相连的第二之字形部分234以及和第二部分234相连的第三条形部分236。

因此,由于形成的第七种电接触元件230具有之字形构形,除了由第一电接触元件获得的工作效应外,当尖端部分通过恒定的物理作用力与半导体芯片基座相接触时,有可能将施加到横梁部分的应力分散,以防尖端部分断裂。

图33是说明根据本发明的第二实施方案,通过制造用来检测电子装置的电接触元件的方法制造的第八种电接触元件的透视图。

本发明的第七种电接触元件230特征是:上述的第五种电接触元件206的横梁部分替换为呈之字构形的横梁部分,其具有第一条形部分232、与第一部分232相连的第二之字形部分234以及与第二部分234相连的第三条形部分236,并且上述的第五种电接触元件206的尖端部分215替换为尖端部分216,其中第一凸出部分在近端周围形成,与第一凸出部分220相连、截面面积比第一凸出部分220小的第二凸出部分在尖端部分216的中间部分形成,与第二凸出部分218相连、截面面积小于第二凸出部分218的末端具有柱形构形,且其末端表面圆滑。

因此,通过第八种电接触元件231,有可能同时实现由第六种电接触元件207的尖端部分216的工作效应和第七种电接触元件234的横梁部分的工作效应。

图19至25b是截面图,这些图解释了根据本发明的第三实施方案生产用于测试电子装置的电接触元件的方法。

在本发明第三实施方案的方法中,首先如图19所示,具有预定厚度的第一保护膜在消耗性衬底80的整个表面上形成,其中消耗性衬底80由具有诸如(100)的固定取向的硅制成。第一保护膜包含诸如光刻胶的薄膜和氧化膜。通过进行与上述第一实施方案中的相同光刻过程,形成了第一保护膜图案82,该保护膜图案具有比第一实施方案中第一开口区更大的第二开口区(未编号)。

然后,通过用第一保护膜图案82作为蚀刻掩模进行第一蚀刻过程,将消耗性衬底80各向同性地进行蚀刻,形成具有四方孔构形的沟槽84,尖端部分将在该沟槽中形成。

此时,第一蚀刻过程包括采用化学药品进行湿法蚀刻,化学药品中氟化氢(HF)、硝酸(HNO3)和醋酸(CH3COOH)以预定的比例混合。

然后,如图20所示,除去第一保护膜图案后,在消耗性衬底80的整个表面上形成具有预定厚度的第二保护膜,该膜包含诸如光刻胶的薄膜、氧化膜,等等。通过进行与形成第一保护膜图案82时所用的相同光刻过程,形成第二保护膜图案86,使沟槽84的两侧端部分闭合,只有沟槽84的中央部分是开放的。

其后,如图21a所示,通过用第二保护膜图案86作为蚀刻掩模进行第二蚀刻过程,使沟槽84进一步加深。

此时,第二蚀刻过程包括采用化学药品进行湿法蚀刻,化学药品中氢氧化钾(KOH)和去离子水以预定的比例混合。通过采用该化学药品进行湿法蚀刻过程,对沟槽84进行各向异性蚀刻,以确定沟槽88,其具有截头多边棱柱形或截头圆锥形,从而使沟槽84更深。

另外,如图21b所示,第一蚀刻过程包括采用化学药品进行湿法蚀刻,化学药品中氟化氢(HF)、硝酸(HNO3)和醋酸(CH3COOH)以预定的比例混合。通过采用该化学药品进行湿法蚀刻过程,对沟槽84进行各向同性的蚀刻,以确定沟槽90,它具有柱状构形,该柱状构形近端凹陷,而底面变得圆滑。

此时,在第二开口区的上端附近,在第二保护膜图案的下方对消耗性衬底进行各向同性蚀刻。

然后,如图22a所示,使用涂敷在消耗性衬底80上的第二保护膜图案86作为蚀刻掩模,其中通过第二蚀刻过程、用具有截头棱柱形构形的沟槽88限定该图案。这种状态下,再次实施第三蚀刻过程。

此时,第三蚀刻过程包括本领域熟知的、第一实施方案中所用的相同RIE法。通过进行第三蚀刻过程,进一步增加了由第二蚀刻过程限定的沟槽88的深度,并且沟槽88的底面变得圆滑。

这里,应注意的是,第三时刻过程可以进行一次或多次。

同样,如图22b所示,使用涂敷在消耗性衬底上的第二保护膜图案86作为蚀刻掩模,其中通过第二蚀刻过程、用具有截头棱柱形构形的沟槽90限定该图案。这种状态下,再次进行第三蚀刻过程。

此时,第三蚀刻过程包括本领域熟知的、第一实施方案中所用的相同RIE法。通过实施第三蚀刻过程,进一步增加了由第二蚀刻过程限定的沟槽90的深度,从而形成了近端凹陷的柱状沟槽90。应注意的是,第三蚀刻过程可以进行一次或多次。

接着,如图23a所示,除去第一保护膜图案86后,在消耗性衬底80的整个表面上形成具有预定厚度的第二保护膜图案92,它包括具有预定厚度的光刻胶并限定了第三开口区(未编号),其中消耗性衬底80用具有截头多边棱柱形构形或截头圆锥形构形的沟槽88进行限定。作为替代的方案,如图23b所示,除去第二保护膜图案86后,包含预定厚度光刻胶并限定了第三开口区(未编号)的第三保护膜图案92在消耗性衬底80的整个表面形成,其中消耗性衬底80用近端凹陷之柱状构形的沟槽90加以限定。

此时,形成第三保护膜图案,在消耗性衬底80上限定第三开口区,使在第三开口区中形成横梁部分,使第三开口区分别与沟槽88和90相通。

随后,如图24a所示,通过实施CVD、PVD或镀膜过程后,往第三保护膜图案92在消耗性衬底80上限定的第三开口区中,以预定厚度的量填充导电材料93后,整平所得产品的上表面。作为替代的方案,如图24b所示,通过进行CVD、PVD或镀膜过程,往第三保护膜图案92在消耗性衬底80上限定的第三开口区中,以预定厚度的量填充导电材料94后,整平所得产品的上表面

此时,导电材料93和94由镍合金等制成,可以通过CMP、深腐蚀和研磨等方法将由导电材料93和94形成的所得产品上表面整平。

接着,如图25a所示,从经过整平过程的消耗性衬底80上表面除去第三保护膜图案92时,形成横梁部分96,使得它与尖端部分相连接,该尖端部分已经在其近端附近连续形成了两个凸出部分。作为替代的方案,如图25b所示,从经过整平过程的消耗性衬底80上表面除去第三保护膜图案92之后,横梁部分98形成,使得它与具有两个凸出部分的尖端部分相连接。

此时,通过采用化学药品进行湿法蚀刻过程和诸如灰化等的干法蚀刻过程除去第三保护膜图案。

通过和第一实施方案相同的方式,横梁部分96和98各自具有多个层次(multi-step)的构形,该构形包括与沟槽88及90中形成的各个尖端部分相连接的第一条形部分、宽度比第一部分大的第二条形部分和宽度比第二部分大的第三条形部分。作为替代的方案,横梁部分96和98各自具有之字形构形,该构形包括与沟槽88及90中形成的各个尖端部分相连接的第一条形部分、第二之字形部分和第三条形部分。

同样,与上述第一实施方案一样,进行一个过程,来通过凸起媒介(medium of abump)并通过结合使消耗性衬底80上形成的横梁部分96及98与其上已实现所需电路图案的电子元件相联接。然后,通过湿法蚀刻等除去消耗性衬底80,即完成用于测试电子装置的电接触元件。

图38a和38b分别是说明根据本发明的第四实施方案的用来检测电子装置的电接触元件的截面图和透视图。

在根据本发明该实施方案的电接触元件中,如图38a和38b所示,其上已实现预定电路图案的、诸如PCB之类的电子元件20的末端,与包含预先确定大小之凸起的立柱部分相互连接。通过焊接、钎焊、镀膜、导电粘合剂等,使在其一端形成的具有尖端部分26的横梁部分24与立柱部分22相连接。

此时,横梁部分24具有之字形构形,该构形具有至少一个之字型部分。在横梁部分24的之字形部分的表面上提供本发明的靠手30,该表面离尖端部分26最远,从而使靠手30在水平方向上靠近尖端部分26。

另外,为了防止由于靠手30和电子元件20之间相接触而产生静电,在靠手30的外表面上进一步施加由聚酰亚胺、聚对亚苯基二甲基等制成的绝缘包覆层34。

在下文中,本发明中用来测试电子元件的电接触元件的横梁部分将参考图41(a)至图41(f)详细地描述。

如图41(a)所示,本发明中电接触元件的横梁部分24具有之字形构形,其中具有预定长度的第一条形部分100、第二部分102和第三部分104以预定角度弯曲,形成两个弯曲段。

此时,在靠近弯曲点的第二部分102和第三部分103之间的横梁部分表面提供一个靠手106,在第三部分104的自由端形成尖端部分108。

另外,如图41(b)至41(f)所示,本发明中电接触元件的横梁部分24具有之字形构形,其中条形的第一部分110、120、130、140和150;第二部分112、122、132、142和152;第三部分114、124、134、144和154;和第四个部分116、126、136、146和156以预定的角度弯曲形成三个弯曲段。

此时,在靠近弯曲点的第二部分112、122、132、142和152与第三部分114、124、134、144和154之间的横梁部分表面提供靠手118、128、138、148和158。在第四个部分116、126、136、146和156的自由端形成尖端部分119、129、139、149和159。

此时,从图41(f)中显然可以看出,由于横梁部分24从立柱部分到尖端部分159其宽度减小,因此可能有效地符合最近的发展趋势,即在高度集成的半导体器件中间距变小的趋势。

也就是说,因为横梁部分从第三部分到第四个部分其宽度减小,所形成的具有尖端部分的多个横梁部分24可以发射性相互靠近邻接,与半导体装置的基座相接触。通过这种方式,可以符合最近的发展趋势,即在高度集成的半导体器件中间距变小的趋势。

结果,电接触元件的尖端部分26通过恒定的物理作用力和半导体芯片基座相接触,在具有所需OD特性的同时,向半导体芯片施加一个恒定的电信号,从而确认半导体芯片正常与否。

此时,通过物理作用力使横梁部分24弯曲,从而使尖端部分26与半导体芯片基座相接触,横梁部分24表面上形成的靠手30与电子元件20相接触。

另外,当尖端部分26和半导体芯片基座相互接触时,由于横梁部分24具有之字形弯曲一次或多次的构形,在横梁部分的一个表面提供靠手30,因此发生扭转现象。由于这种扭转现象,尖端部分26施加到半导体芯片上的压力可以加倍,从而保证尖端部分26可靠地通过氧化膜和半导体基座相接触。

图39a和39b分别是说明根据本发明的第五实施方案的用来测试电子装置的电接触元件的截面图和透视图。

从图39a和39b可以容易地出,以和第四个实施方案相同的方式构造本发明该实施方案中的电子接触元件,不同之处是在电子元件40上与靠近尖端部分46的横梁部分44的弯曲部分相对应的位置上提供靠手50。

此时,为了防止由于靠手50和横梁部分44之间的接触而产生静电,在靠手50的外表面上进一步施加一个由聚酰亚胺、聚对二甲苯等制成的绝缘包覆层52。

结果,电接触元件的尖端部分46通过恒定的物理作用力与半导体芯片基座相接触,在具有所需OD特性的同时,向半导体芯片施加一个恒定的电信号,从而确认半导体芯片正常与否。

此时,通过物理作用力使横梁部分44弯曲,从而使尖端部分46和半导体芯片基座接触,使电子元件40上形成的靠手50与横梁部分44的一个表面接触。

另外,当尖端部分46和半导体芯片基座相互接触时,由于横梁部分44具有之字形弯曲一次或多次的构形并且在电子元件上提供靠手50,因此发生扭转现象。由于这种扭转现象,尖端部分46施加到半导体芯片上的压力可以加倍,从而保证尖端部分46可靠地通过氧化膜与半导体基座相接触。

图40a和40b分别是说明根据本发明的第六实施方案的制造用来检测电子装置的电接触元件的截面图和透视图。

从图40a和40b可以看出,以和第四个实施方案相同的方式构造本发明该实施方案中用来测试电子装置的电子接触元件,不同之处是一对靠手70和74一个水平靠近尖端部分26在横梁部分64的之字形部分表面上,该表面在垂直方向上离尖端部分66最远,另一个在电子元件40上与水平靠近尖端部分46的横梁部分的弯曲部分相对应的位置上。

此时,分别位于横梁部分64和电子元件60上的靠手对70和74彼此间有间隔,取决于横梁部分64的弯曲程度。为了防止由于靠手70和74之间相接触而产生静电,在靠手70和74的外表面上进一步施加由聚酰亚胺、聚对二甲苯等制成的绝缘包覆层72和76。

结果,电接触元件的尖端部分66通过恒定的物理作用力和半导体芯片基座相接触,在具有所需OD特性的同时,向半导体芯片提供一个恒定的电信号,从而确认半导体芯片正常与否。

此时,通过物理作用力使横梁部分64弯曲,通过这种方式,尖端部分66和半导体芯片基座相接触,横梁部分64表面上的靠手对70和74与电子元件60相接触。

另外,当尖端部分66和半导体芯片基座相互接触时,由于横梁部分64具有之字形弯曲一次或多次的构形,在横梁部分的表面上和电子元件上提供靠手70和74,因此发生扭转现象。由于这种扭转现象,尖端部分66施加到半导体芯片上的压力可以加倍,从而保证尖端部分66可靠地通过氧化膜与半导体基座相接触。

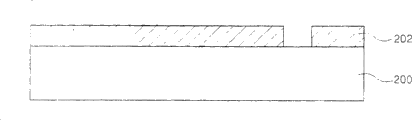

图42a至42i是截面图,该图解释了图38a和38b中所示的、用来测试电子装置的电接触元件的生产方法。

在本发明该实施方案的方法中,首先,如图42a所示,在由硅制成的消耗性衬底200的整个表面上形成预定厚度的第一保护膜。第一保护膜可以包含诸如光刻胶等的薄膜。然后,通过使第一保护膜图案化,形成第一保护膜图案202,使第一保护膜图案202能够限定出第一开口区,尖端部分在该开口区中形成。

此时,在旋转消耗性衬底200的同时,通过涂敷光刻胶、曝光和使光刻胶等显影,在消耗性衬底上形成包含光刻胶等的第一保护膜图案202。

然后,如图42b所示,通过使用第一保护膜图案202作为蚀刻掩模进行蚀刻过程,在消耗性衬底200上限定沟槽204,后续过程中该沟槽中形成尖端部分。

此时,限定沟槽204的蚀刻过程包括采用化学药品进行湿法蚀刻,或者采用反应气体进行干法蚀刻。在限定沟槽204后,通过在沟槽中进行一次或多次各向异性蚀刻,增加沟槽204的深度,从而使沟槽204具有截头多边棱柱形或截头圆锥形构形,其中具有倾斜的侧面。同样,通过使沟槽204的内表面变得圆滑和在沟槽中进行一次或多次各向异性蚀刻,形成圆滑的尖端部分218。

接着,如图42c所示,在通过灰化等去除第一保护膜图案202后,形成第二保护膜图案206以限定第二开口区域,在第二开口区域中形成之字形弯曲一次或多次并具有至少一个弯曲部分的横梁部分,并且第二开口区域与构槽204相通。

此时,以与第一保护膜图案202相同的方式,通过连续地进行涂敷光刻胶、曝光和显影来形成第二保护膜图案206。

然后,如图42d所示,在消耗性衬底200上形成第二保护膜图案之后,通过进行CVD、PVD或镀膜过程,在第二保护膜图案206的第二开口区中形成预定厚度的导电材料208,通过这种方式形成横梁部分和尖端部分。随后,整平所得产品的上表面。接着,如图42e所示,在已经过整平过程的消耗性衬底200的整个表面上形成第三保护膜图案210,从而限定出第三开口区,后续过程中将在其中形成一个靠手,靠手位置水平靠近将在其中形成尖端部分的沟槽204。

此时,形成第三保护膜图案210,以确保后续过程中在将形成的之字形弯曲一次或多次的横梁部分的弯曲部位上形成靠手,其中横梁部分的弯曲部分靠近尖端部分。

然后,如图42f所示,在消耗性衬底200上形成第三保护膜图案210之后,通过进行CVD、PVD或镀膜过程,在第三保护膜图案210的第三开口区中形成预定厚度的导电材料211。随后,整平所得产品的上表面。

此时,可以通过CMP、深腐蚀和研磨等方法将导电材料211形成的所得产品的上表面整平。

随后,如图42g所示,通过除去第二保护膜图案206和第三保护膜图案210,形成横梁部分214和靠手212。由诸如聚酰亚胺、聚对二甲苯等绝缘物质制成的绝缘包覆层216施加到靠手212的外表面上。

接着,如图42h所示,其上已实现预定电路图案的、诸如PCB之类的电子元件300的末端形成包含预定大小之凸起的立柱(post)部分。通过焊接、钎焊、镀膜、导电粘合剂等连接装置304,使前面过程中在消耗性衬底200上形成的横梁部分24末端与立柱部分302相连接,其中横梁部分24的末端离靠手212最远。

最后,如图42i所示,通过湿法蚀刻除去消耗性衬底200,使横梁部分自由,并且尖端部分218与其连接,横梁部分214上具有靠手212的电接触元件即得以完成。

图43a至43d是截面图,这些图解释了图39a和39b所示的用于测试电子装置的电接触元件的生产方法。

在本发明第五实施方案的方法中,如图43a所示,与第四个实施方案中电接触元件的生产方法相同,第二保护膜图案404的形成能够限定第二开口区,在该开口区中,形成之字形弯曲一次或多次、具有至少一个弯曲部分的横梁部分。第二保护膜图案404与消耗性衬底400上形成的沟槽402相通,沟槽402通过使用第一保护膜图案(未示出)进行蚀刻过程在消耗性衬底400上限定,并且在沟槽中形成尖端部分。

限定沟槽402之后,通过在沟槽402中进行一次或多次各向异性蚀刻,增加沟槽402的深度,从而使沟槽402具有截头多边棱柱形或截头圆锥形构形,其中具有倾斜的侧面。另外,通过使沟槽204的内表面变得圆滑,在沟槽中进行一次或多次各向异性蚀刻,形成圆滑的尖端部分218。

然后,在消耗性衬底400上形成第二保护膜图案404之后,通过进行CVD、PVD或镀膜过程,在第二保护膜图案404的第二开口区中形成预定厚度的导电材料406。随后,整平所得产品的上表面。

接着,如图43b所示,通过除去第二保护膜图案404,形成之字形弯曲一次或多次、具有之字形构形的横梁部分408。此时,通过实施湿法蚀刻等除去第二保护膜图案。

接着,如图43c所示,其上已实现预定电路图案的、诸如PCB之类的电子元件500的末端形成具有预定大小的靠手504。由诸如聚酰亚胺、聚对二甲苯等绝缘物质制成的绝缘包覆层506施加到靠手504的外表面上。

此时,在之字形弯曲一次或多次、水平位置上与尖端部分相邻的横梁部分408的弯曲部分位置上的电子元件500上形成靠手504。

在电子元件500的末端形成包含具有预定大小之凸起的立柱部分502。通过焊接、钎焊、镀膜、导电粘合剂等连接装置508,使离沟槽402最远的横梁部分408末端与立柱部分502相连。

最后,如图43d所示,通过湿法蚀刻除去消耗性衬底400,从而使横梁部分408自由并且尖端部分410与之相接触,制成了电子元件500上具有靠手504的电接触元件。

图44a至44d是截面图,这些图解释了图40a和40b所示的用于测试电子装置的电接触元件的生产方法。

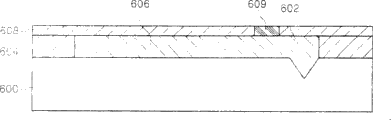

在本发明第六个实施方案的方法中,如图44a所示,与第四个实施方案中电接触元件的生产方法相同,第二保护膜图案604的形成能够限定第二开口区,在该开口区中,形成之字形弯曲一次或多次、具有至少一个弯曲部分的横梁部分。第二保护膜图案604和通过使用第一保护膜图案(未示出)进行蚀刻过程在消耗性衬底600上限定的沟槽602相通,并在沟槽中形成尖端部分。

在限定沟槽602之后,通过在沟槽602中进行一次或多次各向异性蚀刻,增加沟槽602的深度,从而使沟槽602具有截头多边棱柱形或截头圆锥形构形,其具有倾斜的侧面。同时,通过使沟槽602的内表面变得圆滑,在沟槽中进行一次或多次各向异性蚀刻,可以形成圆滑的尖端部分616。

然后,在消耗性衬底600上形成第二保护膜图案604之后,通过实施CVD、PVD或镀膜过程,在第二保护膜图案604的第二开口区中形成具有预定厚度的导电材料609。随后,整平所得产品的上表面。

另外,在包括已经过整平过程的消耗性衬底600的所得产品上形成第三保护膜图案608,从而限定第三开口区,在该开口区中形成靠手。

此时,形成第三保护膜图案608,以确保在之字形弯曲一次或多次、水平方向上与尖端部分相邻的、在后续过程中形成的横梁部分的弯曲部位上形成靠手。

然后,在消耗性衬底600上形成第三保护膜图案608之后,通过进行CVD、PVD或镀膜过程,在第三保护膜图案608的第三开口区中形成具有预定厚度的导电材料609。随后,整平所得产品的上表面。

接着,如图44b所示,通过除去第二保护膜图案604和第三保护膜图案608,形成横梁部分614和靠手610。将由诸如聚酰亚胺、聚对二甲苯等绝缘物质制成的绝缘包覆层612施加到靠手610的外表面上。

接着,如图44c所示,在其上已实现预定电路图案的、诸如PCB之类的电子元件700的末端形成具有预定大小的靠手702。将由诸如聚酰亚胺、聚对二甲苯等绝缘物质制成的绝缘包覆层704施加到靠手702的外表面上。

此时,在与横梁部分614上形成的靠手610相对应的位置上形成靠手702。

在电子元件700的末端形成包含具有预定大小之凸起的立柱部分706。通过焊接、钎焊、镀膜、导电粘合剂等连接装置708,使离沟槽602的横梁部分614末端和立柱部分706相连。

此时,靠手702的连接方式使之面对横梁部分614上形成的靠手610,并与其有间隔。

最后,如图44d所示,通过湿法蚀刻除去消耗性衬底600,从而使横梁部分614自由,并且尖端部分616与之相连,制成了横梁部分614和电子元件700上分别具有靠手610和702的电接触元件。

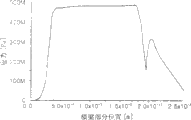

下面,将参考图45a和45b,描述施加在本发明中用于测试电子装置的电接触元件的横梁部分的应力分布,以及施加在用于测试电子装置的常规电接触元件的横梁部分的应力分布。

对于本发明中的横梁部分,如图45a所示,通过一个截面向横梁部分施加约500M(Pa)的恒定应力,其中的截面和连接装置分离,如5.0×10-4至2.0×10-33m的凸起。相反,对于常规的横梁部分,如图45b所示,通过相同的截面向横梁部分施加400M至500M(Pa)的可变应力。

从上面描述显然可以看出,本发明中用于测试电子装置的电接触元件的生产方法,以及通过该方法生产的电接触元件具有下述优点。

在本发明中,由于应力分散地施加到电接触元件的横梁部分,有可能使横梁部分反复与半导体芯片相接触的时候不至于断裂。

在本发明中,由于尖端部分的末端具有截头多边棱柱形或截头圆锥形构形,并具有圆滑末端表面;或者具有柱状构形,并具有圆滑末端表面,当电接触元件的尖端部分通过恒定的物理作用力反复与半导体芯片的基座相接触时,尖端部分不会刺穿基座上形成的氧化膜,防止当进行诸如引线焊接等后续半导体制造过程时缺陷比例增大。同时,避免了电接触元件的末端磨损并产生颗粒的可能性。

另外,由于将要和半导体基座之类物质相接触的电接触元件尖端部分的末端表面是圆滑的,增加了尖端部分的接触面积,从而提高了其导电性。

另外,由于电接触物质的尖端部分的长度延长至30μm~500μm,易于调整OD特性。由于凸出部分围绕尖端部分的近端形成,在该部位电接触元件尖端部分和横梁部分彼此相连,当电接触元件的尖端部分通过恒定的物理作用力反复与半导体芯片的基座相接触时,该应力并不施加在尖端部分的近端,并且可以防止尖端部分断裂。

另外,由于电接触元件的横梁部分具多个阶梯部分,完全符合最近的趋势,即在诸如高度集成的半导体芯片等电子装置中所需的间距变小的趋势。并且,由于电接触元件的横梁部分具有之字形构形,当电接触元件的尖端部分以恒定的物理作用力与半导体芯片的基座反复接触时,有可能将施加到横梁部分的应力分散,使横梁部分不至于断裂。

另外,由于可以使用具有高度重复性的微电子机械系统(micro electro mechanicalsystem,MEMS)大批量生产本发明的电接触元件,有可能提高产量、生产率和电子装置测试用具包,如包含电接触元件的探针卡的操作可靠性。

另外,由于靠手所导致的扭转效应,有可能用显著增大到一定程度的物理作用力来测试半导体芯片,该物理作用力的增大程度使得尖端部分可能刺穿半导体基座上所形成的氧化膜。

在附图和说明书中,公开了本发明的典型优选实施方案,虽然采用了专业术语,但这些术语只是在一般性和说明性的意义上使用,并不对以下的权利要求书中所限定的发明范围作任何限制。

Claims (10)

1. 一种制造用于测试电子器件的电接触元件的方法,该方法包括:

在消耗性衬底中形成限定尖端部分形状的沟槽;

形成具有开口的横梁掩模图案,所述开口限定横梁部分的形状并暴露所述沟槽;

形成具有横梁部分和尖端部分的电接触元件,所述横梁部分和尖端部分分别位于所述开口和所述沟槽中;和

移除所述消耗性衬底和所述横梁掩模图案,

其中,所述沟槽的形成包括至少一个湿法蚀刻步骤和至少一个干法蚀刻步骤;和

所述尖端部分包含连接所述横梁部分的近端部分、从所述近端部分向背离所述近端部分的方向延伸的远端部分和从近端部分的侧壁横向延伸的凸出部分,并且形成所述沟槽以限定所述近端、远端和凸出部分的形状。

2. 如权利要求1所述的方法,其中所述至少一个湿法蚀刻步骤利用包括氢氧化钾的化学品来实施,使得所述远端具有截头多边棱柱形状或截头圆锥形状。

3. 如权利要求1所述的方法,其中所述至少一个湿法蚀刻步骤利用包括氟化氢、硝酸和醋酸的化学品来实施,使得所述远端具有圆柱构形。

4. 如权利要求1所述的方法,其中所述至少一个干法蚀刻步骤增加所述沟槽的深度并使所述沟槽具有圆底表面。

5. 如权利要求1所述的方法,其中形成所述开口,使得所述横梁部分包含第一部分、连接第一部分的第二部分和连接第二部分的第三部分,其中第二部分具有弯曲部分。

6. 如权利要求5所述的方法,其中所述第二部分之字形弯曲一次或多次。

7. 如权利要求5所述的方法,其中所述横梁部分的第一、第二和第三部分布置在被所述开口暴露的消耗性衬底上,使得所述横梁部分的底表面是平坦的。

8. 如权利要求1所述的方法,其中所述沟槽的形成,包括:

形成限定所述近端部分形状的上沟槽,所述上沟槽具有倾斜预定角度的侧壁;

蚀刻所述上沟槽的中央底表面以形成限定所述远端部分形状的下沟槽。

9. 如权利要求8所述的方法,其中所述沟槽的形成还包括在形成上沟槽之后,各向异性蚀刻所述上沟槽的中央底表面以增加所述沟槽的深度。

10. 如权利要求8所述的方法,其中形成所述上沟槽包括利用包括氢氧化钾的化学品湿法蚀刻以使所述上沟槽的底表面具有截头多边棱柱形或截头圆锥形构形。

Applications Claiming Priority (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020020006367A KR100358513B1 (en) | 2002-02-05 | 2002-02-05 | Method of fabricating electrical contactor for testing electronic device and electrical contactor fabricated thereby |

| KR20026367 | 2002-02-05 | ||

| KR2002-6367 | 2002-02-05 | ||

| KR1020020068402 | 2002-11-06 | ||

| KR10-2002-0068402A KR100475468B1 (ko) | 2002-11-06 | 2002-11-06 | 전자소자 검사용 전기적 접촉체 |

| KR10-2002-0068402 | 2002-11-06 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN2008101355299A Division CN101354405B (zh) | 2002-02-05 | 2002-11-08 | 测试电子装置用电接触元件的制造方法及电接触元件 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1618124A CN1618124A (zh) | 2005-05-18 |

| CN100423221C true CN100423221C (zh) | 2008-10-01 |

Family

ID=36931458

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB028277597A Expired - Fee Related CN100423221C (zh) | 2002-02-05 | 2002-11-08 | 测试电子装置用电接触元件的制造方法及所制得的电接触元件 |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US20040018752A1 (zh) |

| JP (1) | JP2005517192A (zh) |

| CN (1) | CN100423221C (zh) |

| AU (1) | AU2002353582A1 (zh) |

| DE (1) | DE10297653T5 (zh) |

| WO (1) | WO2003067650A1 (zh) |

Families Citing this family (30)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7459795B2 (en) * | 2004-08-19 | 2008-12-02 | Formfactor, Inc. | Method to build a wirebond probe card in a many at a time fashion |

| KR100586675B1 (ko) * | 2004-09-22 | 2006-06-12 | 주식회사 파이컴 | 수직형 전기적 접촉체의 제조방법 및 이에 따른 수직형전기적 접촉체 |

| KR100585561B1 (ko) * | 2004-10-26 | 2006-06-07 | 주식회사 파이컴 | 수직형 전기적 접촉체 및 그 제조방법 |

| KR100626570B1 (ko) * | 2004-12-24 | 2006-09-25 | 주식회사 파이컴 | 감지용 프로브를 포함하는 프로브 카드 제작 방법 및 그프로브 카드, 프로브카드 검사 시스템 |

| US7362119B2 (en) * | 2005-08-01 | 2008-04-22 | Touchdown Technologies, Inc | Torsion spring probe contactor design |

| US7589542B2 (en) * | 2007-04-12 | 2009-09-15 | Touchdown Technologies Inc. | Hybrid probe for testing semiconductor devices |

| US7772859B2 (en) * | 2005-08-01 | 2010-08-10 | Touchdown Technologies, Inc. | Probe for testing semiconductor devices with features that increase stress tolerance |

| KR100653636B1 (ko) * | 2005-08-03 | 2006-12-05 | 주식회사 파이컴 | 수직형 프로브, 그 제조 방법 및 프로브의 본딩 방법 |

| KR100664443B1 (ko) * | 2005-08-10 | 2007-01-03 | 주식회사 파이컴 | 캔틸레버형 프로브 및 그 제조 방법 |

| TW200739083A (en) * | 2005-09-30 | 2007-10-16 | Sv Probe Pte Ltd | Cantilever probe structure for a probe card assembly |

| ITMI20052290A1 (it) * | 2005-11-30 | 2007-06-01 | Pasqua Roberto Della | Servizio di messaggistica istantanea con interfaccia utente minimizzata |

| KR100749735B1 (ko) * | 2006-06-07 | 2007-08-16 | 주식회사 파이컴 | 캔틸레버형 프로브 제조 방법 및 이를 이용한 프로브 카드제조 방법 |

| US20080011476A1 (en) * | 2006-07-11 | 2008-01-17 | Halliburton Energy Services, Inc. | Methods for coating particulates with tackifying compounds |

| US7782072B2 (en) * | 2006-09-27 | 2010-08-24 | Formfactor, Inc. | Single support structure probe group with staggered mounting pattern |

| JP2008151573A (ja) * | 2006-12-15 | 2008-07-03 | Micronics Japan Co Ltd | 電気的接続装置およびその製造方法 |

| JP4916893B2 (ja) * | 2007-01-05 | 2012-04-18 | 株式会社日本マイクロニクス | プローブの製造方法 |

| KR101368139B1 (ko) * | 2007-07-16 | 2014-03-12 | 어드밴티스트 아메리카, 인크. | 마이크로 전기 기계 시스템을 수리하기 위한 장치 및 방법 |

| JP2009025107A (ja) * | 2007-07-19 | 2009-02-05 | Advanced Systems Japan Inc | 凸形スパイラルコンタクタの製造方法 |

| US7589547B2 (en) * | 2007-09-13 | 2009-09-15 | Touchdown Technologies, Inc. | Forked probe for testing semiconductor devices |

| US20090072851A1 (en) * | 2007-09-13 | 2009-03-19 | Touchdown Technologies, Inc. | Multi-Pivot Probe Card For Testing Semiconductor Devices |

| US20090144970A1 (en) * | 2007-12-06 | 2009-06-11 | Winmems Technologies Holdings Co., Ltd. | Fabricating an array of mems parts on a substrate |

| US7811849B2 (en) * | 2008-01-30 | 2010-10-12 | Winmems Technologies Co., Ltd. | Placing a MEMS part on an application platform using a guide mask |

| US20100013060A1 (en) * | 2008-06-22 | 2010-01-21 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method of forming a conductive trench in a silicon wafer and silicon wafer comprising such trench |

| US8089294B2 (en) * | 2008-08-05 | 2012-01-03 | WinMENS Technologies Co., Ltd. | MEMS probe fabrication on a reusable substrate for probe card application |

| US7737714B2 (en) * | 2008-11-05 | 2010-06-15 | Winmems Technologies Holdings Co., Ltd. | Probe assembly arrangement |

| US7928751B2 (en) * | 2009-02-18 | 2011-04-19 | Winmems Technologies Holdings Co., Ltd. | MEMS interconnection pins fabrication on a reusable substrate for probe card application |

| TWI417646B (zh) * | 2010-03-29 | 2013-12-01 | Pixart Imaging Inc | 改善鎢沉積拓樸形貌之微機電系統光罩與方法 |

| CN102219177A (zh) * | 2010-04-14 | 2011-10-19 | 原相科技股份有限公司 | 改善钨沉积拓朴形貌的微机电系统光罩与方法 |

| US10859602B2 (en) * | 2012-03-07 | 2020-12-08 | Advantest Corporation | Transferring electronic probe assemblies to space transformers |

| CN110277437A (zh) * | 2018-03-16 | 2019-09-24 | 张峻玮 | 一种外包覆式高效能低漏电流的肖基二极管结构及其制造方法 |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07333232A (ja) * | 1994-06-13 | 1995-12-22 | Canon Inc | 探針を有するカンチレバーの形成方法 |

| JPH0850146A (ja) * | 1994-06-03 | 1996-02-20 | Hitachi Ltd | 接続装置およびその製造方法 |

| CN1194692A (zh) * | 1996-05-17 | 1998-09-30 | 福姆法克特公司 | 用于微电子互连元件的接触端头结构及其制造方法 |

| CN1208368A (zh) * | 1995-05-26 | 1999-02-17 | 福姆法克特公司 | 利用牺牲基片制作互连件和接点 |

| US6184053B1 (en) * | 1993-11-16 | 2001-02-06 | Formfactor, Inc. | Method of making microelectronic spring contact elements |

| KR20010077628A (ko) * | 2000-02-03 | 2001-08-20 | 최성수 | 근접장 광 센서용 서브-파장 구멍의 형성방법 |

| US6307392B1 (en) * | 1997-10-28 | 2001-10-23 | Nec Corporation | Probe card and method of forming a probe card |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4998062A (en) | 1988-10-25 | 1991-03-05 | Tokyo Electron Limited | Probe device having micro-strip line structure |

| US4916002A (en) * | 1989-01-13 | 1990-04-10 | The Board Of Trustees Of The Leland Jr. University | Microcasting of microminiature tips |

| DE68902141T2 (de) * | 1989-08-16 | 1993-02-25 | Ibm | Verfahren fuer die herstellung mikromechanischer messfuehler fuer afm/stm-profilometrie und mikromechanischer messfuehlerkopf. |

| US5177438A (en) * | 1991-08-02 | 1993-01-05 | Motorola, Inc. | Low resistance probe for semiconductor |

| US6482013B2 (en) * | 1993-11-16 | 2002-11-19 | Formfactor, Inc. | Microelectronic spring contact element and electronic component having a plurality of spring contact elements |

| US5513430A (en) * | 1994-08-19 | 1996-05-07 | Motorola, Inc. | Method for manufacturing a probe |

| CN1145802C (zh) * | 1996-05-17 | 2004-04-14 | 福姆法克特公司 | 微电子弹簧接触元件及电子部件 |

| US6307932B1 (en) * | 1998-03-31 | 2001-10-23 | Avaya Technology Corp | End-user control of audio delivery endpoint in a multimedia environment |

| US6414501B2 (en) * | 1998-10-01 | 2002-07-02 | Amst Co., Ltd. | Micro cantilever style contact pin structure for wafer probing |

| US6426638B1 (en) * | 2000-05-02 | 2002-07-30 | Decision Track Llc | Compliant probe apparatus |

| US6970005B2 (en) * | 2000-08-24 | 2005-11-29 | Texas Instruments Incorporated | Multiple-chip probe and universal tester contact assemblage |

| JP2002071719A (ja) | 2000-09-01 | 2002-03-12 | Kobe Steel Ltd | プローブカード及びその製造方法 |

| US6811406B2 (en) * | 2001-04-12 | 2004-11-02 | Formfactor, Inc. | Microelectronic spring with additional protruding member |

-

2002

- 2002-11-08 DE DE10297653T patent/DE10297653T5/de not_active Ceased

- 2002-11-08 WO PCT/KR2002/002073 patent/WO2003067650A1/en active Application Filing

- 2002-11-08 AU AU2002353582A patent/AU2002353582A1/en not_active Abandoned

- 2002-11-08 CN CNB028277597A patent/CN100423221C/zh not_active Expired - Fee Related

- 2002-11-08 JP JP2003566894A patent/JP2005517192A/ja active Pending

-

2003

- 2003-01-23 US US10/350,737 patent/US20040018752A1/en not_active Abandoned

-

2006

- 2006-02-13 US US11/352,658 patent/US7579855B2/en not_active Expired - Fee Related

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6184053B1 (en) * | 1993-11-16 | 2001-02-06 | Formfactor, Inc. | Method of making microelectronic spring contact elements |

| JPH0850146A (ja) * | 1994-06-03 | 1996-02-20 | Hitachi Ltd | 接続装置およびその製造方法 |

| JPH07333232A (ja) * | 1994-06-13 | 1995-12-22 | Canon Inc | 探針を有するカンチレバーの形成方法 |

| CN1208368A (zh) * | 1995-05-26 | 1999-02-17 | 福姆法克特公司 | 利用牺牲基片制作互连件和接点 |

| CN1194692A (zh) * | 1996-05-17 | 1998-09-30 | 福姆法克特公司 | 用于微电子互连元件的接触端头结构及其制造方法 |

| US6307392B1 (en) * | 1997-10-28 | 2001-10-23 | Nec Corporation | Probe card and method of forming a probe card |

| KR20010077628A (ko) * | 2000-02-03 | 2001-08-20 | 최성수 | 근접장 광 센서용 서브-파장 구멍의 형성방법 |

Also Published As

| Publication number | Publication date |

|---|---|

| WO2003067650A1 (en) | 2003-08-14 |

| US7579855B2 (en) | 2009-08-25 |

| US20060192581A1 (en) | 2006-08-31 |

| US20040018752A1 (en) | 2004-01-29 |

| DE10297653T5 (de) | 2005-04-14 |

| AU2002353582A1 (en) | 2003-09-02 |

| JP2005517192A (ja) | 2005-06-09 |

| CN1618124A (zh) | 2005-05-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100423221C (zh) | 测试电子装置用电接触元件的制造方法及所制得的电接触元件 | |

| KR100307082B1 (ko) | 집적회로의연결구조체및그제조방법 | |

| US6400166B2 (en) | Micro probe and method of fabricating same | |

| US6613662B2 (en) | Method for making projected contact structures for engaging bumped semiconductor devices | |

| US7053641B2 (en) | Interconnect having spring contacts | |

| US6651325B2 (en) | Method for forming cantilever beam probe card and probe card formed | |

| US7602204B2 (en) | Probe card manufacturing method including sensing probe and the probe card, probe card inspection system | |

| US6392430B1 (en) | Method of forming coaxial silicon interconnects | |

| KR100523745B1 (ko) | 전자소자 검사용 마이크로 프로브 및 그 제조 방법 | |

| CN101354405B (zh) | 测试电子装置用电接触元件的制造方法及电接触元件 | |

| KR100586675B1 (ko) | 수직형 전기적 접촉체의 제조방법 및 이에 따른 수직형전기적 접촉체 | |

| KR100703043B1 (ko) | 검사용 프로브 기판 및 그 제조 방법 | |

| US7167010B2 (en) | Pin-in elastomer electrical contactor and methods and processes for making and using the same | |

| KR100475468B1 (ko) | 전자소자 검사용 전기적 접촉체 | |

| KR100464681B1 (ko) | 전자소자 검사용 전기적 접촉체의 팁 제조방법 | |

| KR100463308B1 (ko) | 수직형 전기적 접촉체 및 이의 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C17 | Cessation of patent right | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20081001 Termination date: 20121108 |