CN100481506C - 半导体器件及其制造方法 - Google Patents

半导体器件及其制造方法 Download PDFInfo

- Publication number

- CN100481506C CN100481506C CNB2006101030029A CN200610103002A CN100481506C CN 100481506 C CN100481506 C CN 100481506C CN B2006101030029 A CNB2006101030029 A CN B2006101030029A CN 200610103002 A CN200610103002 A CN 200610103002A CN 100481506 C CN100481506 C CN 100481506C

- Authority

- CN

- China

- Prior art keywords

- tft

- film

- gate electrode

- layer

- semiconductor device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 87

- 238000000034 method Methods 0.000 title description 38

- 239000010410 layer Substances 0.000 claims description 211

- 239000010408 film Substances 0.000 claims description 164

- 239000000463 material Substances 0.000 claims description 52

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 claims description 21

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 claims description 19

- 229910052721 tungsten Inorganic materials 0.000 claims description 19

- 239000010937 tungsten Substances 0.000 claims description 19

- 239000004411 aluminium Substances 0.000 claims description 17

- 229910052782 aluminium Inorganic materials 0.000 claims description 17

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 claims description 17

- 239000010949 copper Substances 0.000 claims description 15

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims description 14

- 239000011229 interlayer Substances 0.000 claims description 14

- 239000001301 oxygen Substances 0.000 claims description 14

- 229910052760 oxygen Inorganic materials 0.000 claims description 14

- 229910052751 metal Inorganic materials 0.000 claims description 12

- 239000002184 metal Substances 0.000 claims description 12

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 claims description 9

- 229910052802 copper Inorganic materials 0.000 claims description 9

- 239000010409 thin film Substances 0.000 claims description 2

- 239000000758 substrate Substances 0.000 abstract description 46

- 238000010276 construction Methods 0.000 abstract description 5

- 239000004020 conductor Substances 0.000 description 106

- 239000012535 impurity Substances 0.000 description 43

- 239000003990 capacitor Substances 0.000 description 41

- 230000015572 biosynthetic process Effects 0.000 description 33

- 239000011159 matrix material Substances 0.000 description 32

- 239000004973 liquid crystal related substance Substances 0.000 description 30

- 238000005401 electroluminescence Methods 0.000 description 28

- 239000010936 titanium Substances 0.000 description 27

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 24

- 238000004020 luminiscence type Methods 0.000 description 22

- 230000002269 spontaneous effect Effects 0.000 description 22

- 229910052710 silicon Inorganic materials 0.000 description 21

- 239000010703 silicon Substances 0.000 description 21

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 18

- 238000004519 manufacturing process Methods 0.000 description 18

- 229910052698 phosphorus Inorganic materials 0.000 description 18

- 239000011574 phosphorus Substances 0.000 description 18

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 15

- 229910052715 tantalum Inorganic materials 0.000 description 15

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 15

- 229910052719 titanium Inorganic materials 0.000 description 15

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 13

- 230000000694 effects Effects 0.000 description 13

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 12

- 229910052750 molybdenum Inorganic materials 0.000 description 12

- 239000011733 molybdenum Substances 0.000 description 12

- 238000010438 heat treatment Methods 0.000 description 11

- 239000012298 atmosphere Substances 0.000 description 10

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 8

- 229910021417 amorphous silicon Inorganic materials 0.000 description 8

- 229910052796 boron Inorganic materials 0.000 description 8

- 230000007797 corrosion Effects 0.000 description 8

- 238000005260 corrosion Methods 0.000 description 8

- PQXKHYXIUOZZFA-UHFFFAOYSA-M lithium fluoride Chemical compound [Li+].[F-] PQXKHYXIUOZZFA-UHFFFAOYSA-M 0.000 description 8

- 229920005989 resin Polymers 0.000 description 8

- 239000011347 resin Substances 0.000 description 8

- 150000001875 compounds Chemical class 0.000 description 7

- 238000002425 crystallisation Methods 0.000 description 7

- 239000000945 filler Substances 0.000 description 7

- 239000003566 sealing material Substances 0.000 description 7

- 230000005540 biological transmission Effects 0.000 description 6

- 239000003054 catalyst Substances 0.000 description 6

- 238000010586 diagram Methods 0.000 description 6

- 238000005516 engineering process Methods 0.000 description 6

- 238000005984 hydrogenation reaction Methods 0.000 description 6

- 229910003437 indium oxide Inorganic materials 0.000 description 6

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 6

- 238000002347 injection Methods 0.000 description 6

- 239000007924 injection Substances 0.000 description 6

- 229910052757 nitrogen Inorganic materials 0.000 description 6

- 229920000553 poly(phenylenevinylene) Polymers 0.000 description 6

- 238000002360 preparation method Methods 0.000 description 6

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 6

- 229910052581 Si3N4 Inorganic materials 0.000 description 5

- 230000004913 activation Effects 0.000 description 5

- 239000011248 coating agent Substances 0.000 description 5

- 238000000576 coating method Methods 0.000 description 5

- 239000013078 crystal Substances 0.000 description 5

- 230000008025 crystallization Effects 0.000 description 5

- 230000007850 degeneration Effects 0.000 description 5

- 239000011521 glass Substances 0.000 description 5

- 150000002500 ions Chemical class 0.000 description 5

- 229920002120 photoresistant polymer Polymers 0.000 description 5

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 5

- 229920000728 polyester Polymers 0.000 description 5

- -1 preferably Substances 0.000 description 5

- 238000012545 processing Methods 0.000 description 5

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 5

- 230000035882 stress Effects 0.000 description 5

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 4

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 4

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 4

- YRKCREAYFQTBPV-UHFFFAOYSA-N acetylacetone Chemical compound CC(=O)CC(C)=O YRKCREAYFQTBPV-UHFFFAOYSA-N 0.000 description 4

- 229910045601 alloy Inorganic materials 0.000 description 4

- 239000000956 alloy Substances 0.000 description 4

- 210000002469 basement membrane Anatomy 0.000 description 4

- 238000002474 experimental method Methods 0.000 description 4

- 230000006870 function Effects 0.000 description 4

- 239000001257 hydrogen Substances 0.000 description 4

- 229910052739 hydrogen Inorganic materials 0.000 description 4

- 230000003071 parasitic effect Effects 0.000 description 4

- 229920001721 polyimide Polymers 0.000 description 4

- 239000000565 sealant Substances 0.000 description 4

- 229910052814 silicon oxide Inorganic materials 0.000 description 4

- 238000011282 treatment Methods 0.000 description 4

- SMZOUWXMTYCWNB-UHFFFAOYSA-N 2-(2-methoxy-5-methylphenyl)ethanamine Chemical compound COC1=CC=C(C)C=C1CCN SMZOUWXMTYCWNB-UHFFFAOYSA-N 0.000 description 3

- NIXOWILDQLNWCW-UHFFFAOYSA-N 2-Propenoic acid Natural products OC(=O)C=C NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 3

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 3

- 239000004642 Polyimide Substances 0.000 description 3

- IVHJCRXBQPGLOV-UHFFFAOYSA-N azanylidynetungsten Chemical compound [W]#N IVHJCRXBQPGLOV-UHFFFAOYSA-N 0.000 description 3

- 238000001704 evaporation Methods 0.000 description 3

- 239000012299 nitrogen atmosphere Substances 0.000 description 3

- 229920003227 poly(N-vinyl carbazole) Polymers 0.000 description 3

- 239000004800 polyvinyl chloride Substances 0.000 description 3

- 229920000915 polyvinyl chloride Polymers 0.000 description 3

- 238000007789 sealing Methods 0.000 description 3

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 3

- 229910001887 tin oxide Inorganic materials 0.000 description 3

- 229910000838 Al alloy Inorganic materials 0.000 description 2

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 2

- XYFCBTPGUUZFHI-UHFFFAOYSA-N Phosphine Chemical compound P XYFCBTPGUUZFHI-UHFFFAOYSA-N 0.000 description 2

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 2

- 239000003513 alkali Substances 0.000 description 2

- 229910052783 alkali metal Inorganic materials 0.000 description 2

- 229910021529 ammonia Inorganic materials 0.000 description 2

- 238000000137 annealing Methods 0.000 description 2

- 229910052786 argon Inorganic materials 0.000 description 2

- GPBUGPUPKAGMDK-UHFFFAOYSA-N azanylidynemolybdenum Chemical compound [Mo]#N GPBUGPUPKAGMDK-UHFFFAOYSA-N 0.000 description 2

- 230000006399 behavior Effects 0.000 description 2

- 230000003139 buffering effect Effects 0.000 description 2

- DQXBYHZEEUGOBF-UHFFFAOYSA-N but-3-enoic acid;ethene Chemical compound C=C.OC(=O)CC=C DQXBYHZEEUGOBF-UHFFFAOYSA-N 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 239000003822 epoxy resin Substances 0.000 description 2

- 239000005038 ethylene vinyl acetate Substances 0.000 description 2

- 238000011156 evaluation Methods 0.000 description 2

- 230000008020 evaporation Effects 0.000 description 2

- 239000004744 fabric Substances 0.000 description 2

- 239000011152 fibreglass Substances 0.000 description 2

- 239000007789 gas Substances 0.000 description 2

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical group [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 2

- MRNHPUHPBOKKQT-UHFFFAOYSA-N indium;tin;hydrate Chemical compound O.[In].[Sn] MRNHPUHPBOKKQT-UHFFFAOYSA-N 0.000 description 2

- 229910010272 inorganic material Inorganic materials 0.000 description 2

- 239000011147 inorganic material Substances 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 229920001200 poly(ethylene-vinyl acetate) Polymers 0.000 description 2

- 229920002037 poly(vinyl butyral) polymer Polymers 0.000 description 2

- 229920000767 polyaniline Polymers 0.000 description 2

- 229920000647 polyepoxide Polymers 0.000 description 2

- 229920001296 polysiloxane Polymers 0.000 description 2

- 230000008569 process Effects 0.000 description 2

- 239000010453 quartz Substances 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 238000004088 simulation Methods 0.000 description 2

- 150000003384 small molecules Chemical class 0.000 description 2

- 239000000243 solution Substances 0.000 description 2

- 238000012360 testing method Methods 0.000 description 2

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 2

- 239000011787 zinc oxide Substances 0.000 description 2

- 229910001316 Ag alloy Inorganic materials 0.000 description 1

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 1

- 241001062009 Indigofera Species 0.000 description 1

- 229910019142 PO4 Inorganic materials 0.000 description 1

- 229920001609 Poly(3,4-ethylenedioxythiophene) Polymers 0.000 description 1

- 239000004952 Polyamide Substances 0.000 description 1

- ZLMJMSJWJFRBEC-UHFFFAOYSA-N Potassium Chemical compound [K] ZLMJMSJWJFRBEC-UHFFFAOYSA-N 0.000 description 1

- 229910003902 SiCl 4 Inorganic materials 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- 229910001362 Ta alloys Inorganic materials 0.000 description 1

- 229910001080 W alloy Inorganic materials 0.000 description 1

- 238000002083 X-ray spectrum Methods 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- 238000010521 absorption reaction Methods 0.000 description 1

- 239000012190 activator Substances 0.000 description 1

- 239000005030 aluminium foil Substances 0.000 description 1

- 150000001408 amides Chemical class 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 125000004429 atom Chemical group 0.000 description 1

- QVQLCTNNEUAWMS-UHFFFAOYSA-N barium oxide Inorganic materials [Ba]=O QVQLCTNNEUAWMS-UHFFFAOYSA-N 0.000 description 1

- CSSYLTMKCUORDA-UHFFFAOYSA-N barium(2+);oxygen(2-) Chemical compound [O-2].[Ba+2] CSSYLTMKCUORDA-UHFFFAOYSA-N 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 239000002585 base Substances 0.000 description 1

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 1

- YXTPWUNVHCYOSP-UHFFFAOYSA-N bis($l^{2}-silanylidene)molybdenum Chemical compound [Si]=[Mo]=[Si] YXTPWUNVHCYOSP-UHFFFAOYSA-N 0.000 description 1

- 229920005549 butyl rubber Polymers 0.000 description 1

- 238000004364 calculation method Methods 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 239000002800 charge carrier Substances 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 238000011109 contamination Methods 0.000 description 1

- 239000006071 cream Substances 0.000 description 1

- 125000004093 cyano group Chemical group *C#N 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- ZOCHARZZJNPSEU-UHFFFAOYSA-N diboron Chemical compound B#B ZOCHARZZJNPSEU-UHFFFAOYSA-N 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 229910001873 dinitrogen Inorganic materials 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 239000007772 electrode material Substances 0.000 description 1

- 230000005284 excitation Effects 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 239000011737 fluorine Substances 0.000 description 1

- 229910052731 fluorine Inorganic materials 0.000 description 1

- 230000014509 gene expression Effects 0.000 description 1

- 238000005247 gettering Methods 0.000 description 1

- 150000002431 hydrogen Chemical class 0.000 description 1

- 238000005224 laser annealing Methods 0.000 description 1

- 238000005499 laser crystallization Methods 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 230000005012 migration Effects 0.000 description 1

- 238000013508 migration Methods 0.000 description 1

- 239000003595 mist Substances 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 229910021344 molybdenum silicide Inorganic materials 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- QJGQUHMNIGDVPM-UHFFFAOYSA-N nitrogen group Chemical group [N] QJGQUHMNIGDVPM-UHFFFAOYSA-N 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000010355 oscillation Effects 0.000 description 1

- 239000005011 phenolic resin Substances 0.000 description 1

- NBIIXXVUZAFLBC-UHFFFAOYSA-K phosphate Chemical compound [O-]P([O-])([O-])=O NBIIXXVUZAFLBC-UHFFFAOYSA-K 0.000 description 1

- 239000010452 phosphate Substances 0.000 description 1

- 229920002647 polyamide Polymers 0.000 description 1

- 229920006267 polyester film Polymers 0.000 description 1

- 239000009719 polyimide resin Substances 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 238000006116 polymerization reaction Methods 0.000 description 1

- 229910052700 potassium Inorganic materials 0.000 description 1

- 239000011591 potassium Substances 0.000 description 1

- 238000004151 rapid thermal annealing Methods 0.000 description 1

- 230000008707 rearrangement Effects 0.000 description 1

- 230000027756 respiratory electron transport chain Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 230000011218 segmentation Effects 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 238000005245 sintering Methods 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 230000007480 spreading Effects 0.000 description 1

- 238000003892 spreading Methods 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 230000008646 thermal stress Effects 0.000 description 1

- 229910000597 tin-copper alloy Inorganic materials 0.000 description 1

- 229910021341 titanium silicide Inorganic materials 0.000 description 1

- WQJQOUPTWCFRMM-UHFFFAOYSA-N tungsten disilicide Chemical compound [Si]#[W]#[Si] WQJQOUPTWCFRMM-UHFFFAOYSA-N 0.000 description 1

- 229910021342 tungsten silicide Inorganic materials 0.000 description 1

- 238000013022 venting Methods 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

- RNWHGQJWIACOKP-UHFFFAOYSA-N zinc;oxygen(2-) Chemical group [O-2].[Zn+2] RNWHGQJWIACOKP-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1345—Conductors connecting electrodes to cell terminals

- G02F1/13454—Drivers integrated on the active matrix substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136286—Wiring, e.g. gate line, drain line

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/1368—Active matrix addressed cells in which the switching element is a three-electrode device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/124—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or layout of the wiring layers specially adapted to the circuit arrangement, e.g. scanning lines in LCD pixel circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42384—Gate electrodes for field effect devices for field-effect transistors with insulated gate for thin film field effect transistors, e.g. characterised by the thickness or the shape of the insulator or the dimensions, the shape or the lay-out of the conductor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/4908—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET for thin film semiconductor, e.g. gate of TFT

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66742—Thin film unipolar transistors

- H01L29/6675—Amorphous silicon or polysilicon transistors

- H01L29/66757—Lateral single gate single channel transistors with non-inverted structure, i.e. the channel layer is formed before the gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

- H01L29/78618—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device characterised by the drain or the source properties, e.g. the doping structure, the composition, the sectional shape or the contact structure

- H01L29/78621—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device characterised by the drain or the source properties, e.g. the doping structure, the composition, the sectional shape or the contact structure with LDD structure or an extension or an offset region or characterised by the doping profile

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

- H01L29/78618—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device characterised by the drain or the source properties, e.g. the doping structure, the composition, the sectional shape or the contact structure

- H01L29/78621—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device characterised by the drain or the source properties, e.g. the doping structure, the composition, the sectional shape or the contact structure with LDD structure or an extension or an offset region or characterised by the doping profile

- H01L29/78627—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device characterised by the drain or the source properties, e.g. the doping structure, the composition, the sectional shape or the contact structure with LDD structure or an extension or an offset region or characterised by the doping profile with a significant overlap between the lightly doped drain and the gate electrode, e.g. GOLDD

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78645—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with multiple gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78684—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising semiconductor materials of Group IV not being silicon, or alloys including an element of the group IV, e.g. Ge, SiN alloys, SiC alloys

Abstract

本发明主要提供可用于大尺寸屏幕的有源矩阵显示器件的栅电极和栅极布线,其中为了实现本目的,本发明的构成是一种半导体器件,在同一衬底上具有设置在显示区的象素TFT和围绕显示区设置的驱动电路TFT,其中象素TFT和驱动电路TFT的栅电极由第一导体层形成,栅电极通过连接器与第二导体层形成的栅极布线电接触,连接器设置在象素TFT和驱动电路TFT的沟道形成区之外。

Description

本申请是申请人株式会社半导体能源研究所于2000年4月12日提交的、发明名称为半导体器件及其制造方法的中国专利申请No.200610073781.2的分案申请。

技术领域

本发明涉及设置有有源电路的半导体器件,该有源电路包括位于具有绝缘表面的衬底上的薄膜晶体管(以下称为“TFT”)。本发明特别有利于用于光电器件,典型的一种是在同一衬底上形成有图象显示区及其驱动电路的液晶显示器件,并且有利于用于安装有光电器件的电子设备。在本说明书中,“半导体器件”将是指功能基于半导体特性的所有器件,其范围包括上述光电器件和其上安装有光电器件的电子器件。

背景技术

具有形成了结晶硅膜的半导体层的TFT(以下称为“结晶硅TFT”),具有高的场效应迁移率,因此能够形成具有各种功能的电路。采用结晶硅TFT的有源矩阵型液晶显示器件具有形成在同一衬底上的图象显示区和用于图象显示的驱动电路。在图象显示区中,设置有由n-沟道TFT形成的象素TFT,以及存储电容器,而驱动电路由移位寄存器电路、电平漂移电路、缓冲电路、取样电路等构成,这是基于CMOS(互补金属氧化物半导体)电路形成的。

但是,对于象素TFT和驱动电路TFT来说,其工作条件并不相同,所以常常要求TFT具有不同的性能。例如,象素TFT起开关元件的作用,通过对液晶施加电压对其驱动。由于采用交变电流驱动液晶,所以最常见的是采用众所周知的帧反转驱动系统。在这种系统中,要求象素TFT具有足够低的截止状态电流值(TFT截止时流过的漏电流).以便使功耗最小。另一方面,由于对驱动电路的缓冲电路施加高的驱动电压,所以必须提高电压电阻,防止因施加高电压产生击穿。提高电流驱动容量要求导通状态电流值(TFT导通时流过的漏电流)有足够的保证。

轻微掺杂的漏结构(LDD)是截止状态电流值呈现降低的TFT的公知结构。这种结构设置有添加低浓度杂质元素的区,该区位于沟道形成区和通过添加高浓度杂质元素形成的源区或漏区之间,这种区称为“LDD区”。防止导通状态电流值因热载流子而变劣的一种公知措施,是众所周知的GOLD结构(栅-漏交叠LDD),其中LDD区位于栅电极之上,其间具有栅绝缘膜。已知这种类型的结构通过衰减靠近漏的高电压能有效地防止含有热载流子,从而避免变劣现象。

同时,对更大尺寸和更复杂屏幕的需求日益增大,使有源矩阵型液晶显示器件有更大市场价值。但是,更大的尺寸和更复杂的屏幕增加了扫描线(栅布线)的数量和长度,从而提高了栅布线的低电阻的必要性。亦即,随着扫描线数量的增加,对液晶的充电时间被缩短,以致对于栅布线的时间常数(电阻×容量)必须降低以便更快响应。例如,如果形成栅布线的材料的电阻率是100μΩcm,则对屏幕尺寸的限制约是6英寸,但是对于3μΩcm的电阻率,可以实现对应于27英寸的显示。

而且,对象素矩阵电路的象素TFT和例如移位寄存器或缓冲器电路的驱动电路的TFT的性能要求并不总是相同的。例如,在象素TFT中,对栅极施加大的反向偏压(在n-沟道TFT的情形是负电压),但是在反向偏压状态下驱动电路TFT基本上不能工作。象素TFT的工作速度小于驱动电路TFT工作速度的1/100也是足够的。

此外,在GOLD结构提供强有力的防止导通状态电流值变劣的效应的同时,还存在与通常的LDD结构相比截止状态电流值大的问题。因此,这不是用于象素TFT的优选结构。相反,通常的LDD结构具有使截止状态电流值最小化的强有力效应,但是防止因漏区附近电场衰减而含有热载流子产生的变劣的效应低。因此,总是不能有效地在包括工作条件不同的多个集成电路的半导体器件、例如有源矩阵式液晶显示器件中,用相同结构来形成所有TFT。特别是在高性能的结晶硅TFT这些问题更为突出,并且有源矩阵式液晶显示器件要求具有更高的性能。

为了实现大尺寸的有源矩阵式液晶显示器件,已经考虑使用铝(Al)和铜(Cu)作为布线材料,但是这样存在诸如耐蚀性和耐热性差的缺点。因此,这些材料对于形成TFT栅电极并不是优选的,而且不能容易地把这种材料引入TFT的制造工艺。当然可以用其它导电材料形成布线,但是没有什么材料具有象铝(Al)和铜(Cu)这样的低电阻,这就阻碍了大尺寸显示器件的制造。

发明内容

为了解决上述问题,本发明的构成在于一种半导体器件,在同一衬底上具有显示区中的象素TFT和围绕显示区设置的驱动电路TFT,其中象素TFT和驱动电路TFT具有由第一导体层形成的栅电极,栅电极通过连接器与由第二导体层形成的栅极布线电接触,连接器设置在象素TFT和驱动电路TFT的沟道形成区之外。

本发明的另一种构成在于一种半导体器件,在同一衬底上具有显示区中的象素TFT和围绕显示区设置的驱动电路TFT,其中象素TFT和驱动电路TFT具有由第一导体层形成的栅电极,通过设置在象素TFT和驱动电路TFT的沟道形成区之外的连接器、栅电极与由第二导体层形成的栅极布线电接触,象素TFT的LDD区设置成不与象素TFT的栅电极交叠,驱动电路的第一n-沟道TFT的LDD区设置成与第一n-沟道TFT的栅电极交叠,驱动电路的第二n-沟道TFT的LDD区设置成至少其一部分与第一n-沟道TFT的栅电极交叠。

在本发明的这种构型中,第一导体层具有导体层(A)、导体层(B)和导体层(C),导体层(A)含有氮和选自钽、钨、钛和钼之中的至少一种元素,导体层(B)形成在导体层(A)上并且主要由选自钽、钨、钛和钼之中的至少一种元素组成,导体层(C)形成在导体层(B)不与导体层(A)接触的区域并且含有氮和选自钽、钨、钛和钼之中的至少一种元素,而第二导体层具有导体层(D)和导体层(E),导体层(D)主要由铝或铜组成,导体层(E)主要由选自钽、钨、钛和钼之中的至少一种元素组成,导体层(C)和导体层(D)在连接器接触。导体层(B)含有氩作为添加元素,导体层(B)中的氧浓度是30ppm以下。

为了解决上述问题,本发明的半导体器件制造方法是这样一种半导体器件的制造方法,该器件在同一衬底上具有设置在显示区的象素TFT和围绕显示区设置的驱动电路TFT,该方法包括以下步骤,由第一导体层形成用于象素TFT和驱动电路TFT的栅电极,由第二导体层形成连接于栅电极的栅极布线,其中栅电极和栅极布线通过设置在象素TFT和驱动电路TFT的沟道形成区之外的连接器连接。

本发明的半导体器件制造方法还是这样一种半导体器件的制造方法,该器件在同一衬底上具有设置在显示区的象素TFT和围绕显示区设置的驱动电路TFT,该方法包括,第一步骤,向形成驱动电路的第一和第二n-沟道TFT半导体层选择地添加n-型杂质元素,达到2×1016~5×1019原子/cm3的浓度范围,第二步骤,由第一导体层形成用于象素TFT和驱动电路TFT的栅电极,第三步骤,向形成驱动电路的p-沟道TFT半导体层选择地添加p-型杂质元素,达到3×1020~3×1021原子/cm3的浓度范围,第四步骤,向形成驱动电路的第一和第二n-沟道TFT半导体层和形成象素TFT的半导体层中选择地添加n-型杂质元素,达到1×1020~1×1021原子/cm3的浓度范围,第五步骤,至少采用所述n-沟道TFT的栅电极作为掩模,向象素TFT的半导体层选择地添加n-型杂质元素,达到1×1016~5×1018原子/cm3的浓度范围,第六步骤,由第二导体层形成用于象素TFT和驱动电路TFT的栅极布线,其中栅电极和栅极布线通过设置在象素TFT和驱动电路TFT的沟道形成区之外的连接器连接。

根据本发明的半导体器件的制造方法,

通过如下步骤形成第一导体层,形成含有氮和选自钽、钨、钛和钼之中的至少一种元素的导体层(A),在导体层(A)上形成导体层(B)并且主要由选自钽、钨、钛和钼之中的至少一种元素组成,在导体层(B)不与导体层(A)接触的区域上形成导体层(C)并且含有氮和选自钽、钨、钛和钼之中的至少一种元素;通过如下步骤形成第二导体层,至少形成主要由铝和铜组成的导体层(D),并形成主要由选自钽、钨、钛和钼之中的至少一种元素组成的导体层(E),导体层(C)和导体层(D)在连接器连接。导体层(A)可以在氩气和氮气或氨的混合气氛中通过溅射法形成,采用主要由选自钽、钨、钛和钼之中的至少一种元素组成的靶,最好通过在氧浓度为1ppm以下的氮气气氛中,对导体层(B)进行热处理来形成导体层(C)。也可以在氧浓度为1ppm以下的氮气等离子体气氛中,对导体层(B)进行热处理来形成导体层(C)。

附图说明

图1A-1D是象素TFT、存储电容器和驱动电路TFT的制造步骤的剖面图。

图2A-2D是象素TFT、存储电容器和驱动电路TFT的制造步骤的剖面图。

图3A-3D是象素TFT、存储电容器和驱动电路TFT的制造步骤的剖面图。

图4A-4C是象素TFT、存储电容器和驱动电路TFT的制造步骤的剖面图。

图5是象素TFT、存储电容器和驱动电路TFT的剖面图。

图6A-6C是象素TFT、存储电容器和驱动电路TFT的制造步骤的顶视图。

图7A-7C是象素TFT、存储电容器和驱动电路TFT的制造步骤的顶视图。

图8A-8C是驱动电路TFT的制造步骤的顶视图。

图9A-9C是象素TFT的制造步骤的顶视图。

图10是液晶显示器件的I/O接线端和布线电路布局的顶视图。

图11是液晶显示器件的结构剖面图。

图12是液晶显示器件的结构透视图。

图13是显示区的象素顶视图。

图14是用于液晶显示器件的电路框图。

图15A-15C是栅电极和LDD区之间位置关系的一组视图。

图16A-16C是栅电极和栅极布线之间连接的一组视图。

图17A-17E是半导体器件实例的一组视图。

图18A和18B分别是EL显示器件的顶视图和剖面图。

图19A和19B是EL显示器件的象素部位的剖面图。

图20A和20B是EL显示器件的象素部位电路图的顶视图。

图21A-21C是EL显示器件的象素部位的电路图。

图22是由透射电镜摄取的栅电极和栅极布线的接触部位的剖面照片。

图23是由透射电镜摄取的栅电极(Ta)和栅极布线(Al-Nd)的界面的剖面照片。

图24A和24B是VG-ID特性和TFT的热偏置应力实验的研究结果。

图25A和25B是信号输出段和接线端之间的波形差,其中25A展示了波形的上沿,25B展示了波形下沿。

图26A和26B是棚电极和栅极布线的接触电阻的计算模拟。

具体实施方式

[实施模式1]

以下将参考图1-5说明本发明的实施例。以下的详细说明将涉及工艺的各步骤,由此在同一衬底上制造显示区中的象素TFT和围绕显示区形成的驱动电路TFT。但是为使说明简明,驱动电路将以移位寄存电路,作为基本电路的CMOS电路例如缓冲电路,和形成取样电路的n-沟道TFT来说明。

对于图1A,可以采用低碱玻璃衬底或石英衬底作为衬底101。在此实施例中采用低碱玻璃。可以在比玻璃形变温度低约10-20℃的温度下提前进行热处理。在形成TFT的衬底101的表面上形成基膜102,例如氧化硅膜、氮化硅膜或氮氧化硅膜,以便防止杂质从衬底101扩散。例如,采用等离子体CVD法,形成厚100nm的由SiH4,NH3和N2O制成的氮氧化硅膜,和厚200nm的由SiH4和N2O制成的氮氧化硅膜的层叠体。

接着,采用公知方法例如等离子体CVD或溅射,形成厚20-150nm(最好是30-80nm)的非晶结构的半导体膜103a。在此实施例中,采用等离子体CVD形成厚55nm的非晶硅膜。具有非晶结构的半导体膜包括非晶半导体膜和微晶半导体膜,也可以采用具有非晶结构的化合物半导体膜,例如非晶硅-锗。由于基膜102和非晶硅膜103a可以采用相同的膜形成方法来形成,所以可连续形成。形成基膜之后,通过从空气气氛中将其一次去除可以防止表面沾污,于是降低了TFT性能的波动和制造的TFT的阈值电压的变化(图1A)。

然后采用公知的晶化技术,从非晶硅膜103a形成结晶硅膜103b。例如,可以采用激光晶化法或热晶化法(固相生长法),这里,根据日本专利申请公开7-130652公开的技术,通过采用催化剂的晶化方法形成结晶硅膜103b。晶化步骤之前,虽然应根据非晶硅膜的含水量而定,但最好在400-500℃进行约1小时的热处理,在晶化之前把含水量降低到5at%以下。非晶硅膜的晶化引起原子的重排,形成更紧密的形式,从而使制成的结晶硅膜的厚度,从初始非晶硅膜的厚度(在此实施例中是55mm)减少约1-15%(图1B)。

然后把结晶硅膜103b分离成岛状段,形成岛状半导体层104-107。然后采用厚50-100nm的氧化硅膜,通过等离子体CVD或溅射形成掩模层108(图1C)。

设置光刻胶掩模109,按约1×1016~5×1017原子/cm3的浓度,添加硼(B)作为p-型杂质,目的在于限制形成n-沟道TFT的岛状半导体层104-107的阈值电压。可以采用离子掺杂法完成硼(B)的添加,或者可以在非晶硅膜的形成的同时添加。虽然添加硼(B)并不是必不可少的,但半导体层110-112最好形成为添加有硼(B),以便把n-沟道TFT的阈值电压保持在预定范围(图1D)。

为了形成驱动电路的n-沟道TFT的LDD区,向岛状半导体层110、111选择地添加n-型杂质元素。为此目的提前形成光刻胶掩模113-116。所用的n-型杂质元素可以是磷(P)或砷(As),在此例中采用离子掺杂法,使用磷化氢(PH3)来添加磷(P)。形成的杂质区117、118的磷(P)浓度可以在2×1016~5×1019原子/cm3的范围。在整个本说明书中,这里形成的杂质区117-119中的n-型杂质元素的浓度将表达为(n-)。杂质区119是用于形成象素矩阵电路的存储电容器的半导体层,此区中同样添加相同浓度的磷(P)(图2A)。

随后的步骤是通过氢氟酸等去除掩模层108,并且激活在图1D和图2A添加的杂质元素。可以通过在氮气气氛中、500-600℃下热处理1-4小时,或者通过激光激活法,进行激活。这些也可以组合进行。在此实施例中,采用激光激活法,采用KrF准分子激光(248nm波长)形成线性光束,按5-50Hz的振荡频率和100-500mJ/cm2的能量密度扫描,具有80-98%的线性光束重叠,对其上已形成岛状半导体层的整个衬底进行处理。对激光照射条件没有特别限制,可以由操作者适当设置。

然后采用等离子体CVD或溅射,使用含硅绝缘膜形成厚10-150nm的栅极绝缘膜120。例如,形成厚120nm的氮氧化硅膜。栅绝缘膜也可以是其它含硅绝缘膜的单层或多层结构(图2B)。

然后用第一导体层形成栅电极。此第一导体层可以形成为单层,但是如果需要也可以具有两层或三层的层叠结构。在此实施例中,层叠由导电金属氮化物膜制成的导体层(A)121和由金属膜制成的导体层(B)122。导体层(B)122可以由选自钽(Ta)、钛(Ti)、钼(Mo)和钨(W)之中的一种元素形成,或者主要由这些元素之一组成的合金形成,或者包括这些元素的组合的合金膜(一般是Mo-W合金膜或Mo-Ta合金膜)形成,导体层(A)121由氮化钽(TaN)、氮化钨(WN)、氮化钛(TiN)或氮化钼(MoN)形成。作为导体层(A)121的替换材料,可以使用硅化钨、硅化钛或硅化钼。导体层(B)可以具有降低的杂质浓度,目的在于降低电阻,特别是氧浓度在30ppm以下是满意的。例如,氧浓度在30ppm以下的钨(W)可以实现20μΩcm以下的电阻率。

导体层(A)121可以是10-50nm(最好是20-30mm),导体层(B)122可以200-400nm(最好是250-350nm)。在此实施例中,采用厚30nm的氮化钽膜作为导体层(A)121,采用350nm的Ta膜作为导体层(B)122.两者均通过溅射形成。在采用溅射的此膜形成中,向Ar溅射气体添加适量的Xe或Kr能够减轻形成膜的内应力,于是防止膜剥落。虽然没有示出,但是可以在导体层(A)121下有效地在形成掺杂有磷(P)的厚约2-20nm的硅膜。这样能够改善粘附性,防止其上形成的导体膜氧化,同时还能够防止导体层(A)或导体层(B)中的微量碱金属元素向栅绝缘膜120扩散(图2C)。

然后形成光刻胶掩模123-127,一起腐蚀导体层(A)121和导体层(B)122,形成栅电极128-131和电容器布线132。栅电极128-131和电容器布线132包括集成形成的导体层(A)构成的段128a-132a和导体层(B)构成的段128b-132b。这里,在驱动电路中形成的栅电极129、130是这样形成的,它们借助棚绝缘层120与杂质区117、118的部分交叠(图2D)。

随后是添加p-型杂质元素的步骤,形成驱动电路的p-沟道TFT源区和漏区。这里,采用栅电极128作为掩模,形成自对准杂质区。其中形成有n-沟道TFT的区此时被光刻胶掩模133覆盖。通过采用乙硼烷(B2H6)的离子掺杂法形成杂质区134。此区中的硼(B)浓度是3×1020-3×1021原子/cm3。在本说明书中,这里形成的杂质区134中的p-型杂质元素浓度将表示为(p+)(图3A)。

接着,起源区或漏区作用的杂质区形成在n-沟道TFT中。形成光刻胶掩模135-137,添加n-型杂质元素形成杂质区138-142。这是通过采用磷化氢(PH3)的离子掺杂法完成的,此区中的磷(P)浓度在1×1020-1×1021原子/cm3的范围。在本说明书中,这里形成的杂质区138-142中的n-型杂质元素浓度将表示为(n+)(图3B)。

杂质区138-142早已含有在在先步骤中添加的磷(P)或硼(B),但是由于相对而言添加了足够高浓度的磷(P),所以在在先步骤中添加的磷(P)或硼(B)的影响可以忽略不计。由于向杂质区138添加的磷(P)的浓度是在图3A添加的硼(B)浓度的1/2-1/3,所以可以保证p-型导电型,从而对TFT的性能没有影响。

随后的步骤是添加n-型杂质,在象素矩阵电路的n-沟道TFT中形成LDD区。这里,采用栅电极131作为离子掺杂法的n-型杂质元素的自对准添加的掩模。添加的磷(P)浓度是1×1016-5×1018原子/cm3,添加浓度低于在图2A、3A和3B中添加的杂质元素浓度基本仅形成杂质区143、144。在本说明书中,在这些杂质区143、144中的n-型杂质元素的浓度将表示为(n-)(图3C)。

随后是热处理的步骤,激活按其各个浓度添加的n-型或p-型杂质元素。此步骤可以采用炉退火法、激光退火法或快速热退火法(RTA法)完成。这里,采用炉退火法完成激活步骤。在氧浓度不大于1ppm的氮气气氛中进行热处理,最好不大于0.1ppm,在400-800℃下,一般在500-600℃,对于本实施例,是在550℃进行4小时热处理。当采用耐热材料例如石英衬底作为衬底101时,即使在800℃进行1小时的热处理,也可以激活杂质元素,在添加了杂质元素的杂质区和沟道形成区之间形成满意的键合。

在热处理中,从形成栅电极128-131和电容器布线132的金属膜128b-132b的表面,形成厚5-80nm的导体层(C)128c-132c。例如,当导体层(B)128b-132b是钨(W)时,可以形成氮化钨(WN),而采用钽(Ta)时可以形成氮化钽(TaN)。通过把栅电极128-131暴露于含氮等离子体气氛,采用氮气或氨气,按相同方式形成导体层(C)128c-132c。还在含3-100%氢的气氛中,在300-450℃进行1-12小时的热处理,进行岛状半导体层的氢化。此步骤是通过热激发氢终止半导体层的悬挂键的步骤。作为氢化的另一种方式也可以进行等离子体氢化(采用等离子体激发氢)。

当通过采用催化剂元素从非晶硅膜晶化的方法制备岛状半导体层时,在岛状半导体层中残留微量催化剂元素。虽然即使在这种条件也能够完成TFT,但至少从沟道形成区去除残留的催化剂元素则更好。去除催化剂元素的一种方式是利用磷(P)的吸气效应。吸气所必需的磷(P)浓度是在与图3B形成的杂质区(n+)相同的水平上,这里进行的激活步骤的热处理可从n-沟道TFT和p-沟道TFT的沟道形成区中吸取催化剂元素(图3D)。

图6A和图7A是到目前为止的TFT的顶视图,其中剖面A-A’和剖面C-C’对应于图3D的A-A’和C-C’。剖面B-B’和剖面D-D’对应于图8A和图9A的剖面图。图6A-6C和图7A-7C的顶视图省略了栅电极膜,但是到此步骤为止,至少栅电极128-131和电容器布线132已形成在岛状半导体层104-107上,如图所示。

完成激活和氢化步骤之后,形成第二导体层用做栅极布线。这种第二导体层可以用导体层(D)和导体层(E)形成,导体层(D)主要由作为低电阻材料的铝(Al)或铜(Cu)组成,导体层(E)由钛(Ti)、钽(Ta)、钨(W)、或钼(Mo)制成。在此实施例中,导体层(D)145是含0.1-2wt%钛(Ti)的铝(Al)膜,导体层(E)146是钛(Ti)膜。导体层(D)145可以形成为200-400nm(最好是250-350nm),导体层(E)146可以形成为50-200nm(最好是100-150nm)(图4A)。

导体层(E)146和导体层(D)145进行腐蚀处理,形成连接栅电极的栅极布线,如此形成栅极布线147、148和电容器布线149。腐蚀处理首先通过采用SiCl4、Cl2和BCl3的混合气体的干法腐蚀法,从导体层(E)的表面经过导体层(D)到达一半的去除,然后采用磷酸基腐蚀溶液进行湿法腐蚀,去除导体层(D),这样可以在形成栅极布线的同时保持以基底层的选择加工。

图6B和图7B是这种状态的顶视图,其中剖面A-A’和剖面C-C’对应于图4B中的A-A’和C-C’。剖面B-B’和剖面D-D’对应于图8B和图9B的B-B’和D-D’。在图6B和7B中,部分栅极布线147、148交叠,已与部分栅电极128、129、131电接触。这种状态清楚地显示在对应于剖面B-B’和D-D’的图8B和9B的剖面结构图,其中形成第一导体层的导体层(C)和形成第二导体层的导体层(D)电接触。

采用氧化硅膜或氮氧化硅膜,形成厚500-1500nm的第一层间绝缘膜150,之后形成接触孔到达每个岛状半导体层中形成的源区或漏区,形成源布线151-154和漏布线155-158。虽然这里没有示出,但是在此实施例中,电极具有三层层叠结构,是通过溅射连续形成的100nmTi膜、300nm的含Ti铝膜和150nm的Ti膜。

接着,形成厚50-500nm(一般是100-300nm)的氮化硅膜、氧化硅膜或氮氧化硅膜,作为钝化膜159。在此状态的氢化处理对TFT性能提高有利。例如,可以在含3-100%氢的气氛中、300-450℃进行1-12小时的热处理,或者通过使用等离子体氢化法可以达到类似的效果。这里,在要形成用于象素电极和漏布线的连接的接触孔的位置,在钝化膜159中形成开口(图4C)。

图6C和图7C展示了这种情况的顶视图,其中剖面A-A’和剖面C-C’对应于图4C中的A-A’和C-C’。剖面B-B’和剖面D-D’对应于图8C和图9C中的B-B’和D-D’。图6C和图7C没有展示第一层间绝缘膜,但是岛状半导体层104、105、107的源区和漏区(未示出)中的源区布线151、152、154和漏区布线155、156、158,借助形成在第一层间绝缘膜的接触孔来连接。

接着,形成厚1.0-1.5μm的有机树脂制成的第二层间绝缘膜160。所用的有机树脂可以是聚酰亚胺、丙稀酸、聚酰胺、聚酰亚胺氨化物、BCB(苯并环丁稀)等。这里,对衬底涂敷之后,采用热聚合型聚酰亚胺,在300℃烧结形成。然后在第二层间绝缘膜160中形成到达漏区布线158的接触孔,并形成象素电极161、162。使用的象素电极,在透射液晶显示器件的情形可以是透明导电膜,或者在反射液晶显示器件的情形可以金属膜。在此实施例中采用透射液晶显示器件,因此通过溅射形成厚100nm的氧化铟锡(ITO)膜(图5)。

按此方式制成在同一衬底上具有驱动电路TFT和显示区象素TFT的基片。在驱动电路上形成p-沟道TFT201、第一n-沟道TFT202和第二n-沟道TFT203,在显示区上形成象素TFT204和存储电容器205。在本说明书中,这种基片将简称为有源矩阵基片。

驱动电路的p-沟道TFT201在岛状半导体层104中具有沟道形成区206、源区207a、207b和漏区208a、208b。第一n-沟道TFT202在岛状半导体层105中具有沟道形成区209、与栅电极129交叠LDD区210(以下这种LDD区将称为Lov)、源区211和漏区212。这种Lov区在沟道长度方向的长度是0.5-3.0μm,是1.0-1.5μm更好。第二n-沟道TFT203在岛状半导体层106中具有沟道形成区213、LDD区214、215、源区216和漏区217。这些LDD区由Lov区和不与栅电极130交叠的LDD区(以下这种LDD区将称为Loff)形成,这种Loff区在沟道长度方向的长度是0.3-2.0μm,是0.5-1.5μm更好。象素TFT204在岛状半导体层107中具有沟道形成区218、219、Loof区220-223、源区和漏区224-226。Loff区在沟道长度方向的长度是0.5-3.0μm,是1.5-2.5μm更好。电容器布线132、149和由与栅绝缘膜相同材料制成的绝缘膜连接于象素TFT204的漏区226,存储电容器205由添加n-型杂质元素的半导体层227形成。图5中象素TFT204具有双栅极结构,但是也可以是单栅极结构,采用具有多栅电极的多栅极结构没有问题。

这样,本发明根据对象素TFT和驱动电路的技术要求,优化了每个电路的TFT结构,从而可改善半导体器件的工作性能和可靠性。此外,通过用耐热导电材料形成栅电极,可以有助于LDD区和源区和漏区的激活,从而通过用低电阻材料形成栅极布线来充分降低布线电阻。这样可以应用于在4英寸以上级别的显示区(屏幕尺寸)。

[实施模式2]

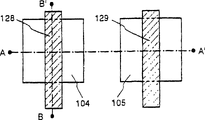

图16A-16C展示了栅电极和栅极布线的另一个实施例。按与实施模式1所示步骤相同的方式形成图16中的栅电极和栅极布线,形成在岛状半导体层901和栅绝缘膜902上

图16A中,作为栅电极的第一导体层,是由氮化钽(TaN)、氮化钨(WN)、氮化钛(TiN)或氮化钼(MoN)形成的导体层(A)903。导体层(B)904由选自钽(Ta)、钛(Ti)、钼(Mo)和钨(W)之中的元素,或者主要由这些元素组成的合金或包括这些元素组合的合金膜形成的,而导体层(C)905按与实施模式1相同的方式形成在表面上。导体层(A)903可以是10-50nm(最好是20-30nm),导体层(B)904可以是200-400nm(最好是250-350nm)。通过层叠导体层(D)906和位于其上的导体层(E)907形成作为栅极布线的第二导体层,导体层(D)906主要由作为低电阻材料的铝(Al)或铜(Cu)构成,导体层(E)907由钛(Ti)或钽(Ta)形成。由于通过应力迁移和电迁移而使铝(Al)和铜(Cu)快速扩散,所以氮化硅膜908必须形成为厚50-150nm,以便覆盖第二导体层。

图16B展示了按与实施模式1相同的方式制备的栅电极和栅极布线,掺杂了磷(P)的硅膜909形成在栅电极之下。掺杂了磷(P)的硅膜909具有防止栅电极中的微量碱金属元素扩散进入栅绝缘膜的作用,有利于保证TFT可靠性。

图16C是在形成栅电极的第一导体层上形成掺杂磷(P)的硅膜910的例子。掺杂磷(P)的硅膜是电阻大于其它导体金属材料的材料,但是通过用铝(Al)或铜(Cu)形成由栅极布线构成的第二导体层,可以应用于大面积的液晶显示器件。这里,栅极布线可以是三层结构,通过达100nm的Ti膜911、达300nm的含Ti铝(Al)膜912和达150nm的Ti膜913来形成,避免铝(Al)膜和掺杂磷(P)的硅膜之间直接接触,提供耐热性。

[实施模式3]

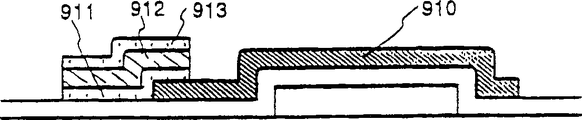

图15A-15C是根据本发明的TFT的结构示意图,展示了TFT中的栅电极和LDD区之间的位置关系,这种TFT具有半导体层沟道形成区、LDD区、位于半导体层上的栅极绝缘膜和位于棚极绝缘膜上的栅电极。

图15A展示的结构设置了具有沟道形成区209、LDD区210和漏区212的半导体层,和形成于其上的栅极绝缘膜120和栅电极129。LDD区210是通过栅极绝缘膜120与栅电极129交叠设置的Lov。Lov具有衰减靠近漏区产生的强电场的功能,同时防止热载流子引起的退化,能够适用于包括移位寄存器电路、电平漂移电路、缓冲电路等的驱动电路的n-沟道TFT。

图15B展示的结构设置了具有沟道形成区213、LDD区215a、215b和漏区217的半导体层,和形成于半导体层上的栅极绝缘膜120和栅电极130。LDD区215a设置成通过栅极绝缘膜120与栅电极130交叠。而且,LDD区215b是不与栅电极130交叠设置的Loff。Loff具有降低截止电流值的功能,设置有Lov和Loff的结构能够防止热载流子引起的退化,同时还能够降低截止电流值,从而可以适用于驱动电路的取样电路的n-沟道TFT。

图15C展示了设置有沟道形成区219、LDD区223和漏区226的半导体层。LDD区223是不通过栅极绝缘膜120与栅电极131交叠设置的Loff,其可以有效地降低截止电流值,因此适合用于象素TFT。象素TFT的LDD区223中的n-型杂质浓度最好比驱动电路的LDD区210、215中的浓度小1/2-1/10。

[实施模式4]

在此实施例中,将说明从有源矩阵衬底制备有源矩阵型液晶显示器件的步骤。如图11所示,按实施模式1制备的如图5所示状态下,在有源矩阵衬底上形成对准膜601。对于大多数液晶显示器件,常常采用聚酰亚胺树脂作为对准膜。在相反侧上的对置衬底602上,形成光屏蔽膜603、透明导体膜604和对准膜605。形成对准膜之后进行摩擦处理,以便按一致的预置倾角使液晶分子取向。通过公知的单元接合步骤,经过封接材料或衬垫(未示出),把象素矩阵电路和与其上已经形成了CMOS电路的有源矩阵对置的衬底装配在一起。然后,在两个衬底之间注入液晶材料606,采用密封剂(未示出)完成全部封接。使用的液晶材料可以是任何公知的液晶材料。这就制成了如图11所示的有源矩阵型液晶显示器件。

以下将参考图12的透视图和图13的顶视图,说明这种有源矩阵型液晶显示器件。图12和13中所用的相同标号对应于图1-5和图11的剖面结构图。沿图13中的E-E’的剖面结构对应于图5中的象素矩阵电路的剖面图。

图12中,有源矩阵衬底由形成在玻璃衬底101上的显示区306、扫描信号驱动电路304和图象信号驱动电路305构成。象素TFT204设置显示区,围绕其设置的驱动电路由CMOS电路构成。扫描信号驱动电路304和图象信号驱动电路305分别通过栅极布线148和源区布线154连接到象素TFT204。而且,FPC731连接于外I/O接线端734,并且通过输入布线302、303连接到每个驱动电路。

图13的顶视图展示了显示区306的大约一个象素部分。栅极布线148借助栅极绝缘膜(未示出)与其之下的半导体层107交叉。半导体层上未示出的还有源区、漏区和作为n-区的Loff区。连接器163存在于源区布线154和源区224之间,连接器164存在于漏区布线158和漏区226之间,连接器165存在于漏区布线158和象素电极161之间。存储电容器205形成的区中,从象素TFT204的漏区226延伸的半导体层227借助栅电极膜与电容器布线132、149交叠。

上面用实施模式1的结构说明了本实施例的有源矩阵型液晶显示器件,但是也可以采用与实施模式2的结构的任意组合制备有源矩阵液晶显示器件。

[实施模式5]

图10是液晶显示器件的I/O接线端、显示区和驱动电路的排列示意图。显示区306具有按矩阵形式交叉的m个栅极布线和n个源区布线。例如,当象素密度是VGA(视频图形阵列)时,形成480个栅极布线和640个源区布线,对于XGA(扩展图形阵列),形成768个栅极布线和1240个源区布线。在13英寸级别显示的情况,显示区的屏幕尺寸具有340mm的对角线长度,在18英寸级别显示的情况是460mm。为了实现这种液晶显示器件,必须形成低电阻材料的栅极布线,如实施模式1和实施模式2所示。

围绕显示区306设置扫描信号驱动电路304和图象信号驱动电路305。由于随着显示区屏幕尺寸的增大,这些驱动电路栅极布线的长度也必须较长,所以最好由低电阻材料形成,如实施模式1和实施模式2所示,以便实现大尺寸屏幕。

根据本发明,从输入端301连接于每个驱动电路的输入布线302、303,可以由与栅极布线相同的材料形成,它们能够有助于低的布线电阻。

[实施模式6]

图14是实施模式1或实施模式2所示有源矩阵衬底的结构视图,用于直观式显示器件结构。此实施例的有源矩阵衬底具有图象信号驱动电路1001、扫描信号驱动电路(A)1007、扫描信号驱动电路(B)1011、预充电电路1012和显示区1006。在本说明书中,术语“驱动电路”将包括图象信号驱动电路1001和扫描信号驱动电路(A)1007。

图象信号驱动电路1001设置有移位寄存器电路1002、电平漂移电路1003、缓冲电路1004和取样电路1005。扫描信号驱动电路(A)1007设置有移位寄存器电路1008、电平漂移电路1009和缓冲电路1010。扫描信号驱动电路(B)1011也具有相同的结构。

移位寄存器电路1002、1008具有5-16V的驱动电压(一般是10V),形成这种电路的CMOS电路的n-沟道TFT适合具有如图5中202所示的结构。电平漂移电路1003、1009和缓冲电路1004、1010具有高达14-16V的驱动电压,对于移位寄存器电路,包括图5中的n-沟道TFT的CMOS电路是适合的。在这些电路中,用多栅极结构形成栅电极有利于提高耐电压能力和改善电路可靠性。

取样电路1005具有14-16V的驱动电压,但是由于必须降低截止电流值,同时用交替反向的极性进行驱动,所以含有图5的n-沟道TFT203的CMOS电路是适合的。图5仅展示了n-沟道TFT,但是在实际取样电路中是与p-沟道TFT组合形成。这里,p-沟道TFT适合具有同一图中201所示的结构。

象素TFT204具有14-16V的驱动电压,从降低功耗的来看,要求截止电流值比取样电路更为降低,因此该结构具有的LDD(Loff)区最好没有按象素TFT204那样方式与栅电极交叠。

根据实施模式1所示的步骤制备TFT可以容易地实现此实施例的结构。在此实施例中,仅展示了用于显示区和驱动电路的结构,但是在实施模式1的步骤之后,可以在同一衬底上形成信号处理电路,例如信号分割电路、分谐波电路、D/A转换器、γ-校正电路、运算放大器电路、存储器电路或计算处理电路,或逻辑电路。这样,本发明能够在同一衬底上实现包括象素矩阵电路及其驱动电路的半导体器件,例如装配信号驱动电路和象素矩阵电路的半导体器件。

[实施模式7]

根据本发明制备的有源矩阵衬底和液晶显示器件可以用于各种光电器件。本发明也可以用于任何含有这种光电器件作为显示介质的电子设备。作为电子设备这里可以列举个人计算机,数字照相机,录象机,便携式信息终端(移动计算机,蜂窝电话,电子书籍等),导航系统等。这些之中的例子如图17A-17E所示。

图17A是个人计算机,其由设置有微处理器或存储器的主体2001、图象输入器件2002、显示器件2003和键盘2004构成。可以根据本发明形成显示器件2003或其他信号处理电路。

图17B是录象机,由主体2101、显示器件2102、声音输入器件2103、操作开关2104、电池2105和图象接收器件2106构成。本发明可以用于显示器件2102或其他信号驱动电路。

图17C是便携式数字终端,由主体2201、图象输入器件2202、图象接收器件2203、操作开关2204和显示器件2205构成。本发明可以用于显示器件2205或其他信号驱动电路。

图17D是用于记录了节目的记录介质(以下简称为记录介质)的播放器,由主体2401、显示器件2402、扬声器2403、记录介质2404和操作开关2405构成。使用的记录介质可以是DVD(数字通用盘)或压缩盘(CD),可以重放音乐节目和图象显示,以及通过互连网显示视频节目(或TV节目)的数据。本发明可以满意地用于显示器件2402或其他信号驱动电路。

图17E是数字照相机,由主体2501、显示器件2502、取景器2503、操作开关2504和图象接收器(未示出)构成。本发明可以用于图象器件2502或其他信号驱动电路。

这样,本发明的应用范围极宽,能够用于各种领域的电子设备。这些实施例的电子设备也可以采用实施模式1-6的组合来实现。

[实施模式8]

在本实施模式中,将说明由类似于实施模式1的有源矩阵衬底,制造采用电致发光(EL)材料的自发发光式显示屏(以下称为EL显示器件)的例子。图18A展示了EL显示屏的顶视图。图18A中,参考标号10是衬底,11是象素段,12是源区侧驱动电路,13是栅电极侧驱动电路,每个驱动电路通过布线14-16到达FPC17,然后连接于外部器件。

图18B展示了在图18A的线A-A’的剖面。这里对置板80至少位于象素段之上,最好在驱动电路和象素段上。对置板80被封接材料19粘附在有源矩阵衬底上,其上形成TFT和采用EL材料的自发发光层。填料(图中未示出)混合在封接材料19中,两个衬底被这种填料粘附在一起,具有大致均匀的间距。该器件的结构通过封接材料19外侧和FPC17周边上的密封剂81密封。密封剂81使用例如硅树脂、环氧树脂、酚树脂或丁基橡胶等材料。

当有源矩阵衬底10和对置衬底80被封接材料19粘附在一起时,其内形成空隙。用填料83填充该空隙,这种填料83还具有粘附对置板80的作用。PVC(聚氯乙烯)、环氧树脂、硅树脂、PVB(聚乙烯醇缩丁醛)或EVA(乙烯乙酸乙烯酯)可以用做填料83。由于自发发光层的抗湿性较弱,易于退化,最好在填料83内形成干燥剂例如氧化钡,以便能够保持水分吸收效应。而且器件的结构还有在自发发光层上由氮化硅膜或氮氧化硅膜等形成钝化膜,以便防止包括填料83在内的碱性元素产生的腐蚀。

对置板80可以采用玻璃板、铝板、不锈钢板、FRP(玻璃纤维增强塑料)板、PVF(聚氯乙烯)膜、Myler膜(I.E.du Pont de Nemours and Company的商标)、聚酯膜、丙稀酸膜或丙稀酸板。而且,通过使用具有几十μn铝箔与PVF膜或Myler膜TM的夹层结构的片可以提高抗湿性。按此方式,EL元件被密封并与外界气氛屏蔽开。

在图18B中,驱动电路TFT22(注意组合n-沟道TFT和p-沟道TFT的CMOS电路如图所示),和用于象素段的TFT23(注意控制到达EL元件的电流的TFT如此图所示)形成在衬底10和基膜21上。特别是,在这些TFT中,n-沟道TFT设置有构如本实施例所示的LDD区,防止导通电流因热载流子效应而降低,以及性能因第V次漂移或偏置应力而退化。

例如,图5所示的p-沟道TFT201和n-沟道TFT202可以用做驱动电路TFT22。虽然其取决于驱动电压,如果驱动电压是10V以上,则图5的第一n-沟道TFT204或具有相同结构的p-沟道TFT可以用做象素段TFT。虽然第一n-沟道TFT202构成为设置有在漏区侧上与栅电极交叠的LDD,但是当驱动电压小于10V时并不必须这样设置,因为几乎可以忽略因热载流子效应引起的TFT退化。

为了从在图1A-1D状态的有源矩阵衬底制备EL显示器件,包括树脂材料的层间绝缘膜(平坦膜)26形成在源区布线和漏区布线上,包括电连接于象素段TFT23的漏区的透明导体膜的象素电极27形成于其上。氧化铟和氧化锡和化合物(称为ITO)或者氧化铟和氧化锌的化合物可以用做透明导体膜。形成象素电极27之后,形成绝缘膜28,在象素电极27上形成开孔段。

接着,形成自发发光层29。自发发光层29可以是层叠结构或单层结构,其中公知的EL材料(空穴注入层、空穴传送层、发光层、电子传送层或电子注入层)可以自由组合。考虑如何构成时可以采用公知范畴的技术。而且,对于EL材料有小分子材料和聚酯材料。在采用小分子材料的情形使用蒸发方法,在采用聚酯材料的情形可以使用简单方法,例如旋涂法、印刷法或喷墨法等。

可以通过采用阴罩掩模的蒸发法、喷墨法或投放器法形成自发发光层。按这些方式,通过形成每个象素能够发出不同波长的光发光层(发红光层、发绿光层和发蓝光层),可以实现彩色显示。可以采用其它任何方式,例如色彩变化层(CCM)与滤色器组合,发白光层与滤色器组合。不用说也可以采用发单色光的EL显示器件。

形成自发发光层29之后,在顶部形成阴极30。最好尽可能地去除阴极30和自发发光层29之间界面存在的水分和氧。因此必须采取如下措施,例如通过连续膜淀积在真空中形成自发发光层29和阴极30,或者在惰性气氛中形成自发发光层29,然后在不暴露大气的条件下形成阴极30。可以采用多室系统(群工具系统)淀积设备按本实施例进行上述膜淀积。

注意采用LiF(氟化锂)膜和Al(铝)膜的层叠结构用于实施模式8的阴极30。特别是,通过蒸发1nm厚的LiF(氟化锂)膜形成在自发发光层29上,在其上部形成300nm厚的铝膜。不用说,可以使用MgAg电极、公知电极材料。阴极30在参考标号31表示的区域与布线16连接。布线16是电源线,以便为阴极30提供预定的电压,并通过各向异性导电膏材料32与FPC17连接。在FPC17上还形成树脂层80,这段的粘附性得以提高。

为了在参考标号31代表的区域电连接阴极30和布线16,必须在层间绝缘膜26和绝缘膜28中形成接触孔。可以在层间绝缘膜26的腐蚀期间(当形成象素电极接触孔时)和绝缘膜28的腐蚀期间(当形成自发发光层之前形成开口段时)形成接触孔。而且,在腐蚀绝缘膜28时可以在整个过程中的一次发射中对层间绝缘膜26进行腐蚀。在这种情况,接触孔可以具有良好的形状,只要层间绝缘膜26和绝缘膜28是相同树脂材料即可。

布线16穿过封接材料19和衬底10之间的空间(只要用密封剂81封闭即可)与FPC17连接。注意这里的说明是针对布线16,但是其它布线14和15也可以按类似方式穿过封接材料18之下与FPC17电连接。

象素段的更详细剖面结构如图19A和19B所示,顶视图如图20A所示,电路图如图20B所示。在图19A中.设置在衬底2401上的开关TFT2402,按与实施模式1的图5的象素TFT204相同的结构形成。成为2个TFT通过采用双栅电极结构串联的结构,通过在不与栅电极交叠而设置的偏置区中形成LDD可以降低截止电流值。虽然本实施例使用双栅电极结构,但是结构可以是三栅电极结构或者具有更多栅电极的多栅电极结构。

而且,采用如图5所示的第一n-沟道TFT202形成电流控制TFT2403。这种TFT结构是这样的结构,其中与栅电极交叠的LDD仅设置在漏区侧,通过降低寄生电容和栅极与漏区之间的串联电阻,提高了电流驱动器容量。而且从其它观点来看,应用这种结构具有非常重要的意义。由于电流控制TFT是控制流过EL元件的电流量的元件,所以该元件流过大量电流时存在因加热而退化和因热载流子而退化的较大危险。通过设置部分与栅电极交叠的LDD,可以防止电流控制TFT的退化,提高工作可靠性。此时,开关TFT2402的漏区布线35通过布线36与电流控制TFT的栅电极37电连接。参考标号38代表的布线是栅极布线,与开关TFT2402的栅电极39a和39b电连接。

而且,虽然本实施例展示了用于电流TFT2403的单栅极结构,但也可以是串联连接多个TFT多栅极结构。而且,可以是多个TFT并联连接、在效果上分开沟道形成区的结构,其中可以高效地获得热发射。这种结构是针对因加热而退化的有效对策。

如图20A所示,成为电流控制TFT2403的栅电极37的布线,通过在参考标号2404代表的区设置绝缘膜,与电流控制TFT2403的漏区布线40交叠。在参考标号2404代表的区形成电容器。此电容器2404的作用是保持施加于电流控制TFT2403栅电极的电压。漏区布线40连接于电流线(电源线)2501,对其总是施加恒定电压。

在开关TFT2402和电流控制TFT2403上形成第一钝化膜41,在其上形成包括树脂绝缘膜的平坦化膜42。采用平坦化膜42使因TFT产生的平面差平坦化是非常重要的。之后形成的自发发光层是如此之薄,以致存在平面差有时会导致发光缺陷。因此需要在形成象素电极之前进行平坦化处理,以便在尽可能平坦的表面上形成自发发光层。

43代表的是具有高反射率的导电膜制成的象素电极(EL元件的阴极),与电流控制TFT2403的漏区电连接。象素电极43的优选材料是低电阻导电膜,例如铝合金膜、铜合金膜和银合金膜,或者这些膜的层叠膜。不用说,可以使用这些膜与其它导电膜形成层叠结构。由绝缘膜(最好是树脂)制成的边坡44a和44b在其间形成沟槽(对应于象素),在沟槽中形成发光层44。虽然这里仅展示了一个象素,但是可以形成分别对应于R(红)、G(绿)和B(蓝)色的发光层。作为形成发光层的有机EL材料采用π共轭聚酯材料。代表性的聚酯材料包括聚对亚苯基亚乙烯基(PPV)、聚乙烯咔唑(PVK)、和聚氟基材料等。在各种形式的PPV基有机EL材料中,有用的材料例如公开在H.Shenk,H.Becker,O.Gelsen,E.Kluge,W.Kreuder,and H.Spreirzer,“Polymers for Light EmittingDiodes,”Euro Display,Proceedings,1999,pp.33-37,或公开在日本专利申请公开平10-92576。

具体地,采用氰基聚亚苯基亚乙烯基用于发射红光的发光层,采用聚亚苯基亚乙烯基用于发射绿光的发光层,采用聚亚苯基亚乙烯基或聚烷基亚苯基用于发射蓝光的发光层。其适当的膜厚是30-150nm(最好是40-100nm)。而且,上述说明是可用做发光层的有机EL材料,但本发明并不限于此。通过自由组合发光层、电荷输送层和电荷注入层,可以形成自发发光层(用于发光和用于移动载流子发光的层)。代替在本实施例所示例子中用做发光层的聚酯材料,例如可以采用小分子有机EL材料。也可以使用无机材料例如碳化硅,用于电荷输送层和电荷注入层。公知材料可以用做这些元件EL材料和无机材料。

本实施例中的自发发光层具有层叠结构,其中包括PEDOT(聚三苯)或者PAni(聚苯胺)的空穴注入层46层叠在发光层45上。在本实施例的情形,在发光层45产生的光发射向顶面(向上超出TET),这要求阳极具有透光性。透明导电膜可以由氧化铟和氧化锡的化合物形成,或者由氧化铟和氧化锌的化合物形成,优选的材料是能够在尽可能低的温度下形成膜的材料,因为在形成耐热性低的发光层和空穴注入层之后形成透明导电膜。

通过形成阳极47从而制成自发发光元件2045。这里的自发发光元件2045是指由象素电极(阴极)43、发光层45、空穴注入层46和阳极47构成的电容器。如图20A所示,象素电极43几乎延伸在全部象素区域上,从而全部象素起自发发光元件的作用。因此发光效率非常高,所以图象显示明亮。

在此实施例中,在阳极47上还形成第二钝化膜48。优选的第二钝化膜48是氮化硅膜或氮氧化硅膜。此第二钝化膜的目的在于使自发发光元件与外界封闭,防止有机EL材料因氧化而退化,以及抑制有机EL材料放气。这样可以提高EL显示器件的可靠性。

如上所述,本实施例的EL显示屏包括象素段,象素段包括如图20A所示的结构的象素,具有足够低的截止电流值的开关TFT,和抵抗热载流子能力强的电流控制TFT。如此获得的是具有高可靠性并且图象显示优异的EL显示屏。

图19B展示了自发发光层转变的例子。采用与图5的p-沟道TFT相同结构形成电流控制TFT2601。制备方法可以优选实施模式1。此实施例中采用透明导电膜用做象素电极(阳极)50。具体地,采用由氧化铟和氧化锌的化合物制成的导电膜。不用说,由氧化铟和氧化锡的化合物制成的导电膜也可以采用。

形成绝缘膜制成的边坡51a和51b之后,通过施加溶液形成包括聚乙烯咔唑的发光层52。在其上形成包括乙酰丙酮钾(表示为acacK)的电子注入层53和由铝合金制成的阴极54。此时,阴极54还起钝化膜的作用。如此形成EL元件2602。在此实施例中,发光层52中产生的光被发射朝向形成了TFT的衬底,如图中箭头所示。在采用本实施例的结构的情形,最好由p-沟道TFT形成电流控制TFT。

本实施例所示的EL显示器件可以用做实施模式7的电子器件的显示段。

[实施模式9]

本实施例展示在图21A-21C,这些例子中象素具有不同于图20B的电路图的结构。在此实施例中,参考标号2701代表开关TFT2702的源区布线,2703代表开关TFT2702的栅极布线,2704代表电流控制TFT,2705代表电容器,2706和2708代表电流供给线,2707代表EL元件。

图21A展示了两个象素共用电流供给线2706的例子。换言之,此例的特征在于与电流供给线2706对称地形成两个象素。此时,电流供给线的数量可以减少,可以进一步提高象素段的确定性(definition)。

图21B展示了电流供给线2708布置成与栅极布线2703平行的例子。虽然电流供给线如此布置,不与图21B中的栅极布线2703交叠,但是如果这些线形成在不同的层,则两条线可以通过绝缘膜彼此交叠。此时,电流供给线2708和栅极布线2703可以共用其占据的区域,进一步提高象素段的确定性。

图21C所示例子的特征在于,电流供给线2708的布置与图21B的结构类似,与栅极布线2703平行,而且两个象素对称于电流供给线2708形成。使电流供给线2708与栅极布线2703之一交叠,这样的布置也是有效的。此时,可以减少电流供给线的数量,进一步提高象素段的确定性。虽然设置电容器2705以便保持在图21A和21B的电流控制TFT2704的栅电极施加的电压,但也可以省略电容器2705。

由于如图19A所示的本发明的n-沟道TFT用做电流控制TFT2704,所以其具有的LDD区设置成通过插入的栅极绝缘膜与栅电极交叠。一般称为寄生电容的栅极电容形成在此交叠区,本实施例的特征在于使用寄生电容代替电容器2705。由于此寄生电容的电容量因栅电极和LDD区的交叠面积而变化,所以包含在交叠区的LDD区的长度决定了其电容量。而且,同样可以省略图21A-21C的结构的电容器2705。

注意本实施模式所示EL显示器件的电路结构可以选自实施模式1所示TFT结构,形成图21A-21C所示电路。可以使用本实施例的EL显示屏作为实施模式7的电子器件的显示段。

[实施例1

[实施例1]

如实施模式1所示,TFT的栅电极和栅极布线在岛状半导体层之外接触,不插入接触孔。对这种结构的栅电极和栅极布线的电阻的评价结果如表1和2所示。表1展示了形成栅电极和栅极布线的薄层电阻。

表1:用于栅极和栅极总线的金属的各种薄层电阻

表2展示了由接触链(接触数量100-200)的测量值而计算的每个接触段的接触电阻的结果,这是为了评价栅电极和栅极布线的接触电阻。每个接触段的面积设定为4μm×10μm或6μm×10μm。

表2;栅极金属和栅极总线之间的每个接触链的接触电阻

对于栅电极,制备两种膜,即TaN膜和Ta膜的层叠膜和W膜。用Al形成栅极布线。注意向Al添加1wt%的Nd。(以下表示为Al-Nd膜)。当栅电极和栅极布线的交叠面积假设为40μm2,则接触电阻对于TaN膜和Ta膜的层叠膜大约是200Ω,对于W膜大约是0.1Ω。

图22展示了采用透射电镜(TEM)对栅电极交叠段的观察结果,栅电极是通过层叠TaN膜和Ta膜,和W膜形成的。图23是Ta膜和Al-Nd膜之间界面的放大图,通过能量分布X-射线光谱(EDX)检测图中表示为*1和*4的点的成分。结果,虽然在*1检测到Al,在*4检测到Ta,但是发现形成了包括氧化物的层,这是因为在*2检测到Al和氧,在*3检测到Ta和氧。假设原因是Ta膜表面在用于杂质元素激活的热处理工艺中被氧化,这是在形成作为栅电极的Ta膜之后进行的。再形成Al-Nd膜时,Ta膜表面的氧估计氧化了Al-Nd膜。这样提高的接触电阻是采用Ta时显著出现的结果。

但是,通过模拟接触电阻对信号波形施加的影响进行测试,证实了对200Ω左右的接触电阻的影响并不很大。图26A和26B展示了因波形上沿和波形下沿的电阻引起的差异。用于计算的等效电路如图中插图所示。这里通过从1Ω到1MΩ改变对应于接触电阻的R2进行模拟,证实了大至约10kΩ的接触电阻也几乎不能发现其影响。

而且,作为接触段的可靠性测试进行导电性测试,考察接触电阻的差异。制备具有40μm2的接触段面积和接触数量200的测试样品,在180℃的气氛中导通1小时的1mA的电流。虽然对上述两种栅电极材料检测了接触电阻的差异,但是几乎观察不到差异。

[实施例2]

通过偏置热应力实验(以下称为BT实验)研究制备的TFT的可靠性。TFT的尺寸是沟道长度为8μm,沟道宽度是8μm。实验条件是+20V的栅电极电压和0V的栅电极电压施加于n-沟道TFT,并在150℃保持1小时。图24A和24B展示了分别针对n-沟道TFT和p-沟道TFT的结果,但是在两种情形下几乎观察不到因偏置应力的退化。

[实施例3]

评价因栅极布线材料的差异而产生的信号延迟的影响。图25A和25B展示了信号输入段和输出段之间的波形差异,其中25A展示了波形上沿,25B展示了波形下沿。输入段和输出段之间的距离是83mm。图25A和25B中,表示为J2的特性是针对由Ta膜和Ta膜的层叠形成的栅极布线,表示为J4的样品是用Al-Nd膜的栅极布线形成的样品。栅极布线的宽度是10μm。虽然前者样品对于上沿时间和下沿时间在输入段和输出段之间有大的差异,但是后者样品具有极小的差异。J2样品的延迟时间是J4样品的大约10倍,从表1所示薄层电阻清晰可见,可以认为布线材料的电阻影响延迟时间。

表3 单位:nsec

从上述结果可见,在显示尺寸是4英寸以上的情形,必须用正如本发明的低电阻材料形成与栅电极连接的栅极布线。

通过使用本发明,可以使TFT具有半导体器件的功能电路的技术要求所适用的性能,上述半导体器件(本例中具体是光电器件)在同一衬底上形成有多功能电路,这样可使工作特性和可靠性有很大的提高。特别是,通过使象素矩阵电路的n-沟道TFT的LDD区形成为具有n-浓度并仅作为Loff,可以急剧地减低截止电流值,这有利于减低象素矩阵电路的功耗。而且,通过使驱动电路的n-沟道TFT的LDD区形成为具有n-浓度并仅作为Lov,可以提高电流驱动容量,防止因热载流子而产生的退化,这样减低了导通电流值的减低退化。还可以改善具有这种光电器件作为其显示介质的半导体器件(本例中具体是电子设备)的工作性能和可靠性。

此外,通过用高度耐热、导电材料形成象素TFT和驱动电路TFT的栅电极,形成用低电阻材料例如铝(Al)连接栅电极的栅极布线,可以实现上述满意的TF丁性能,使用这种TFT来实现4英寸以上的大尺寸显示器件。

Claims (12)

1.一种半导体器件,包括:

半导体区;

在所述半导体区上形成的栅绝缘膜;

包括氮化钽层和在所述氮化钽层上的钨层的栅电极,其中,所述氮化钽层与所述栅绝缘膜直接接触;以及

在所述栅电极上形成的层间绝缘膜,

其中,所述钨层中的氧浓度在30ppm以下,其电阻率在20μΩcm以下。

2.一种半导体器件,包括:

半导体区;

在所述半导体区上形成的栅绝缘膜;

包括氮化钽层和在所述氮化钽层上的钨层的栅电极,其中,所述氮化钽层与所述栅绝缘膜直接接触;以及

在所述栅电极上形成的层间绝缘膜,

其中,所述氮化钽层厚度为10-50nm,以及

其中,所述钨层中的氧浓度在30ppm以下,其电阻率在20μΩcm以下。

3.如权利要求1和2中任一项所述的半导体器件,其中,所述钨层厚度为200-400nm。

4.一种半导体器件,包括:

半导体区;

在所述半导体区上形成的栅绝缘膜;

包括氮化钽层和在所述氮化钽层上的金属层的栅电极,其中,所述氮化钽层与所述栅绝缘膜直接接触;以及

在所述栅电极上形成的层间绝缘膜,

其中,所述金属层中的氧浓度在30ppm以下。

5.一种半导体器件,包括:

半导体区;

在所述半导体区上形成的栅绝缘膜;

包括氮化钽层和在所述氮化钽层上的金属层的栅电极,其中,所述氮化钽层与所述栅绝缘膜直接接触;以及

在所述栅电极上形成的层间绝缘膜,

其中,所述氮化钽层厚度为10-50nm,以及

其中,所述金属层中的氧浓度在30ppm以下。

6.如权利要求4和5中任一项所述的半导体器件,其中,所述金属层厚度为200-400nm。

7.如权利要求1、2、4和5中任一项所述的半导体器件,其中,所述半导体器件是薄膜晶体管。

8.如权利要求1、2、4和5中任一项所述的半导体器件,其中,所述栅绝缘膜含硅。

9.如权利要求4和5中任一项所述的半导体器件,其中,所述金属层与所述氮化钽层接触。

10.如权利要求1、2、4和5中任一项所述的半导体器件,其中,所述半导体区形成于绝缘表面上。

11.如权利要求1、2、4和5中任一项所述的半导体器件,还包括与所述栅电极接触的第三导电层,其中,所述第三导电层包括从由铝和铜组成的组中选择的一种材料。

12.如权利要求1、2、4和5中任一项所述的半导体器件,其中,所述半导体器件被装入从由个人计算机、摄像机、数字相机、电子书和便携式信息终端组成的组中选择的一种装置中。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP10464699 | 1999-04-12 | ||

| JP104646/1999 | 1999-04-12 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN2006100737812A Division CN1870293B (zh) | 1999-04-12 | 2000-04-12 | 半导体器件及其制造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1917232A CN1917232A (zh) | 2007-02-21 |

| CN100481506C true CN100481506C (zh) | 2009-04-22 |

Family

ID=14386237

Family Applications (4)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB2006101030029A Expired - Fee Related CN100481506C (zh) | 1999-04-12 | 2000-04-12 | 半导体器件及其制造方法 |

| CN2006100737812A Expired - Fee Related CN1870293B (zh) | 1999-04-12 | 2000-04-12 | 半导体器件及其制造方法 |

| CNB001188097A Expired - Fee Related CN1197157C (zh) | 1999-04-12 | 2000-04-12 | 半导体器件及其制造方法 |

| CN2005100081531A Expired - Fee Related CN1655038B (zh) | 1999-04-12 | 2000-04-12 | 半导体器件及其制造方法 |

Family Applications After (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN2006100737812A Expired - Fee Related CN1870293B (zh) | 1999-04-12 | 2000-04-12 | 半导体器件及其制造方法 |

| CNB001188097A Expired - Fee Related CN1197157C (zh) | 1999-04-12 | 2000-04-12 | 半导体器件及其制造方法 |

| CN2005100081531A Expired - Fee Related CN1655038B (zh) | 1999-04-12 | 2000-04-12 | 半导体器件及其制造方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (5) | US7456430B1 (zh) |

| EP (4) | EP1780589A3 (zh) |

| JP (8) | JP2010219549A (zh) |

| KR (1) | KR100733892B1 (zh) |

| CN (4) | CN100481506C (zh) |

| TW (1) | TW444257B (zh) |

Families Citing this family (43)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP2284605A3 (en) * | 1999-02-23 | 2017-10-18 | Semiconductor Energy Laboratory Co, Ltd. | Semiconductor device and fabrication method thereof |

| US6531713B1 (en) * | 1999-03-19 | 2003-03-11 | Semiconductor Energy Laboratory Co., Ltd. | Electro-optical device and manufacturing method thereof |

| TW444257B (en) | 1999-04-12 | 2001-07-01 | Semiconductor Energy Lab | Semiconductor device and method for fabricating the same |

| EP2256808A2 (en) | 1999-04-30 | 2010-12-01 | Semiconductor Energy Laboratory Co, Ltd. | Semiconductor device and manufacturing method therof |

| JP4666723B2 (ja) | 1999-07-06 | 2011-04-06 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| SG116443A1 (en) | 2001-03-27 | 2005-11-28 | Semiconductor Energy Lab | Wiring and method of manufacturing the same, and wiring board and method of manufacturing the same. |

| KR100507278B1 (ko) * | 2001-05-31 | 2005-08-09 | 비오이 하이디스 테크놀로지 주식회사 | 박막 트랜지스터 액정표시장치 제조방법 |

| WO2004027740A1 (en) | 2002-09-20 | 2004-04-01 | Semiconductor Energy Laboratory Co., Ltd. | Display device and manufacturing method thereof |

| KR100493030B1 (ko) * | 2002-11-08 | 2005-06-07 | 삼성전자주식회사 | 하드 디스크 드라이브의 액츄에이터 로킹 장치 |

| CN101882668B (zh) | 2002-12-19 | 2012-05-09 | 株式会社半导体能源研究所 | 显示装置 |

| WO2004068910A1 (ja) * | 2003-01-24 | 2004-08-12 | Semiconductor Energy Laboratory Co. Ltd. | 発光装置及びその製造方法、並びに前記発光装置を用いた電気機器 |

| US7161184B2 (en) | 2003-06-16 | 2007-01-09 | Semiconductor Energy Laboratory Co., Ltd. | Display device and method for manufacturing the same |

| US7221095B2 (en) | 2003-06-16 | 2007-05-22 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device and method for fabricating light emitting device |

| US7224118B2 (en) | 2003-06-17 | 2007-05-29 | Semiconductor Energy Laboratory Co., Ltd. | Display device and electronic apparatus having a wiring connected to a counter electrode via an opening portion in an insulating layer that surrounds a pixel electrode |

| SG142140A1 (en) | 2003-06-27 | 2008-05-28 | Semiconductor Energy Lab | Display device and method of manufacturing thereof |

| US20070052021A1 (en) * | 2005-08-23 | 2007-03-08 | Semiconductor Energy Laboratory Co., Ltd. | Transistor, and display device, electronic device, and semiconductor device using the same |

| KR20090115222A (ko) | 2005-11-15 | 2009-11-04 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체장치 제조방법 |

| US7851996B2 (en) * | 2005-11-16 | 2010-12-14 | Canon Kabushiki Kaisha | Display apparatus |

| US8395746B2 (en) | 2006-01-31 | 2013-03-12 | Semiconductor Energy Laboratory Co., Ltd. | Display device |

| JP4321557B2 (ja) * | 2006-07-06 | 2009-08-26 | エプソンイメージングデバイス株式会社 | 電気光学装置、電気光学装置の製造方法及び電子機器 |

| JP4991634B2 (ja) * | 2008-06-09 | 2012-08-01 | キヤノン株式会社 | 有機el発光装置 |

| KR101273972B1 (ko) | 2008-10-03 | 2013-06-12 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체장치 |

| JP5577646B2 (ja) * | 2009-01-09 | 2014-08-27 | セイコーエプソン株式会社 | 電気泳動表示装置、電子機器、電気泳動表示装置の製造方法 |

| US8461582B2 (en) | 2009-03-05 | 2013-06-11 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| US20100224878A1 (en) | 2009-03-05 | 2010-09-09 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| WO2011065208A1 (en) | 2009-11-27 | 2011-06-03 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| US8415677B2 (en) * | 2010-01-20 | 2013-04-09 | International Business Machines Corporation | Field-effect transistor device having a metal gate stack with an oxygen barrier layer |

| US8304840B2 (en) * | 2010-07-29 | 2012-11-06 | Taiwan Semiconductor Manufacturing Company, Ltd. | Spacer structures of a semiconductor device |

| WO2012042564A1 (ja) | 2010-09-29 | 2012-04-05 | パナソニック株式会社 | 表示装置用薄膜半導体装置、表示装置用薄膜半導体装置の製造方法、el表示パネル及びel表示装置 |

| JP5386643B2 (ja) | 2010-09-29 | 2014-01-15 | パナソニック株式会社 | 表示装置用薄膜半導体装置、表示装置用薄膜半導体装置の製造方法、el表示パネル及びel表示装置 |

| US9508904B2 (en) * | 2011-01-31 | 2016-11-29 | Cree, Inc. | Structures and substrates for mounting optical elements and methods and devices for providing the same background |

| JP5626010B2 (ja) * | 2011-02-25 | 2014-11-19 | 富士通株式会社 | 半導体装置及びその製造方法、電源装置 |

| TW201322341A (zh) * | 2011-11-21 | 2013-06-01 | Ind Tech Res Inst | 半導體元件以及其製造方法 |

| TWI491050B (zh) * | 2011-11-25 | 2015-07-01 | Sony Corp | 電晶體,顯示器及電子裝置 |

| TWI611567B (zh) * | 2013-02-27 | 2018-01-11 | 半導體能源研究所股份有限公司 | 半導體裝置、驅動電路及顯示裝置 |

| KR102086422B1 (ko) | 2013-03-28 | 2020-03-10 | 삼성디스플레이 주식회사 | 표시패널 및 이의 제조방법 |

| KR102402717B1 (ko) * | 2016-08-30 | 2022-05-27 | 소니 세미컨덕터 솔루션즈 가부시키가이샤 | 표시 장치 및 전자 기기 |

| CN107134474B (zh) * | 2017-06-12 | 2020-07-24 | 武汉华星光电半导体显示技术有限公司 | 薄膜晶体管及其制作方法、有机电致发光显示器 |

| US11049887B2 (en) | 2017-11-10 | 2021-06-29 | Applied Materials, Inc. | Layer stack for display applications |

| US10692799B2 (en) * | 2018-06-01 | 2020-06-23 | Innolux Corporation | Semiconductor electronic device |

| KR102600041B1 (ko) * | 2018-06-07 | 2023-11-08 | 삼성디스플레이 주식회사 | 유기 발광 표시 장치 |

| CN109686861B (zh) * | 2018-12-26 | 2020-12-11 | 上海晶合光电科技有限公司 | 一种环套式分立控制图案化有机电致发光器件及其制备方法 |

| JP2023144395A (ja) * | 2022-03-28 | 2023-10-11 | セイコーエプソン株式会社 | 電気光学装置および電子機器 |

Family Cites Families (136)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US699543A (en) * | 1896-06-03 | 1902-05-06 | Electric Vehicle Company | Motor-vehicle. |

| US679749A (en) * | 1901-03-12 | 1901-08-06 | Louis J Hirt | Coke-oven. |

| US710910A (en) * | 1902-01-09 | 1902-10-07 | John H Wescott | Compound engine. |

| JPS5847461A (ja) | 1981-09-16 | 1983-03-19 | Takeda Chem Ind Ltd | 高比容化学調味料顆粒およびその製造法 |

| JPH0613612Y2 (ja) | 1983-07-20 | 1994-04-13 | ヤンマー農機株式会社 | 作業機の角度制御装置 |

| JPS6096921A (ja) | 1983-10-31 | 1985-05-30 | Yamatake Honeywell Co Ltd | 電子スイツチの過電流検出回路 |

| JPH0613605Y2 (ja) | 1986-03-03 | 1994-04-13 | 大介 藤井 | 整畦機 |

| JPH0194664A (ja) * | 1987-10-05 | 1989-04-13 | Nec Corp | 電界効果トランジスタ |

| JPH0827465B2 (ja) * | 1988-04-06 | 1996-03-21 | 株式会社日立製作所 | 平面デイスプレイ |

| JPH01281434A (ja) * | 1988-05-09 | 1989-11-13 | Toshiba Corp | 表示装置の電極形成方法 |

| JP2720470B2 (ja) * | 1988-08-26 | 1998-03-04 | 富士通株式会社 | 薄膜トランジスタマトリクスの製造方法 |

| JPH06104433B2 (ja) | 1988-11-04 | 1994-12-21 | 株式会社小糸製作所 | 車輌用コーナリングランプシステム |

| JPH07113726B2 (ja) * | 1989-01-10 | 1995-12-06 | 富士通株式会社 | 薄膜トランジスタマトリクスの製造方法 |

| JPH065852Y2 (ja) | 1989-02-10 | 1994-02-16 | 駿河精機株式会社 | 発泡プラスチックの減容機 |

| GB8909011D0 (en) | 1989-04-20 | 1989-06-07 | Friend Richard H | Electroluminescent devices |

| US5245207A (en) | 1989-04-21 | 1993-09-14 | Nobuo Mikoshiba | Integrated circuit |

| US5153690A (en) * | 1989-10-18 | 1992-10-06 | Hitachi, Ltd. | Thin-film device |

| US5266825A (en) * | 1989-10-18 | 1993-11-30 | Hitachi, Ltd. | Thin-film device |

| US5264728A (en) * | 1989-11-30 | 1993-11-23 | Kabushiki Kaisha Toshiba | Line material, electronic device using the line material and liquid crystal display |

| JP3024620B2 (ja) | 1990-04-11 | 2000-03-21 | セイコーエプソン株式会社 | 液晶パネルの製造方法 |

| GB2243948B (en) | 1990-04-20 | 1994-06-08 | Nobuo Mikoshiba | Integrated circuit |

| JP2628928B2 (ja) | 1990-05-22 | 1997-07-09 | 株式会社フロンテック | 薄膜トランジスタアレイおよびその製造方法 |

| US5402254B1 (en) * | 1990-10-17 | 1998-09-22 | Hitachi Ltd | Liquid crystal display device with tfts in which pixel electrodes are formed in the same plane as the gate electrodes with anodized oxide films before the deposition of silicon |

| US5343063A (en) * | 1990-12-18 | 1994-08-30 | Sundisk Corporation | Dense vertical programmable read only memory cell structure and processes for making them |

| JPH04364723A (ja) * | 1991-06-12 | 1992-12-17 | Kawasaki Steel Corp | 半導体装置及びその製造方法 |

| JPH07111334B2 (ja) | 1991-07-15 | 1995-11-29 | 協同組合ブライト北九州 | 表面形状測定装置 |

| JPH0613612A (ja) * | 1991-12-03 | 1994-01-21 | Nec Corp | 薄膜トランジスタ |

| JPH05326960A (ja) * | 1992-05-20 | 1993-12-10 | Seiko Epson Corp | 薄膜トランジスタを備えた固体装置およびその製造方法 |

| JPH065852A (ja) * | 1992-06-23 | 1994-01-14 | Oki Electric Ind Co Ltd | Mosfet及びその製造方法 |

| US5508216A (en) | 1992-06-24 | 1996-04-16 | Seiko Epson Corporation | Thin film transistor, solid device, display device and manufacturing method of a thin film transistor |

| JP3189399B2 (ja) | 1992-06-26 | 2001-07-16 | ソニー株式会社 | 半導体装置の製造方法 |

| EP0582486A2 (en) | 1992-08-07 | 1994-02-09 | Sharp Kabushiki Kaisha | A thin film transistor pair and a process for fabricating the same |

| JP2859784B2 (ja) | 1992-09-03 | 1999-02-24 | シャープ株式会社 | アクティブマトリクス基板 |