CN101154461B - 半导体存储装置 - Google Patents

半导体存储装置 Download PDFInfo

- Publication number

- CN101154461B CN101154461B CN2007101802315A CN200710180231A CN101154461B CN 101154461 B CN101154461 B CN 101154461B CN 2007101802315 A CN2007101802315 A CN 2007101802315A CN 200710180231 A CN200710180231 A CN 200710180231A CN 101154461 B CN101154461 B CN 101154461B

- Authority

- CN

- China

- Prior art keywords

- data

- mentioned

- page

- signal

- storage unit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5621—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge storage in a floating gate

- G11C11/5628—Programming or writing circuits; Data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0483—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells having several storage transistors connected in series

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/08—Address circuits; Decoders; Word-line control circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/22—Safety or protection circuits preventing unauthorised or accidental access to memory cells

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/3436—Arrangements for verifying correct programming or erasure

- G11C16/3454—Arrangements for verifying correct programming or for detecting overprogrammed cells

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/70—Masking faults in memories by using spares or by reconfiguring

- G11C29/78—Masking faults in memories by using spares or by reconfiguring using programmable devices

- G11C29/83—Masking faults in memories by using spares or by reconfiguring using programmable devices with reduced power consumption

- G11C29/832—Masking faults in memories by using spares or by reconfiguring using programmable devices with reduced power consumption with disconnection of faulty elements

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/3436—Arrangements for verifying correct programming or erasure

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2211/00—Indexing scheme relating to digital stores characterized by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C2211/56—Indexing scheme relating to G11C11/56 and sub-groups for features not covered by these groups

- G11C2211/562—Multilevel memory programming aspects

- G11C2211/5621—Multilevel programming verification

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2211/00—Indexing scheme relating to digital stores characterized by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C2211/56—Indexing scheme relating to G11C11/56 and sub-groups for features not covered by these groups

- G11C2211/564—Miscellaneous aspects

- G11C2211/5641—Multilevel memory having cells with different number of storage levels

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/70—Masking faults in memories by using spares or by reconfiguring

Abstract

本发明用于准确识别存储器中的不良块的半导体存储装置,该半导体存储装置包含:具有多个存储元件的多个块;与上述各块对应设置的存储电路(109),上述存储电路存储第1逻辑电平或第2逻辑电平的数据;检出上述存储电路的存储状态的检出电路(6b);从上述各块的存储元件读出数据的读出电路,上述读出电路在通过上述检出电路检述存储电路存储上述第1逻辑电平时,输出上述块内存储元件的数据,在检出上述存储电路存储上述第2逻辑电平时,输出不取决于上述块内存储元件的数据的一定值。通过上述半导体存储装置能够准确识别存储器中的不良块,提高成品率。

Description

本申请是申请号为01137244.3,申请日为2001年9月20日,发明名称为“非易失半导体存储装置”的申请的分案申请。

本申请具有2000年9月28日提交的在先日本专利申请No.2000-297443的优先权,其全部内容已被引证在本申请中。

技术领域

本发明涉及半导体存储装置,例如可以电重写的非易失半导体存储装置。

背景技术

作为可以电重写的非易失半导体存储装置,提出了使用EEPROM的NAND型快速存储器。该NAND型快速存储器与相邻配置的多个存储单元的源极、漏极串联连接,该串联连接的多个存储单元作为1单位与位线连接。在该NAND型快速存储器中,对于按行方向配置的全部单元或半数单元,一起进行写入或读出。近来,又开发了在NAND型快速存储器的1个单元中存储多个数据的多值存储器。

然而,该种类的非易失半导体存储装置,具有称为存储了用于保密的识别代码等的ROM块(ROM BL0CK)的存储元件区域。该ROM块由特别指令进行选择。该ROM块被分配为救济存储单元阵列的不良单元的冗长单元的一部分。因此,当在该冗长单元的一部分中存在不良时,则会出现不能使用ROM块的问题。

而且,ROM块使用冗长单元的一部分。因而,难于根据需要将ROM块设定在禁止写入和禁止擦除。

NAND型快速存储器具有多个块(block),用该块单位擦除数据。具有不良单元的不良块,替换为冗余块。但是,在冗余数以上具有不良块时,将作为仍存留不良块的部分优良品(一部分良品)出厂。这时,为了识别不良块,在不良块的最前面数位写入数据“O”,当选取不良块时,即输出数据“O”。然而,在不良块的单元中不一定写入或不写入数据“O”。这时,尽管大部分存储单元是正常的,也必须废弃该产品。因此,导致了成品率降低。

发明内容

因此,在能够可靠存储用于保密的信息,但在部分存储器中有不良块的情况下,希望能有可以准确识别该不良块的半导体存储装置。

本发明的半导体存储装置包含:具有第1、第2存储区域的存储单元阵列,上述第1存储区域具有由地址信号选择的多个存储元件,上述第2存储区域具有由控制信号选择的多个存储元件;具有第1熔丝元件的控制电路,当上述控制电路切断了上述第1熔丝元件时,则禁止相对于上述第2存储区域的写入和擦除的至少其中之一。

附图说明

图1是表示本发明第1实施例的半导体存储装置的构成图。

图2是表示图1所示存储单元阵列1和数据存储部2的电路图。

图3A、B是表示存储单元和选择晶体管的断面图。

图4是表示存储单元阵列中的1个NADN单元的断面图。

图5是表示图2所示数据存储电路的电路构成。

图6A、6B、6C、6D是各方式的写入地址和I/O端子的关系图。

图7A、7B是图1所示前置译码器和列式RD译码器的动作图。

图8A、B、C是表示图1所示CG驱动电路的电路图,图8D是表示图8C的动作图。

图9A表示图1所示阵列块电路的动作,图9B表示锁存电路。

图10是图1所示块RD译码电路的动作图。

图11是图1所示块译码器的动作图。

图12是表示块选择电路的电路图。

图13是表示图12的动作的波形图。

图14是存储单元阵列的物理映象图。

图15A是表示图1所示禁止写入电路15a的电路图,图15B是表示禁止擦除电路15b的电路图。

图16是4值数据的写入方法图。

图17A是存储单元数据与写入和读出数据的关系图,图17B、17C是说明写入次数图。

图18是升压写入方法的写入特性图。

图19是表示程序动作顺序的波形图。

图20是表示倍速程序动作顺序的波形图。

图21是表示第1页的程序动作的流程图。

图22是表示第1页的程序动作的流程图。

图23是表示在第1页程序时的顺序的波形图。

图24是第1页的程序校验读出动作图。

图25是表示程序校验读出的顺序的波形图。

图26A、26B、26C是第2页的程序校验读出的动作图。

图27是表示在内部数据装入时的顺序的波形图。

图28是不第2页第1校验读出时的顺序的波形图。

图29是表示读出动作顺序的波形图。

图30是表示倍速读出动作顺序的波形图。

图31是概略表示读出动作的流程图。

图32是第2页的读出动作图。

图33A、图33B是第1页的读出动作图。

图34是表示第2页的读出动作顺序的波形图。

图35是表示第1页的读出动作顺序的波形图。

图36是表示擦除动作顺序的波形图。

图37是表示倍速擦除动作顺序的波形图。

图38是概略表示自动擦除的流程图。

图39是表示擦除动作顺序的波形图。

图40是表示擦除校验动作顺序的波形图。

图41是表示设置在图1所示控制电压发生电路内的电压设定电路的构成图。

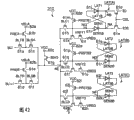

图42表示本发明的第2实施例,表示数据存储电路一例的电路图。

图43是表示第1页、第2页同时程序动作顺序的波形图。

图44是第1页、第2页同时程序动作图。

图45A、45B、45C、45D是第1页、第2页同时程序动作图。

图46是表示第1页、第2页同时程序动作的流程图。

图47是表示以第1页、第2页同时程序并倍速程序动作顺序的波形图。

具体实施方式

以下,参照附图说明本发明的实施例。

(第1实施例)

图1是本发明第1实施例的半导体存储装置的构成图。首先,用图1进行概略说明。

存储单元阵列1包含未图示的多个位(bit)线和多个字线以及共同借用线的可以进行电的数据重写的存储单元被配置为矩阵状。各存储单元阵列1的内部,如后所述,分割为多个块和多个冗长块。在各存储单元阵列1的列方向一端,分别配置数据存储部2。在各存储单元阵列1的行方向两侧,分别配置块选择部6。

上述数据存储部2,如后所述,包含多个数据存储电路。各数据存储电路具有以下功能。(1)通过位线从存储单元阵列1中的存储单元读出数据。(2)通过位线检出存储单元阵列1中的存储单元的状态。(3)通过位线在存储单元阵列1中的存储单元外加写入控制电压,并在存储单元进行写入。

在各数据存储部2被连接到列译码器3、输入缓冲器7、输出缓冲器4。输入缓冲器7和输出缓冲器4与I/O端子5连接。

上述各列译码器3选择数据存储部2中的数据存储电路。从由列译码器3选择的数据存储电路读出的存储单元的数据,通过输出缓冲器4从I/O端子5向外部输出。从外部输入到I/O端子5的写入数据,通过输入缓冲器7,供给由列译码器3选择的数据存储电路。

控制部15根据从外部供给的信号ALE、CLE、CE、WE、RE、WP,控制上述输出缓冲器4、输入缓冲器7、ECC代码发生电路8、控制电路13、指令寄存器16、列地址寄存器17、行地址寄存器18。控制部15具有禁止后述的ROM块20写入的禁止写入电路15a、以及禁止ROM块20擦除的禁止擦除电路15b。控制部15,如后所述,还有转换半导体存储装置的设定方式的熔丝。

ECC代码发生电路8根据控制部15的指示发生ECC(错误订正代码),供给输入缓冲器7。

上述指令寄存器16将从上述输入缓冲器7供给的指令,供给控制电路13。该控制电路13根据指令控制各部。该控制电路13被连接到控制电压发生电路14。该控制电压发生电路14由例如充电激励电路等构成,产生数据写入、读出、擦除时的必要电压。

上述列地址寄存器17将从上述输入缓冲器7供给的地址,供给列RD(冗余)译码器和列前置译码器10。该列RD译码器和列前置译码器10对列的冗长地址进行译码,并对列地址进行前置译码。该列RD译码器和列前置译码器10的输出信号,被供给上述各列译码器3。

上述行地址寄存器18将从上述输入缓冲器7供给的地址,供给上述CG(控制栅极)驱动电路9和上述阵列块锁存电路19。

CG驱动电路9根据由行地址寄存器18供给的行地址,选择由上述控制电压发生电路14产生的字线电位,供给块选择部6。

上述块选择部6连接块译码器12。该块译码器12连接块RD(冗余)译码器11和ROM块指定电路20。上述块RD译码器11连接阵列块锁存电路19。该阵列块锁存电路19连接行地址寄存器18。

上述块选择部6根据阵列块锁存电路19、块RD译码器11和块译码器12的输出信号,选择存储单元阵列1内的块。块选择部6在数据读出、写入和擦除时,根据行地址,选择后述的传送栅极,将从CG驱动电路9供给的电压供给存储单元阵列1的字线。

上述ROM块指定电路20将存储单元阵列的冗长块指定为ROM块。也就是,本实施例中,可以将存储单元阵列内的任意冗长块指定为ROM块。在RO块中写入用于制造工序中保密的识别代码等。因此,ROM块在汇总写入、汇总擦除等的测试时,不进行选择。

图2表示图1所示存储单元阵列1和数据存储部2的构成。数据存储部2具有多个数据存储电路310、311~31n/2。各数据存储电路310、311~31n/2连接上述输入缓冲器4、输出缓冲器7。这些310、311~31n/2由从上述列译码器3供给的列选择信号CSL0、CSL1~CSLn/2控制。

各数据存储电路310、311~31n/2与一对位线连接。也就是,数据存储电路310与位线BL0、BL1连接,数据存储电路311与位线BL2、BL3连接,数据存储电路31n/2与位线BLn、BLn+1连接。

在存储单元阵列1配置多个NAND单元。1个NAND单元由串联连接的16个EEPROM组成的存储单元M0~M15、连接在该存储单元M15的第1选择栅极S1、连接在存储单元M0的第2选择栅极S2组成。第1选择栅极S1与位线BL0连接,第2选择栅极S2与源极线CELSRC连接。配置在各行的存储单元M0~M15的控制栅极共同连接字线WLO~WL15。并且,第1选择栅极S1共同连接选择线SGD1,第2选择栅极S2共同连接选择线SGD2。

当读出动作、程序校验动作和程序动作时在与数据存储电路连接的2条位线(BLi、BLi+1)中,通过由外部指定的地址选择1条位线。再根据外部地址,选择1条字线,选择2值时1页、4值时用图2虚线表示的2页的单元。

擦除动作由图2的虚线表示的块单位实行。也就是,以该块单位擦除数据。1块由多个NAND单元构成。在与数据存储电路连接的2条位线(BLi、BLi+1)同时进行。

擦除校验动作,通过1次动作,在与数据存储电路连接的2条位线(BLi、BLi+1)中,对1条位线(BLi)进行校验动作。然后,对另一条位线(BLi+1)进行校验动作。

图3A、3B表示存储单元和选择晶体管的断面图。图3A表示存储单元。在基片41上形成作为存储单元的源极、漏极的n型扩散层42。在基片41上通过栅极绝缘膜43形成浮置栅极44。在该浮置栅极44上通过绝缘膜45形成控制栅极46。

图3B表示选择晶体管。在基片41上形成作为源极、漏极的n型扩散层47。在基片41上通过栅极绝缘膜48形成控制栅极49。

图4表示存储单元阵列的1个NAND单元的断面。该例中,1个NANA单元由16个存储单元M0~M15串联连接构成。各存储单元形成图3A所示的构成。在NAND单元的漏极侧和源极侧,设置第1选择栅极S1和第2选择栅极S2。第1选择栅极S1和第2选择栅极S2形成图3B所示的结构。

图5表示图2所示数据存储电路310的电路构成。数据存储电路全部是同样构成,所以仅对数据存储电路310予以说明。

位线BLi与N沟道晶体管61a的电流通路的一端连接。将信号BLTR供给该晶体管61a的栅极。该晶体管61a的电流通路的另一端与晶体管61b的电流通路的一端和晶体管61c的电流通路的一端连接。上述晶体管61b的电流通路的另一端与端子62a连接。将电压VBLA供给该端子62a。将信号PREA供给上述晶体管61b的栅极。将信号BLSA供给上述晶体管61c的栅极。

位线BLi+1与N沟道晶体管61d的电流通路的一端连接。将上述信号BLTR提供给该晶体管61d的栅极。该晶体管61d的电流通路的另一端与晶体管61e的电流通路的一端和晶体管61f的电流通路的一端连接。上述晶体管61e的电流通路的另一端与端子62b连接。将电压VBLB供给该端子62b。将信号PREB供给上述晶体管61e的栅极。将信号BLSB供给上述晶体管61f的栅极。晶体管61b、61e根据信号PREA、PREB将非选择的位线预充电至电位VBLA、VBLB。上述晶体管61c、61f根据信号BLSA、BLSB选择位线。

上述晶体管61c、61f的电流通路的另一端通过晶体管61g与端子62c连接,并同时与结点NE连接。将信号BIAS供给上述晶体管61g的栅极,将电压VCC供给端子62e。该晶体管61g在数据读出时,根据信号BIAS对位线予充电。

上述结点NE与晶体管61h的电流通路的一端连接。将信号BLC1供给该晶体管61h的栅极。该晶体管61h的电流通路的另一端通过P沟道M0S晶体管61m与端子62d连接。将电压VCC供给该端子62d。将信号PRSTB1供给上述晶体管61m的栅极。

上述晶体管61h的电流通路的另一端与第1锁存电路LAT(A)连接。该第1锁存电路LAT(A)由2个同步脉冲倒相电路61l、61j构成。同步脉冲倒相电路61l由信号SEN1、SEN1B(B表示倒相信号)控制。同步脉冲倒相电路61j由信号LAT1、LAT1B控制。该第1锁存电路LAT(A)锁存写入数据。

在上述同步脉冲倒相电路61j的输出结点NB以及同步脉冲倒相电路61l的输入端的连接结点NC,连接N沟道M0S晶体管610的电流通路的一端。该晶体管610的电流通路的另一端IO连接上述输入缓冲器7、输出缓冲器4。

在上述同步脉冲倒相电路61l的输出结点NA以及同步脉冲倒相电路61j的输入端的连接结点,连接N沟道M0S晶体管61n的电流通路的一端。该晶体管61n的电流通路的另一端IOB与上述输入缓冲器7、输出缓冲器4连接。将来自列译码器3的列选择信号CSL供给这些晶体管610、61n的栅极。

在上述结点NE,晶体管61K、61l串联连接。晶体管61K的栅极与上述第1锁存电路LAT(A)的结点NC连接,将信号VRFY1供给晶体管61l的栅极。将信号VREG供给晶体管61l的电流通路。这些晶体管61K、61l根据在第1锁存电路LAT(A)锁存的数据,设定位线的电位。

另外,在上述结点NE,连接晶体管61q的电流通路的一端。将信号BLC2供给该晶体管61q的栅极。在该晶体管61q的电流通路的另一端,通过P沟道M0S晶体管61p与端子62e连接。将电压VCC供给该端子62e。将信号PRSTB2供给上述晶体管61p的栅极。

在上述晶体管61q的电流通路的另一端,连接第2锁存电路LAT(B)。该第2锁存电路LAT(B)由2个同步脉冲倒相电路61r、61s构成。同步脉冲倒相电路61r由信号SEN2、SEN2B控制。同步脉冲倒相电路61s由信号LAT2、LAT2B控制。该第2锁存电路LAT(B),锁存从存储单元读出的数据。

在上述结点NE,晶体管61t、61u串联连接。晶体管61t的栅极与上述第2锁存电路LAT(B)的结点ND连接,将信号VRFY2供给晶体管61u的栅极。将信号VREG供给晶体管61u的电流通路。这些晶体管61t、61u根据在第2锁存电路LAT(B)锁存的数据,设定位线的电位。

对上述构成的动作予以说明。

(指令输入)

指令使供给图1所示控制部15的信号CLE为高电平,在信号VE的前沿和后沿时,供给I/O端子5的数据作为指令供给指令寄存器16。

(地址输入)

地址使图1所示控制部15的信号ALE为高电平,在信号WE的前沿和后沿时,供给I/O端子5的数据作为地址取入。

图6A、6B、6C、6D表示在各状态写入的地址与I/O端子的关系。该实施例的半导体存储装置可将存储单元阵列转换设定为4种状态。该4种状态的转换可以通过切断设置在控制部15的未图示的熔丝来设定。

图6A是以1G(千兆)位在1个单元存储2位的4值数据存储,块规模表示32KB的状态。图6B是以512M(兆)位在1个单元存储1位的2值数据存储,块规模表示16KB的状态。图6C是以1G位存储4值数据,块规模表示128KB的状态。图6D是以512M位存储2值数据,块规模表示64KB的状态。

在各动作状态,读出、程序通过4循环取出列地址和块地址等。然而,由于擦除不必要取出列地址,则第1循环省略,在从第2循环开始的4循环的3循环输入的地址。

在图6A、6C所示4值情况下,必须转换1页和2页。该转换利用第2循环的MLAdd进行。2值情况下,在1个单元仅存储1位。因此,不必要转换页。

图6A所示列地址A8、A8E,根据指令转换输入。

(数据输入)

当输入写入数据时,使图1所示控制部15的信号ALE和信号CLE都为低电平,在信号WE的前沿和后沿时,取入供给I/O端子5的数据。该数据供给由列译码器3选择的数据存储电路。通过连续触发信号WE,列地址增加,顺序取入下一个地址数据。

(数据输出)

当将从存储单元读出的数据输出到外部时,使图1所示控制部15的信号ALE和信号CLE都为低电平。在这种状态下,在信号RE的前沿和后沿时,由列译码器3选择的数据存储电路的数据从I/O端子5输出。通过反复触发信号RE,地址增加,顺序输出下一个地址数据。

(前置译码器和列RD译码器)

图7A、7B表示前置译码器和列RD译码器10的动作。

图1所示列地址寄存器17锁存由外部指定的地址A0~A8、A8E,同时与信号WE和信号RE同步,增加地址。使用ECC时,为了存储ECC代码,对于列地址的528列,必须追加21列。也就是,当订正2位时,每1页(528位)必须有订正代码用的21位单元。但是,21列中的4列是与列冗余共同的。因此,仅增加了17列的列地址。

列前置译码器和列RD译码器10,如图7A所示,对列地址A0~A8、A8E进行译码,输出列前置译码信号CA0~7、CB0~7、CC0~8。这样,选择528+17列。

如图7B所示,选择列冗余时,停止列前置译码信号,输出选择列冗余的信号CSS0~7。本实施例中,ECC未使用时,列冗余对于1个阵列为8个。使用ECC时,列冗余对于1个阵列为4个,17列由信号CA0~7、CB0~8选择,4列由信号CSS0~3选择。

从列前置译码器和列RD译码器10输出的信号CA0~7、CB0~7、CC0~8,由列译码器3选择528列中的1个。信号CSS0~7直接选择未被译码的1个列。

图1所示行地址寄存器18锁存由外部指定的地址A9~A26。

图8A、8B、8C表示图1所示CG驱动电路9。

在读出和程序时,首先,由图8A、8B所示电路分别生成选择CG电压Vcgsel和非选择CG电压Vcgusel。选择CG电压Vcgsel,读出时设定在电压Vcgrv,程序时设定在电压Vpgmh。非选择CG电压Vcgusel,读出时设定在电压Vread,程序时设定在电压Vpass。

图8A是产生被选择的控制栅极线电位的电路,由升压电路81a、81b、晶体管81c、81d构成。在晶体管81c的电流通路的一端,供给来自控制电压发生电路14的程序电压Vpgmh。该晶体管81c的栅极连接升压电路81a的输出端。将程序电压Vpgmh以及信号VPGMEN供给升压电路81a,升压电路81a根据信号VPGMEN产生电压Vpgmh+Vth。因此,晶体管81c可以输出电压Vpgmh。

在晶体管81d的电流通路的一端,供给来自控制电压发生电路14的电压Vcgrv。该晶体管81d的栅极连接升压电路81b的输出端。将电压Vcgrv以及信号VCGREN供给升压电路81b,升压电路81b根据信号VCGREN产生电压Vcgrv+Vth。因此,晶体管81d可以输出电压Vcgrv。这些晶体管81c、81d的电流通路的另一端共同连接,从该连接结点输出由电压Vpgmh或电压Vcgrv构成的选择CG电压Vcgsel。

图8B是产生非选择的控制栅极线电位的电路,由升压电路82a、82b、晶体管82c、82d构成。在晶体管82c的电流通路的一端,供给来自控制电压发生电路14的电压Vpass。该晶体管82c的栅极连接升压电路82a的输出端。将电压Vpass以及信号VPASSENB供给该升压电路82a,升压电路82a根据信号VPASSENB产生电压Vpass+Vth。因此,晶体管82c可以输出电压Vpass。

在晶体管82d的电流通路的一端,供给来自控制电压发生电路14的电压Vreadh。该晶体管82d的栅极连接升压电路82b的输出端。将电压Vreadh以及信号VREADEN供给该升压电路82b,升压电路82b根据信号VREADEN产生电压Vreadh+Vth。因此,晶体管82d可以输出电压Vreadh。这些晶体管82d的电流通路的另一端共同连接,从该连接结点输出由电压Vpass或Veadh构成的非选择CG电压Vcgusel。

图8C表示将选择CG电压Vcgsel和非选择CG电压Vcgusel供给控制栅极的CG供给电路。该CG供给电路与控制栅极对应设置16个。根据地址A11~A14,使其中的1个为选择状态,剩余的15个为非选择状态。

也就是,CG供给电路由译码电路83a、倒相电路83b、升压电路83c、83d、晶体管83e、83f、83g构成。将地址A11-A14供给译码电路83a的输入端。根据该地址选择CG供给电路时,通过升压电路83c使晶体管83e导通,作为控制栅极电压VCGi,输出上述选择CG电压Vcgsel。当CG供给电路为非选择时,通过升压电路83d使晶体管83f导通,作为控制栅极电压VCGi,输出上述非选择CG电压Vcgusel。

擦除情况下,信号ERASEEN为高电平,晶体管83g导通。因此,全部控制栅极电压VCG0~VCG15为接地电位。

图8D表示地址A11~A14与控制栅极电压VCGi的关系。该图8D表示根据地址A11~A14输出1个控制栅极电压VCGi。

这样,以图8A、8B所示电路和图8C所示电路的2阶段转换控制栅极电压VCGi。因此,可以从各CG供给电路输出在读出、程序、以及擦除时必要的全部电位。并且,采用上述2阶段的电路构成,可以缩小电路规模。

图9A、9B表示图1所示阵列块电路19。阵列块电路19在每个存储单元阵列锁存块地址(A17~26)。

如图9A所示,4个存储单元阵列由地址A15、A16选择。被选择的存储单元阵列的锁存信号PBLATPB0~3为高电平。

图9B表示设置在阵列块锁存电路19的锁存电路。该锁存电路与A17~A26的各块地址对应配置。该锁存电路由倒相电路91a、“与非”电路91b、构成触发电路的“与非”电路91c、91d构成。该锁存电路在锁存信号PBLATP0~3为高电平时,锁存块地址A17-A26。

图10表示图1所示块RD译码器11的动作。该块RD译码器11,当从阵列块锁存电路19供给的块地址A17~A26与由熔丝设定的块冗余地址APB17~APB26一致时,输出地址ATPB17~ATPB26和选择冗余区域的信号ATPBD。该地址ATPB17~ATPB26和信号ATPBD用于从多个存在的块冗余中选择1个。

图10表示块地址A17~26与块冗余地址APB17~APB26一致的情况。这时,块RD译码器11设块地址ATPB18和选择冗余区域的信号ATPBRD为高电平,从而选择位于ATPB18的块冗余。

图11表示图1所示块译码器12的动作。块译码器12对从块RD译码器11供给的块地址ATPB17~26以及ATPBRD进行译码,输出图11所示的行译码信号AROWA~AROWE和RDECPBLR。行译码信号AROWA~AROWE是用于选择存储单元阵列1内的块的信号。RDECPBLR是选择配置在存储单元阵列1两侧(左右)的块选择部6的其中之一的信号。

当选择ROM块指定电路20时,块译码器12与上述同样对从ROM块指定电路20供给的块地址进行译码,生成用于选择ROM块的行译码信号AROWA~AROWE。

图12表示设置在图1所示块选择部6的块选择电路6a的电路构成。该块选择电路6a相对于各块设置1个。图12所示熔丝状态检出电路6b,对于各存储单元阵列1各配置1个。

在块选择电路6a,将电源电压VDD供给端子100。在该端子100和供给信号ROWCOM的结点相互之间,串联连接P沟道M0S晶体管101、N沟道M0S晶体管102、108。将上述信号RDECPBLR供给上述晶体管101的栅极。该信号RDECPBLR是选择存储单元阵列1的左侧或右侧的块选择部6的信号。将上述行译码信号AROWA~AROWE供给晶体管102~106的栅极。将信号RDECPBLRD供给晶体管107的栅极。信号RDECPBL如图13所示,稍迟于信号RDECPBLRD地变化。

用于存取ROM块的指令信号CD_ROMBA被供给晶体管108的栅极。在该晶体管108,熔丝109并联连接。当与该块选择电路6a对应的块是不良块时,切断该熔丝109。

在上述晶体管101,P沟道M0S晶体管117、118串联电路并联连接。上述晶体管117的栅极接地(图中向下的箭头表示接地)。在上述晶体管101、102、118的连接结点连接倒相电路119的输入端。该倒相电路119的输出端与上述晶体管118的栅极连接,并与电平移相器120的一个输入端连接。

将信号VRDEC供给该电平移相器120的另一个输入端。该信号VRDEC是根据数据的程度、读出、擦除控制电平移相器120的信号。该电平移相器120,在块选择电路6a是选择状态时,根据信号VRDEC生成驱动传送栅极TG的信号。

上述传送栅极TG包含与存储单元的字线连接的传送栅极TG0~TG15,以及与第1、第2选择栅极S1、S2的栅极连接的传送栅极TGS1、TGS2。在传送栅极TG0~TG15的电流通路的一端分别连接控制栅极线CG0~CG15,在电流通路的另一端分别连接字线WL~WL15。将来自上述CG驱动电路9的控制栅极电压VCG分别供给控制栅极线CG0~CG15。

在传送栅极TGS1、TGS2的电流通路的一端分别连接选择栅极线SGD、SGS,在电流通路的另一端分别连接选择线SGD1、SGD2。将来自上述控制电压发生电路14的所定电压分别供给选择线SGD1、SGD2。

在上述选择线SGD1,N沟道M0S晶体管121、122串联连接。将信号SGDSPBLR供给晶体管121的电流通路的一端,将信号RDECADin+ln供给栅极。通过倒相电路123将上述倒相电路119的输出信号RDECADn供给晶体管122的栅极。

在上述选择线SGD2连接N沟道M0S晶体管124的电流通路的一端。将上述信号SGDSPBLR供给该晶体管124的电流通路的另一端,将上述信号RDECADn供给栅极。

在熔丝状态检出电路6b,供给上述信号ROWCOM的结点通过N沟道M0S晶体管110接地,并与N沟道M0S晶体管111的栅极连接。将信号ROWCOMVSS供给上述晶体管110的栅极。上述晶体管的电流通路的一端与倒相电路112的输入端、以及倒相电路113的输出端连接,另一端接地。上述倒相电路112的输出端和倒相电路113的输入端与倒相电路114的输入端连接。从该倒相电路114的输出端输出表示上述熔丝是否切断的信号FUSECUT。该信号FUSECUT被供给控制部15。该倒相电路114的输入端通过N沟道M0S晶体管115接地。信号BUSY通过倒相电路116被供给晶体管115的栅极。

对在上述构成中的块选择电路6a的动作予以说明。

信号RDECPBLR、信号RDECPBLRD、CDM_ROMBA、ROWCOM通常是接地电位VSS。因此,倒相电路119的输出信号RDECAD为低电平。

另一方面,当读出动作、程序动作、擦除动作开始时,与选择的存储单元阵列的右侧或左侧对应的信号RDECPBLR为高电平。在该状态下,当地址一致时,行译码信号AROWA~AROWE全部为高电平。因此,倒相电路119的输出信号RDECAD为高电平,电平移相器120被激活。该电平移相器120,在程序时输出程序电压Vpgm+Vth(Vth是传送栅极的阈值电压),在读出时输出读出电压Vread+Vth,在擦除时输出电源电压VDD。通过生成这些电压,传送栅极仍可传送来自CG驱动电路9的电压。

当地址不一致时,行译码信号AROWA~AROWE都为低电平,块选择电路6a为非选择状态。因此,电平移相器120的输出电压为接地电压VSS。在读出时、程序时,字线WL0~15为浮置(floating)的。选择线SGD1、SGD2,通过SGDSPBLR为接地电位,进而晶体管121、122、123导通而变为接地电位VSS。

擦除时,字线WL0~15为浮置状态,电压SGDSPBLR被设定为电源电压VDD。因此,选择线SGD1、SGD2的电位为VDD_Vth。然而,由于基片被设定在擦除电压VERA,则通过耦合,字线WL0~15以及选择线SGD1、SGD2都为接近擦除电压VERA的电位。

图12所示熔丝109,如前所述,在不良块情况下被切断。当都选择写入等的检测时,行译码信号AROWA~E全部为高电平。然而,由于熔丝109被切断,倒相电路119的输出信号RDECAD为低电平,不选择不良块。

当存取部分优良品的不良块时,在熔丝109被切断情况下,该不良块为非选择。因此,在这种状态下,进行读出动作时单元被关断。因而,2值时,读出数据自动为“0”数据。4值的第2页时,相对于“0”数据,第1页时为数据“1”。因此,在使信号RDECPBLR为高电平前,若信号ROWCOMVSS为低电平,则使ROWCOM浮置。

图13表示用于检出图12所示熔丝109状态的动作顺序。

首先,当使信号BUSY和信号RDECPBLRD为高电平状态时,使信号ROWCOMVSS为低电平。在这种状态下,行译码信号AROWA~AROWE都是高电平,而且在熔丝109未切断的块情况下,供给信号ROWCOM的结点电压为电源电压VDD。因此,晶体管111导通,由倒相电路112、113组成的锁存电路的输出端保持高电平。倒相电路114的输出信号FUSECUT为低电平。

在熔丝109切断的块情况下,供给信号ROWCOM的结点仍为浮置(电位是VSS)。因此,晶体管111关断,由倒相电路112、113组成的锁存电路的输出端保持低电平。倒相电路114的输出信号FUSECUT为高电平。

此后,信号ROWCOMVSS、信号RDECPBLRD为高电平。由倒相电路112、113组成的锁存电路保持锁存状态。因此,切断熔丝109时,哪个块也不选择。

这样,在图12所示电路的情况下,要知道是否切断熔丝109。因此,当切断熔丝109时,在第1次读出后,不进行第2次读出动作,输出为数据“0”。

当在多个单元写入相同数据的擦除动作时,对于擦除充分时擦除校验,数据存储电路的值为数据“1”,不充分时为数据“0”。然而,当熔丝109被切断时,哪个块也不选择的数据为“0”。因此,反复进行擦除校验,直到最大的循环次数。本发明为了防止这种情况,信号FUSECUT为高电平时,不进行该阵列的擦除。

图14表示存储单元阵列的物理映象,表示根据地址选择的物理位置。

各存储单元阵列1具有块blk0~blk23,以及作为冗长块的块冗作blkRD0~9。可以将块冗余blkRD0~blkRD9中的任意块冗余作为ROM块。例如,将块冗余blkRD1作为ROM块时,输入用于存取ROM块的指令信号CD_ROMBA,不从图1所示块RD译码器11输出信号。这时,从ROM块指定电路20,输出选择块冗余的信号A17~A26以及信号ARD,输出选择第1个块冗余的行译码信号ARDWA~AROWE。

ROM块的熔丝109通常是切断的。由于在多类别检验时将数据写入ROM块,因此在此后的汇总程序和汇总擦除时,不选择ROM块。

当存取ROM块时,图12中,使指令信号CMD_ROMBA为高电平,由于晶体管108导通,即使熔丝109被切断,也为选择状态。

图15A表示设置在图1所示控制部15的ROM块的禁止写入电路15a,图15B表示R0M块20的禁止擦除电路15b。

图15A中,禁止写入电路15a由P沟道M0S晶体管151a、151b,N沟道M0S晶体管151c,熔丝151d,倒相电路151e、151f、151h,“非或”电路151g组成。在上述晶体管151a、151b的电流通路的一端供给电源电压VDD,电流通路的另一端共同连接。在这些晶体管的连接结点和接地之间,连接上述晶体管151c和上述熔丝151d。将信号LOWVDDn供给晶体管151a和晶体管151c的栅极。上述连接结点通过上述倒相电路151e与“非或”电路151g的一个输入端连接。将指令信号CMD_ROMBA通过倒相电路151f供给该“非或”电路151g的另一个输入端。该“非或”电路151g的输出端与倒相电路151h的输入端连接,从该倒相电路151h的输入端输出信号PROENABL。

图15B所示禁止擦除电路15b是与禁止写入电路15a同样的构成。也就是,在晶体管152a、152b的电流通路的一端供给电源电压VDD,电流通路的另一端共同连接。在这些晶体管的连接结点和接地之间连接晶体管152c和熔丝152d。将信号LOWVDDn供给晶体管152a和晶体管152c的栅极。上述连接结点通过倒相电路152e与“非或”电路152g的一个输入端连接。指令信号CMD_ROMBA通过倒相电路152f供给该“非或”电路152g的另一个输入端。该“非或”电路152g的输出端与倒相电路152h的输入端连接,从该倒相电路152h的输出端输出信号ERAENABL。

上述信号LOWVDDn在接通电源时为低电平,此后则为高电平。在熔丝151d、152d切断前,输出信号PROENABL、输出信号ERAENABL经常为高电平。因此,程序和擦除是可能的。然而,在熔丝151d、152d切断后,存取ROM块的指令信号CMD_ROMBA为高电平,则输出信号PROENABL、ERAENABL都为低电平。因此,ROM块不能写入、擦除。可以任意设定熔丝151d或152d的切断。

(4值情况的动作)

说明本发明的半导体存储装置的4值情况的动作。

如图16、图17A所示,定义存储单元的数据和存储单元的阈值。这里,存储单元的数据为状态“0”~“3”,定义存储单元的阈值为从低到高。进行擦除时存储单元的数据为状态“0”。根据写入动作,存储单元的阈值电压向高方向移动。

图16表示本发明的写入方法。在存储单元写入数据时,首先,将第1页的数据写入存储单元,接着,将第2页的数据写入存储单元。这里,当构成第1页或第2页的数据的写入数据是“1”时,通过写入动作,存储单元的阈值电压不变化的存储单元的数据不变化。也就是,不将数据写入存储单元。当构成第1页或第2页的数据的写入数据是“0”时,通过写入动作使存储单元的阈值电压变化,则随之存储单元的数据也变化。也就是,数据被写入存储单元。

擦除状态的存储单元的数据为状态“0”。该状态下,最初第1页的数据被写入存储单元。当写入数据为“1”时,不进行写入的存储单元的数据仍是状态“0”。当写入数据为“0”时,进行写入的存储单元的数据为状态“1”。

然后,将第2页的数据写入存储单元。这时,通过第1页的写入动作,对于数据是状态“1”的存储单元,当供给写入数据“0”时,存储单元的数据为状态“2 ”。并且,通过第1页的写入动作,对于数据是状态“0”的存储单元,当供给写入数据“0”时,存储单元的数据为状态“3”。

通过第1页的写入动作,对于数据是状态“1”的存储单元,当从外部供给写入数据“1”时,存储单元的数据仍为状态“1”。并且,通过第1页的写入动作,对于数据是状态“0”的存储单元,当从外部供给写入数据“1”时,存储单元的数据仍为状态“0”。

如图16、图17A所示,在本发明中,当存储单元的数据是状态“2”时,第1页和第2页的数据设定为“0”、“0”。当存储单元的数据是状态“3”时,第1页和第2页的数据设定为“1”、“0”。当读出存储单元的数据时,首先读出第2页的数据,然后读出第1页的数据。

在读出第2页的数据时,若存储单元的数据是状态“0”或状态“1”,则读出的数据为“1”。若存储单元的数据是状态“2”或状态“3”,则读出的数据为“0”。因此,第2页的数据读出,可由存储单元的数据是状态“1”以下或状态“2”以上的1次动作来判断。

在读出第1页的数据时,若存储单元的数据是状态“0”或状态“3”,则读出的数据为“1”。若存储单元的数据是状态“1”或状态“2”,则读出的数据为“0”。因此,第1页的数据,可以由存储单元的数据是状态“0”或状态“1”以上的判断,以及存储单元的数据是状态“2”以下或状态“3”的判断来读出。也就是,第1页的数据,可用合计2次的动作读出。

进行擦除动作的存储单元的数据为状态“0”,在地址中指定第1、第2页的其中任一个时,读出的数据为“1”。

2位(第1页、第2页)的转换由地址A9进行。例如,使地址A9为低电平,则指定第1页,使地址A9为高电平,则指定第2页。

多值存储器情况下,必须根据写入数据正确控制存储单元的阈值电压。因此,在存储单元写入数据时,在存储单元的控制栅极渐渐增加外加电压并写入数据。这种写入方法称为升压写入方法。

图18表示对于存储单元的升压写入方法的写入特性。纵轴表示单元的阈值电压,横轴表示写入电压(程序电压)。

擦除后的单元阈值电压(存储单元的数据是状态“0”)为-3.5V。如上所述,本实施例中,在存储单元的数据为从状态“0”到状态“3”时,在单元的控制栅极外加16V作为初始程序电压。此后,每提高0.2V写入电压进行写入时,阈值电压沿着图中的“0”→“3”上升。另外,在存储单元的数据为从状态“0”到状态“1”时,使初始写入电压为14V开始写入。这是因为数据是状态“1”的阈值电压为0.2V。因此,使初始写入电压为16V开始写入时,在第3步和第4步之间数据为状态“1”的阈值电压,具有溢出程序的可能性。为了避免这种情况,使初始写入电压为14V。

第1页写入时,存储单元的数据从状态“0”移动到状态“1”。因此,在13次的写入次数,存储单元数据达到状态“1”的阈值。第2页写入时,存储单元的数据为状态“0”→“3”和“1”→“2”。这时,由于在状态“0”→“3 ”写入到比“0”→“1”较高的位置,则可将初始写入电压提高到16V。

如图17B所示,在将存储单元的数据从状态“0”变化到状态“3”时写入次数是11次,在将存储单元的数据从状态“1”变化到状态“2”时写入次数是6次。因此,第2页的写入可能是11次写入程序。这样,第1页和第2页的写入次数合计是24次。

如后所述,在同时写入第1页和第2页时,将存储单元的数据变化为状态“0”→“1”、“0”→“2”、“0”→“3”。因此,设定初始写入电压为14V。

如图17C所示,当存储单元的数据从状态“0”变化到状态“1”时写入次数是13次,当存储单元的数据从状态“0”变化到状态“2”时写入次数是17次,当存储单元的数据从状态“0”变化到状态“3 ”时写入次数是20次。因此,同时写入第1页和第2页时,用20次写入完成。在同时写第1页和第2页时,可以高速写入。

由于该第1页和第2页是同一块内的页,则可高速写入连续的2页。

(自动程序)

程序动作,如图19所示,首先输入作为数据输入指令的“80h”(h表示16进数),在全部数据存储电路310~31n/z的第1锁存电路LAT(A)中,置位数据“1”(不进行写入)。此后,根据信号ALE和信号WE的触发,输入地址和数据。在由列地址指定的数据存储电路,串行供给数据。

当从外部输入的数据是表示不进行写入的数据“1”时,图5所示数据存储电路的结点NC为高电平。当从外部输入的数据是表示进行写入的数据“0”时,结点NC为低电平。以后,第1锁存电路LAT(A)的数据作为结点NC的电位。

此后,如图19所示,输入作为自动程序实行指令的“10h”,开始自动程序。ECC代码使用时,“10h”指令输入后,通过ECC代码发生电路8自动建立ECC代码,并将该代码供给数据存储电路。然后,开始自动程序动作。

如图20所示,倍速程序动作,输入数据输入指令“80h”、地址、数据后,由于输出伪Busy信号,则输入指令“11h”。该伪程序在1.5μs的短时间,输出Busy信号。ECC代码使用时,在该指令“11h”后,产生ECC代码,并将该代码供给数据存储电路。因此,Busy信号的时间为比1.5μs较长的时间。

用改变阵列地址(A15、A16)进行4次将上述指令“80h”、地址、数据、指令“11h”的输入。但是,最后仅输入指令“10h”代替指令“11h”,实行自动程序。在第2次以后的指令“80h”,第1锁存电路LAT(A)不复位。

块地址(A17-A26),每次输入任意地址。图1所示行地址寄存器18,当输入下一个地址时,消除前一个地址。因此,图1所示阵列块锁存电路19,在各阵列每个地址输入锁存块地址。

在自动程序指令“10h”输入后,进行程序动作。然而,本存储器是多值存储器,在1个存储单元中存储2位数据。如前述所示,该2位被分配在地址A9。也就是,地址A9为低电平时指定第1页,地址A9为高电平时指定第2页。第1、第2页的写入顺序如图21、图22所示。本存储器首先写入第1页的数据,然后写入第2页的数据。首先,用图21、图22概略说明第1、第2页的程序。

图21所示第1页的程序中,在各数据存储电路310~31n/2置位的数据,在存储单元实施程序(ST1),然后,进行写入是否充分的检验读出(ST2)。也就是,读出存储单元的数据,并锁存在数据存储电路的第1锁存电路LAT(A)中。此后,在将不良块替换为块冗余前的测试工序中,对第1锁存电路LAT(A)锁存的低电平数据的数目即检验不合格数目进行计数。当该计数值在规定值(本例中,列冗余是4个时是4,列冗余是8个时是8)以上时,再次反复进行程序检验。当计数值是规定值以下时,程序动作结束(ST4)。除测试以外,判别各第1锁存电路LAT(A)锁存的数据是否是“1”(ST5)。其结果,若各第1锁存电路LAT(A)锁存的数据都不是“1”,则反复进行上述动作,若全部是“1”时,则第1页的程序结束。

在图22所示第2页的程序中,首先实行内部数据装入(ST11)。在该内部数据装入中,在各数据存储电路310~31n/2的第1锁存电路LAT(A)置位数据后,第1页的程序中写入的数据在数据存储电路的第2锁存电路LAT(B)读出。此后,与第1页同样进行程序(ST12)。然后,用检验读出1,检验存储单元的数据是否为状态“2”(ST13)。接着,用检验读出2,检验存储单元的数据是否为状态“3”(ST14)。以下,进行与第1页的程序同样的动作(ST15~ST17)。

部分优良品的不良块在测试后切断熔丝109。因此,当存取该不良块时,不选择该不良块。为此,以OK检验结束。

以下详细说明第1、第2页的程序。该说明中,省略图21所示步骤ST3、ST4以及图22所示步骤ST15、ST16。

(第1页自动程序)

图23表示第1页程序时的各部分动作顺序。如图5、图23所示,设供给数据存储电路的晶体管61h栅极的信号BLC1为VCC+Vth,设信号BLSA为Vpass,设BLTR为VCC。当第1锁存电路LAT(A)存储数据“1”(不进行写入)时,位线BL的电位为VCC。当存储数据“0”(进行写入)时,位线电位为接地电位VSS。并且,与被选择的字线连接,非选择页(位线为非选择)的单元不进行写入。因此,与这些单元连接的位线电位是与供给数据“1”的位线同样的电位VCC。

通过图1所示的CG驱动电路9,在选择线SG1外加VCC,在选择线SG2外加VSS,在选择CG线外加VPGM(20V),在非选择字线外加Vpass(10V)。由块选择电路6选择的块(倍速时,在各阵列有1个)的选择线SG1为VCC,选择字线为VPGM(20V),非选择字线为VPASS(10V)。当位线为VSS时,单元的通道为VSS,字线为VPGM。因此,该单元实施程序。当位线为VCC时,由于单元的通道不是VSS并且VPGM上升,通过耦合为VPGM/Z。因此,该单元不实施程序。

这样,写入数据“0”的存储单元,如图16、图17A所示,为状态“1”。写入数据“1”的存储单元仍为状态“0”。

(第1页程序检验)

以下,实行程序检验读出(图21、ST2)。

图24表示程序检验读出的动作,图25表示程序检验读出时各部分的顺序。

第1页程序检验读出,如图16所示,将比读出时的电位b稍高的电位b,供给选择的字线。以后“’”表示检验电位,认为是比读出时的字线电位稍高的值。

如图25所示,将电压Vread供给被选择块内的非选择字线和选择线SG1。供给图5所示数据存储电路的晶体管61g栅极的信号BIAS为高电(1.6V),位线预通电。

此后,使存储单元源极侧的选择线SG2为高电平(Vread)。在存储单元的阈值电压比电位b’高时,由于存储单元关断,则位线仍为高电平。在存储单元的阈值电压未达到电位b’时,由于存储单元导通,则位线电位为低电平(VSS)。

当进行写入时,在图5所示第1锁存电路LAT(A)的结点NA锁存低电平(数据“0 ”)。当不进行写入时,在结点NA锁存高电平(数据“1 ”)。因此,设供给晶体管611的电流通路的信号VREG为VCC,供给栅极的信号VRFY1为高电平时,不进行写入时的位线从浮置状态固定在高电平。该动作后,位线电位写入第1锁存电路LAT(A)。在第1锁存电路LAT(A)锁存高电平的情况下,当存储单元的电位达到阈值电压时,不进行写入。在第1锁存电路LAT(A)锁存低电平时,仅是存储单元的电位未达到阈值电压的情况。

当第1锁存电路LAT(A)为低电平时,反复进行上述程序动作和检验读出动作,直到再次进行写入动作的全部数据存储电路的数据达到高电平(图21,ST1~ST5)。

(第2页程序)

第2页程序与第1页程序一样,从外部输入第2页的数据。这些数据存储在各数据存储电路310~31h/z的第1锁存电路LAT(A)。

在第2页程序动作中,与第1页程序动作很大的不同是内部数据装入(ST11)。第2页程序动作根据第1页程序动作结果而有所不同。

如图16、图17A所示,在第1页存储单元的数据为状态“0”的情况下(没有进行写入动作),第2页的数据为“0”(进行写入)时,设定存储单元的数据为状态“3”。第2页的数据为“1”(没有进行写入)时,设存储单元的数据仍为状态“0”。在存储单元的数据为状态“1”的情况下(在第1页进行了写入动作),第2页的数据为“0”时(进行写入),设定存储单元的数据为状态“2”。第2页的数据为“1”时(没有进行写入),存储单元的数据仍为状态“1”。

这样,第2页程序动作根据第1页程序的动作结果而有所不同。因此,在将第2页数据写入单元前,检查并存储存储单元的数据是状态“0”或状态“1”是必要的。为此,读出存储单元的数据,并进行装入图5所示数据存储电路的第2锁存电路LAT(B)的内部数据装入(ST11)。该内部数据装入是将图16所示电位a供给字线,进行读出动作。将该读出结果存储在数据存储电路的第2锁存电路LAT(B)。

图26A表示内部数据装入时的动作,图27表示内部数据装入时各部分的顺序。参照图26A、图27说明内部数据装入的动作。

内部数据装入时,首先,将图5所示数据存储电路的第1锁存电路LAT(A)的数据存储在非选择侧的位线。然后,在字线外加电位a,进行读出动作。将该结果存储在第1锁存电路LAT(A)。当存储单元的数据为“0”时第1锁存电路LAT(A)锁存数据“0”,当存储单元的数据为“1”时第1锁存电路LAT(A)存储数据“1”。

在第2锁存电路LAT(B)的数据为“1”后,在信号BLC2外加中间电位1V,使信号VREG为电压VSS,使信号VRFY1为高电平。这样,第1锁存电路LAT(A)为数据“1”,也就是在存储单元的数据为“1”时第2锁存电路LAT(B)的数据为“0”。第1锁存电路LAT(A)的数据为“0”,也就是存储单元的数据为状态“1”时第2锁存电路LAT(B)的数据仍是“1”。此后,将存储在非选择侧的位线的数据返回第1锁存电路LAT(A)。

然后,与第1页程序同样,在各部分外加所定电压。在该状态下,根据存储在第1锁存电路LAT(A)的第2页数据,对已选择的全部单元进行写入(图22,ST12)。

(第2页检验)

第2页检验具有第1检验读出(ST13)和第2检验读出(ST14)共2个检验读出。第1检验读出(ST13)检验存储单元的数据是否是状态“2”。第2检验读出(ST14)检验存储单元的数据是否是状态“3”。

(第2页第1检验读出)

图26B表示第2页第1检验读出的动作,图28表示第2页第1检验读出时各部分的顺序。

该检验如图16所示,在字线外加电位b’,进行读出动作。其结果,当存储单元的阈值电压达到b’时位线为高电平,当阈值电压未达到b’时为低电平。这时,使存储单元的数据为状态“3”的单元也关断。因此,检验为OK。另外,在第1页的写入动作时不写入,则与数据为状态“0”的存储单元连接的位线电位为低电位。

也就是,在第1页的写入动作时不写入,当存储单元的数据为状态“0 ”时,通过上述内部数据装入,第2锁存电路LAT(B)的结点ND为高电平。在这种状态下设供给图5所示晶体管61u的电流通路的信号VREG为图28所示的接地电压VSS,设供给栅极的信号VRFY2为高电平。这样,在第2锁存电路LAT(B)的结点ND为高电平时,晶体管61t导通,位线被强制为低电平。

与第1页检验动作同样,设信号VREG为电源电压VCC,设供给晶体管611栅极的信号VRFY1为高电平。这样,当第1锁存电路LAT(A)的结点NC锁存高电平(不进行写入)时,晶体管61k导通。因此,位线为高电平。该动作以后,将位线电位写入第1锁存电路LAT(A)。

通过上述动作,第1锁存电路LAT(A)锁存高电平,如图26B所示,由于存储单元的数据为状态“2”,则当进行写入的单元达到阈值电压时,不进行写入。在第1锁存电路LAT(A)锁存低电平时,由于存储单元的数据为状态“2”,则当进行写入的单元未达到阈值电压时,进行写入的存储单元的数据为状态“3”。

(第2页第2检验读出)

图26C表示上述第2页第2检验读出动作,图25表示此时各部分的顺序。

该检验与第1页检验动作完全相同。这是因为除了数据为状态“3”的单元以外,不存在比图16所示电位C’高的单元。为了检验存储单元的数据是否为状态“1”,第1页检验在字线外加电位a’。然而,这时为了检验存储单元的数据是否为状态“3”,在字线外加电位c’。

其结果,第1锁存电路LAT(A)锁存高电平,如图26C所示,当单元达到阈值电压时,不进行写入(从开始第1锁存电路LAT(A)即锁存高电平)。同样,第1锁存电路LAT(A)锁存低电平,当单元未达到阈值电压时,即存储单元的数据为状态“3”时写入,当未达到状态“3”的NG,将在状态“2”写入存储单元的数据。

第2页检验,进行第1检验读出和第2检验读出的2次检验读出。第1检验读出是将存储单元的数据写入状态“2”的检验读出,第2检验读出是写入状态“3”的检验读出。第1锁存电路LAT(A)为低电平时再次进行写入动作。这样,反复进行该程序动作和检验动作,直到全部数据存储电路的数据为高电平(图22,ST12~ST17)。

然而,存储单元的数据为状态“3”时,阈值电压高。因此,该存储单元不容易写入。在反复进行的程序检验动作中,开始的数次可以省略存储单元的数据是否为状态“3”的检验动作。反复进行数次程序检验动作,将阈值电压比状态“3”低的状态“2”的数据写入的存储单元,即应结束写入。因此,写入状态“2”的数据的存储单元,反复进行数次程序检验动作后,即可省略检验。

(读出动作)

图29表示读出动作的顺序。

读出动作如图29所示,首先,输入读出指令“00h”后,从输入地址开始。读出动作中,由地址指定的页的全部单元的数据,分别在数据存储电路310~31n/z中读出。此后,信号BUSY解除,处于准备就绪状态,根据信号RE的触发,按照由列地址指定的顺序,从数据存储电路输出数据。

图30表示倍速读出动作的顺序。该倍速读出是在一次读出动作中,在各数据存储电路全部读出4个存储单元阵列内的页的单元。然后,当信号BUSY解除并处于准备就绪状态时,根据信号RE的触发,按照由列地址指定的顺序,从数据存储电路输出数据。到了1个存储单元阵列的最终列地址,输出短信号BUSY(1.5μs)。此后信号BUSY解除并处于准备就绪状态时,根据信号RE的触发,输出下一个存储单元阵列的数据。反复该动作,可以一次读出,顺序输出4页的数据。但是,该4页是不连续的4页。因此,如图6C、6D所示,必须对地址予以安排。

本实施例的存储器是多值存储器,1个单元存储2位数据。该2位数据由地址A9指定。也就是,如上所述,当地址A9为高电平时指定第2页。地址A9为低电平时指定第1页。

图31是概略表示读出动作的流程图。

读出动作,在输入读出指令“00h”后,从输入地址开始(ST21)。当地址A9为高电平时,读出第2页的数据(ST25)。该第2页读出,如图16、图17A所示,判别存储单元的数据是否是“2”以下。

当地址A9为低电平时,读出第1页的数据。第1页的读出动作具有2个读出动作。第1读出动作(第1页读出1)(ST22),如图16、图17A所示,判别存储单元的数据是“2 ”以下或是“3 ”。第2读出动作(第1页读出2)(ST24),如图16、图17A所示,判别存储单元的数据是“1”或是“2”以上。

与部分优良品的不良块对应的块选择电路的熔丝109被切断。对于2值和4值的第2页读出动作,当存取不良块时,不选择该不良块,不流过电流。因此,自动输出数据“0”。然而,对于4值存储器的第1页的读出动作,通过第1、第2读出动作(第1页读出1、2),输出数据“1”。根据从图12所示倒相电路114输出的信号FUSECUT,可以知道是否切断熔丝109。当切断熔丝时,仅进行第1读出动作(第1页读出1),不进行第2读出动作(第1页读出2),输出数据“0”(ST23)。

以下参照图32到图35,详细说明读出动作。

(第2页读出)

第2页读出,如图16所示,在选择的字线外加读出时的电位C。

接着,如图34所示,在选择的块内的非选择字线和选择线SG1外加Vread(4.5V)。在图5所示数据存储电路晶体管61g的栅极外加高电平的BIAS,使位线予通电。然后,使单元的源极侧的选择线SG2为高电平。当单元的阈值电压比电位C高时,由于单元关断,则位线仍是高电平。当单元的阈值电压未达到电位C时,由于单元导通,则位线为接地电位VSS。如图17A所示,定义存储单元的数据和存储单元的阈值电压。在存储单元的数据是状态“0”或状态“1”时,位线电位为低电平,当是状态“2”或状态“3”时,位线电位为高电平。

然后,在第1锁存电路LAT(A)写入这些位线的电位。图5所示第1锁存电路LAT(A)的结点NA,如图32所示,当存储单元的数据是状态“0”或状态“1”时为低电平,当是状态“2”或状态 “3”时为高电平。结点NB是与结点NA相反的电平。当列选择线CSL为高电平时,晶体管610、61n导通,将结点NB、NA的电位输出到输出缓冲器4。

(第1页读出)

以下,读出第1页数据。当由第1页读出输出的数据是“1”时,如图17A所示,存储单元的数据是状态“0”或状态“3”。

因而,最初判断存储单元的数据是状态“2”以下或状态“3”。下一个必定判断存储单元的数据是状态“0”或状态“1”以上。

{第1读出动作}

第1读出动作判断存储单元的数据是状态“2”以下或是状态“3”。

图33A表示第1页的第1读出动作,图23的左一半表示这时的顺序。

图35中的顺序与图34一样。

首先,为了检查存储单元的数据是状态“2 ”以下或是状态“3”,在字线外加电位C,读出存储单元的数据。其结果,第1锁存电路LAT(A)锁存高电平,如图33A所示,存储单元的数据仅是状态“3”。当第1锁存电路LAT(A)锁存低电平时,存储单元的数据是状态“0 ”、状态“1”、状态“2”的其中之一。

{第2读出动作}

第2读出动作判断存储单元的数据是状态“0 ”或是状态“1”以上。图33B表示第1页的第2读出动作,图35的右一半表示这时的顺序。

为了检查存储单元的数据是状态“0 ”或是状态“1”以上,在字线外加电位a,读出存储单元的数据。其结果,第1锁存电路LAT(A)锁存低电平,存储单元的数据仅是状态“0”。当第1锁存电路LAT(A)锁存高电平时,存储单元的数据是状态“1”、状态“2”、状态“3”的其中之一。

这里,使图5所示信号VREG为接地电位VSS,使供给晶体管611的栅极的信号VRFY1为高电平。当第1锁存电路LAT(A)锁存高电平时,也就是在第1页的第1读出动作中,存储单元的数据是状态“3 ”时,位线被强制在低电平。其结果,当存储单元的数据是状态“0”或状态“3 ”时,位线的电位为低电平。当存储单元的数据是状态“1”或状态“2”时,位线的电位为高电平。

在第1锁存电路LAT(A)写入这些位线电位,如图33B所示,当存储单元的数据是状态“0 ”、状态“3”时,第1锁存电路LAT(A)的结点NA为低电平。当是状态“1”、状态“2 ”时,结点NA为高电平。结点NB是与结点NA相反的电平。当列选择线CSL为高电平时,晶体管61o、61n导通,将结点NB、NA的电位输出到输出缓冲器4。

(自动擦除)

图36表示擦除动作。擦除动作,以块单位进行擦除。首先,输入选择块的块选择指令“60h”,然后,输入块地址。当输入自动擦除的实行指令“Doh”时,开始自动擦除。

图37表示倍速擦除动作。倍速擦除动作,更换阵列地址(A15、A16),3次输入块选择指令“60h”、块地址。然后,通过输入块选择指令“60h”、地址、自动擦除实行指令“Doh”,开始倍速擦除动作。

块地址(A17~A26),每次输入任意的地址,但当图1所示行地址寄存器18输入下一个地址时,消除前面的地址。因此,在每个地址输入,用图1所示阵列块锁存电路19在每个存储单元阵列锁存块地址。

图38表示自动擦除的流程图。首先,进行选择的块的擦除动作(ST31)。然后,对与数据存储电路连接的2条位线(BLi、BL+1)中的1条位线(BLi)进行擦除检验读出动作,当未充分擦除时,再次进行擦除(ST32~ST35、ST31)。当存储单元充分擦除时,再对其他位线(BLi)进行擦除检验读出动作(ST36)。其结果,当未充分擦除时,再次进行擦除(ST36~ST39、ST31)。在存储单元充分擦除时结束。

在将不良块替换为块冗余前的测试工序中,在各擦除检验动作ST33、ST36之后,对第1锁存电路LAT(A)锁存的低电平数据的数目,也就是检验失误的数目进行计数。当该计数值是规定值(本例中,列冗余是4个时是4,列冗余是8个时是8)以上时,再次反复进行擦除(ST34、ST38)。

部分优良品的不良块,测试后熔丝109被切断。因此,在存取该不良块时,不选择该不良块。第1锁存电路LAT(A)其数据为低电平,擦除检验不是OK。然而,根据从图12所示倒相电路114输出的信号FUSECUT,可以知道是否切断熔丝109。当根据信号FUSECUT切断熔丝109时,检验为OK。

(擦除)

图39表示擦除动作的顺序。进行擦除动作时,存储单元的数据为状态“0”,在第1页、第2页、任一页进行读出时,都输出数据“1”。

(擦除检验)

图40表示擦除检验动作的顺序。1次擦除检验动作,对与数据存储电路连接的2条位线(BLi、BL+1)中的1条位线(BLi)进行擦除检验读出动作。因此,使块内的全部字线WL为选择状态VSS。使单元的源极线SRC为VDD、选择线SG1为Vread之后,单元的源极侧的选择线SG2为Vread。在单元的漏极侧,即在位线,输出16个单元中最浅的单元的-Vth的电位。

这里,当第1锁存电路LAT(A)为高电平、信号BLC1为1.6V、Vth为-0.6V以下(擦除充分)时,第1锁存电路LAT(A)仍为高电平。然而,当Vth为-0.6V 以上(擦除不充分)时,第1锁存电路LAT(A)其数据为低电平。当全部第1锁存电路LAT(A)的数据为高电平时,擦除检验为OK。

(升压移动测试)

图41表示设置在图1所示控制电压发生电路14内的电压设定电路。如前所述,控制电压发生电路14具有升压电路。该升压电路产生程序电压Vpgm、擦除电压Vera、以及电压Vpass。如前所述,程序电压Vpgm分数阶段升压。

然而,存储单元的特性根据工序的变动等而变化,升压电路产生的上述各电压也随工序的变动等而变化。因此,必须根据芯片的特性设定程序电压Vpgm、擦除电压Vera、以及电压Vpass。在向冗余区域替换前的测试时,进行自动程序和自动擦除,根据其结果,进行程序开始电压的设定和擦除开始电压的设定。

图41所示电压设定电路,可以根据芯片特性设定最适合的程序电压Vpgm、电压Vpass、以及擦除电压Vera。

该电压设定电路由初始数据存储用熔丝161、计数器162构成。上述初始数据存储用熔丝161用熔丝设定用于控制电压Vpgm、电压Vpass、以及电压Vera的初始数据。这些熔丝根据自动程序和自动擦除的结果进行程序。这些自动程序和自动擦除在向冗余区域替换前的测试时进行。在熔丝设定的上述初始数据,当产生电压Vpgm、电压Vpass、以及电压Vera时,在计数器162预置。计数器162由预置计数器构成。将信号CT1、CT2供给该计数器162。该计数器162的输出信号,例如连接于升压电路163的限幅器,改变该限幅器的限定值。

上述信号CT1,例如在1次程序或擦除动作结束、检验为NG时供给。计数器162根据信号CT1增加。根据计数器162的输出信号,控制限幅器,从升压电路163输出高1级的电压。

上述信号CT2表示本实施例的特征。也就是,在测试状态时,按数级增加从初始数据存储用熔丝161读出数据的程序开始电压和擦除开始电压。

以往,调整后的加速试验,一律加稍高的程序开始电压和擦除开始电压。然而,由于使用信号CT2,可具有用于加速试验的±数级(Step)变化的功能。因此,可对各个芯片加适当的电压。

在使电压Vpass、Vpgm为比由初始数据存储用熔丝161设定的数据低的电压的程序非选择的加速试验中,必须在负方向增加计数器162。然而,可在该负方向增加的计数器是复杂的。因此,使用信号CT2,通过按(1周)-(数级)增加计数器,设定在比由初始数据存储用熔丝161设定的数据较低的电压。采用这种构成,不使用复杂的计数器,即可容易地设定所要求的值。

上述第1实施例中,存储单元阵列1具有多个块bkl0-bkl23、多个块冗余blkRD0~blkRD9。在各块bkl0~bkl23和各块冗余blkRD0-blkRD9,设置块选择电路6a。各块选择电路6a具有熔丝109,通过切断该熔丝109,可将任意块冗余blkRD0~blkRD9设定为存储用于保密的信息的ROM块。因此,能够可靠地将保密信息设定在ROM块中。

通过按照要求切断设置在控制部15的ROM块的禁止写入电路15a、禁止擦除电路15b的熔丝151c、152c,可以适当地使ROM块为禁止写入、禁止擦除。

通过切断与不良块对应的块选择电路6a的熔丝109,能够可靠地使不良块为非选择。因此,在程序(倍速自动程序)和擦除(倍速自动擦除)时,可以防止检验反复进行到最大次数。

上述实施例,可以通过设置在控制部15的熔丝,设定使用ECC和不使用ECC的情况。当不使用ECC时,可以将ECC使用的21位用于冗余,能够提高不良的救济效率。

在冗余替换前的测试工序中,进行自动程序和自动擦除时,在存在列不良的情况下,用于该不良列的检验为NG。然而,上述实施例中,忽略列冗余数在规定值以下时的检验结果。因此,在冗余替换前的测试时,可以进行自动程序和自动擦除,并可据此进行程序开始电压的设定和擦除开始电压的设定。

而且,将信号CT2供给计数器162,通过该信号CT2,具有使由初始数据存储用熔丝161固定的程序开始电压和擦除开始电压用于加速试验的±数级的功能。因此,如以往一样,在调整后的加速试验中,与一律加稍高的程序开始电压和擦除开始电压的情况比较,具有可以加适合各个芯片的电压的优点。

(第2实施例)

下面说明本发明的第2实施例。第1实施例在1页写入动作时,写入1位的数据。在第2实施例中,当1页的写入动作时写入1位、2页同时写入动作时可连续写入2位,同时写入连续页时可高速写入。

第1实施例中,分别对第1页、第2页进行程序时,第1页的程序写入1个阈值,第2页的程序写入2个阈值。第1页、第2页同时程序写入3个阈值。

图42表示适用于第2实施例的数据存储电路的构成。这里,为了简化说明,数据存储电路具有3个锁存电路。 (在2个锁存电路可一次写入3个阈值)。

图42中,与图5相同部分附与相同符号,仅对不同部分予以说明。图42所示数据存储电路还具有第3锁存电路LAT(C)。第3锁存电路LAT(C),在上述结点NE与晶体管62f的电流通路的一端连接。将信号BLC3供给该晶体管62f的栅极。在该晶体管62f的电流通路的另一端,通过P沟道M0S晶体管62j与端子62i连接。将电压VCC供给该端子62i。将信号PRSTB3供给上述晶体管62j的栅极。

在上述晶体管62f的电流通路的另一端与第3锁存电路LAT(C)连接。该第3锁存电路LAT(C)由2个同步脉冲倒相电路62k、621构成。同步脉冲倒相电路62k由信号SEN3、SEN3B控制,同步脉冲倒相电路621由信号LAT3、LAT3B控制。该第3锁存电路LAT(C)锁存从存储单元读出的数据。

在结点NE,串联连接晶体管62q、62h。晶体管62q的栅极与上述第3锁存电路LAT(C)的结点NF连接,将信号VRFY3供给晶体管62h的栅极。将信号VREG供给晶体管62h的电流通路。这些晶体管62q、62h根据第3锁存电路LAT(C)锁存的数据设定位线的电位。

说明上述构成的动作。

(第1页、第2页同时程序)

图43表示第1页、第2页同时程序的动作顺序,图44、图45表示各部分的动作。图46表示流程图。

第1页、第2页同时程序时,与图19同样,首先,数据输入指令“80h”之后,输入地址、数据。当从外部输入的数据是表示不进行写入的数据“1”时,图42的第1锁存电路LAT(A)的结点NC为高电平。当从外部输入的数据是表示进行写入的数据“0”时,结点NC为低电平。

然后,如图44所示,将第1锁存电路LAT(A)锁存的数据移动到第2锁存电路LAT(B)。因此,与上述倍速程序同样,输入指令“12h”。该指令也是较短的1.5μs。这时,将第1锁存电路LAT(A)的内容传送到第2锁存电路LAT(B)。此后,再次输入指令“80h”、地址、数据。这里的地址是前面输入的地址相邻页的地址(不同于A9)。该数据被锁存在第1锁存电路LAT(A)。然后,输入自动程序实行指令“10h”,开始自动程序。

在检验存储单元的数据是否为状态“1”时,写入状态“2”、“3”的存储单元为OK。将其强制为NG。因此,使对应于写入状态“2”、“3”的存储单元的第2锁存电路LAT(B)为数据“1”。在检验存储单元的数据是否为状态“2”时,写入状态“3”的存储单元为OK。因此,强制其为NG,对于写入状态“3”的存储单元,使第3锁存电路LAT(C)为数据“1”。

也就是,首先被第1锁存电路LAT(A)、第2锁存电路LAT(B)锁存的数据之一方或双方为表示写入的数据“0”时,使第1锁存电路LAT(A)为写入状态。

为了进行这些操作,如图45A所示,调换第2锁存电路LAT(B)和第3锁存电路LAT(C)的数据。其结果,写入状态“3”,第2锁存电路LAT(B)为高电平,写入状态“2”、“3”,第3锁存电路LAT(C)为高电平(ST41)。

然后,进行程序动作。该程序动作利用图23所示的顺序,与分别进行第1页、第2页的程序的情况完全相同(ST42)。

图45B、45C、45D表示检验动作。

在判别图45B所示存储单元的数据是否为状态“1”的检验中,写入状态“2”和状态“3”的存储单元为OK。然而,通过上述操作,写入状态“2”和状态“3”时,第3锁存电路LAT(C)为高电平。因此,使强制位线为低电平作为NG(ST43)。

在判别图45C所示存储单元的数据是否为状态“2”的检验中,写入状态“3”的存储单元为OK。然而,通过上述操作,写入状态“3”时,第2锁存电路LAT(B)为高电平。因此,使强制位线为低电平作为NG(ST44)。

在判别图45D所示存储单元的数据是否为状态“3”的检验中,为OK的仅是写入状态“3”的情况(ST45)。

因此,当第1锁存电路LAT(A)为低电平时,不再进行写入动作,直到全部数据存储电路的第1锁存电路LAT(A)的数据为高电平之前,反复进行该程序动作和检验动作(ST48)。

在将不良块替换为块冗余前的测试工序中,对被第1锁存电路LAT(A)锁存的低电平数据的数目,也就是检验失误的数目进行计数。当该计数值是规定值(本例中,列冗余是4个时为4,列冗余是8个时为8)以上时,再次反复进行程序检验,在规定值以下时,结束程序动作(ST46,ST47)。

(第1页、第2页倍速同时程序)

图47表示第1页、第2页同时程序并倍速程序的动作。这时与上述同样,首先,输入指令“80h”、地址、数据。该数据锁存在第1锁存电路LAT(A)中。然后,输入指令“12h”,输出信号BUSY。此后,将第1锁存电路LAT(A)的数据传送到第2锁存电路LAT(B)。再重新输入指令“80h”、地址(前面输入的地址相邻页的地址)、数据、指令“11h”,输出信号BUSY。改变阵列地址(A15、A16)进行4次该动作。最后,代替指令“11h”,输入自动程序实行指令“10h”,开始实际的程序。

上述第2实施例中,第1、第2页同时进行程序。因此,可缩短程序时间。

并且,通过实行倍速程序,更加缩短了程序时间。

第1、第2实施例中,块选择电路6a具有熔丝109,禁止写入电路15a和禁止擦除电路15b具有熔丝151c、152c,但是并不限定为熔丝,例如也可以使用EEPOM单元等非易失存储器。关于其他熔丝也是一样的。

对于熟悉本技术的人很容易发现其他的优点和变更。本发明具有多种表达形式,不限定于这里的特定描述和表示的实例。因此,除非超出了由本发明权利要求和其等同物限定的本发明概念的精神和范围,各种变更都是可以实现的。

Claims (5)

1.一种半导体存储装置,其特征是包含:

具有多个存储元件的多个块;

与上述各块对应设置的熔丝元件,

检出上述熔丝元件的状态的检出电路;

从上述各块的存储元件读出数据的读出电路,上述读出电路在通过上述检出电路检出上述熔丝元件未被切断时,输出上述块内的存储元件的数据,在检出上述熔丝元件被切断时,输出不取决于上述块内的存储元件的数据的一定值。

2.根据权利要求1所述的装置,其特征是还包含:

上述熔丝元件在对应的上述块有不良时被切断。

3.一种半导体存储装置,其特征是包含:

具有多个存储元件的多个块;

与上述各块对应设置的非易失性存储器,上述非易失性存储器存储第1逻辑电平或第2逻辑电平的数据;

检出上述非易失性存储器的存储状态的检出电路;

从上述各块的存储元件读出数据的读出电路,上述读出电路在通过上述检出电路检出上述非易失性存储器存储上述第1逻辑电平时,输出上述块内存储元件的数据,在检出上述非易失性存储器存储上述第2逻辑电平时,输出不取决于上述块内存储元件的数据的一定值。

4.根据权利要求3所述的装置,其特征是,

上述非易失性存储器在对应的上述块有不良时,存储上述第2逻辑电平的数据。

5.根据权利要求3所述的装置,其特征是,

上述非易失性存储器是EEPROM单元。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000297443A JP4184586B2 (ja) | 2000-09-28 | 2000-09-28 | 半導体記憶装置 |

| JP297443/2000 | 2000-09-28 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB011372443A Division CN1178228C (zh) | 2000-09-28 | 2001-09-20 | 非易失半导体存储装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN101154461A CN101154461A (zh) | 2008-04-02 |

| CN101154461B true CN101154461B (zh) | 2011-10-19 |

Family

ID=18779560

Family Applications (5)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN2007101802315A Expired - Lifetime CN101154461B (zh) | 2000-09-28 | 2001-09-20 | 半导体存储装置 |

| CN200710180232XA Expired - Lifetime CN101154465B (zh) | 2000-09-28 | 2001-09-20 | 半导体存储装置 |

| CNB2004100421793A Expired - Lifetime CN100431045C (zh) | 2000-09-28 | 2001-09-20 | 非易失半导体存储装置 |

| CN2007101802300A Expired - Lifetime CN101154459B (zh) | 2000-09-28 | 2001-09-20 | 半导体存储装置 |

| CNB011372443A Expired - Lifetime CN1178228C (zh) | 2000-09-28 | 2001-09-20 | 非易失半导体存储装置 |

Family Applications After (4)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN200710180232XA Expired - Lifetime CN101154465B (zh) | 2000-09-28 | 2001-09-20 | 半导体存储装置 |

| CNB2004100421793A Expired - Lifetime CN100431045C (zh) | 2000-09-28 | 2001-09-20 | 非易失半导体存储装置 |

| CN2007101802300A Expired - Lifetime CN101154459B (zh) | 2000-09-28 | 2001-09-20 | 半导体存储装置 |

| CNB011372443A Expired - Lifetime CN1178228C (zh) | 2000-09-28 | 2001-09-20 | 非易失半导体存储装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (8) | US6600676B2 (zh) |

| JP (1) | JP4184586B2 (zh) |

| KR (1) | KR100458411B1 (zh) |

| CN (5) | CN101154461B (zh) |

| TW (1) | TW543200B (zh) |

Families Citing this family (48)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5362545A (en) * | 1993-03-24 | 1994-11-08 | Tingley Daniel A | Aligned fiber reinforcement panel for structural wood members |

| USRE40110E1 (en) * | 1999-09-20 | 2008-02-26 | Kabushiki Kaisha Toshiba | Nonvolatile semiconductor memory device for storing multivalued data |

| FR2810438B1 (fr) * | 2000-06-19 | 2002-09-06 | St Microelectronics Sa | Circuit de detection d'usure |

| JP4184586B2 (ja) | 2000-09-28 | 2008-11-19 | 株式会社東芝 | 半導体記憶装置 |

| DE10162308A1 (de) * | 2001-12-19 | 2003-07-03 | Philips Intellectual Property | Verfahren und Anordnung zur Zugriffssteuerung auf EEPROMs sowie ein entsprechendes Computerprogrammprodukt und eine entsprechendes computerlesbares Speichermedium |

| JP2005108273A (ja) | 2003-09-26 | 2005-04-21 | Toshiba Corp | 不揮発性半導体記憶装置 |

| US7139864B2 (en) | 2003-12-30 | 2006-11-21 | Sandisk Corporation | Non-volatile memory and method with block management system |

| JP4170952B2 (ja) | 2004-01-30 | 2008-10-22 | 株式会社東芝 | 半導体記憶装置 |

| US7009889B2 (en) | 2004-05-28 | 2006-03-07 | Sandisk Corporation | Comprehensive erase verification for non-volatile memory |

| US7336531B2 (en) * | 2004-06-25 | 2008-02-26 | Micron Technology, Inc. | Multiple level cell memory device with single bit per cell, re-mappable memory block |

| KR100632946B1 (ko) * | 2004-07-13 | 2006-10-12 | 삼성전자주식회사 | 불 휘발성 메모리 장치 및 그것의 프로그램 방법 |

| US7272050B2 (en) * | 2004-08-10 | 2007-09-18 | Samsung Electronics Co., Ltd. | Non-volatile memory device and erase method of the same |

| US7145816B2 (en) * | 2004-08-16 | 2006-12-05 | Micron Technology, Inc. | Using redundant memory for extra features |

| US7298648B2 (en) * | 2004-11-19 | 2007-11-20 | Samsung Electronics Co., Ltd. | Page buffer and multi-state nonvolatile memory device including the same |

| KR100648281B1 (ko) * | 2005-01-14 | 2006-11-23 | 삼성전자주식회사 | 보안 리던던시 블록을 구비한 낸드 플래시 메모리 장치 |

| EP1750278B1 (en) * | 2005-07-28 | 2009-11-11 | STMicroelectronics S.r.l. | Method of programming a four-level flash memory device and a related page buffer |

| KR100630537B1 (ko) * | 2005-08-09 | 2006-10-02 | 주식회사 하이닉스반도체 | 듀얼 페이지 프로그램 기능을 가지는 플래시 메모리 장치의페이지 버퍼 회로 및 그 프로그램 동작 방법 |

| JP4991131B2 (ja) * | 2005-08-12 | 2012-08-01 | 株式会社東芝 | 半導体記憶装置 |

| JP4647446B2 (ja) * | 2005-09-20 | 2011-03-09 | 富士通株式会社 | 半導体記憶装置 |

| JP4846314B2 (ja) * | 2005-09-22 | 2011-12-28 | 株式会社東芝 | 半導体記憶装置 |

| KR100660544B1 (ko) * | 2005-10-25 | 2006-12-22 | 삼성전자주식회사 | 신뢰성을 향상시킬 수 있는 플래시 메모리 장치 |

| JP4455492B2 (ja) | 2005-12-27 | 2010-04-21 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| KR100757411B1 (ko) * | 2006-02-03 | 2007-09-11 | 삼성전자주식회사 | 옵션 퓨즈 회로를 이용한 반도체 메모리 장치의 전압재설정 회로 및 그 방법 |

| US7453723B2 (en) | 2006-03-01 | 2008-11-18 | Micron Technology, Inc. | Memory with weighted multi-page read |

| JP4976764B2 (ja) * | 2006-07-05 | 2012-07-18 | 株式会社東芝 | 半導体記憶装置 |

| US7369434B2 (en) * | 2006-08-14 | 2008-05-06 | Micron Technology, Inc. | Flash memory with multi-bit read |

| US7701770B2 (en) * | 2006-09-29 | 2010-04-20 | Hynix Semiconductor Inc. | Flash memory device and program method thereof |

| JP2008097696A (ja) * | 2006-10-11 | 2008-04-24 | Elpida Memory Inc | 半導体装置 |

| JP4871701B2 (ja) * | 2006-11-02 | 2012-02-08 | 株式会社日立製作所 | ストレージシステム |

| KR100801035B1 (ko) * | 2006-12-14 | 2008-02-04 | 삼성전자주식회사 | 멀티 레벨 셀의 프로그램 방법, 페이지 버퍼 블록 및 이를포함하는 불휘발성 메모리 장치 |

| JP2008192212A (ja) * | 2007-02-01 | 2008-08-21 | Spansion Llc | 半導体装置およびその制御方法 |

| JP5032155B2 (ja) | 2007-03-02 | 2012-09-26 | 株式会社東芝 | 不揮発性半導体記憶装置、及び不揮発性半導体記憶システム |

| US7916544B2 (en) | 2008-01-25 | 2011-03-29 | Micron Technology, Inc. | Random telegraph signal noise reduction scheme for semiconductor memories |

| US20100180183A1 (en) * | 2009-01-12 | 2010-07-15 | Macronix International Co., Ltd. | Circuit for reducing the read disturbance in memory |

| CN102081972B (zh) * | 2009-11-27 | 2015-05-20 | 上海华虹集成电路有限责任公司 | 一种eeprom器件测试电路及其测试方法 |

| JP2011138569A (ja) * | 2009-12-25 | 2011-07-14 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP2011150749A (ja) * | 2010-01-20 | 2011-08-04 | Toshiba Corp | 不揮発性半導体記憶装置 |

| CN105788638A (zh) * | 2011-03-04 | 2016-07-20 | 瑞萨电子株式会社 | 半导体器件 |

| JP2013229080A (ja) * | 2012-04-26 | 2013-11-07 | Toshiba Corp | 半導体記憶装置および半導体記憶装置のテスト方法 |

| US9111624B2 (en) * | 2013-03-22 | 2015-08-18 | Katsuyuki Fujita | Semiconductor memory device |

| US20150078178A1 (en) * | 2013-09-16 | 2015-03-19 | Tachyon Networks Incorporated | Software platform for implementation and control of satellite communication systems |

| KR102210520B1 (ko) * | 2013-12-19 | 2021-02-02 | 삼성전자주식회사 | 비휘발성 메모리 장치 및 그것의 소거 방법 |

| US9281027B1 (en) * | 2014-10-10 | 2016-03-08 | Arm Limited | Test techniques in memory devices |

| US9817593B1 (en) | 2016-07-11 | 2017-11-14 | Sandisk Technologies Llc | Block management in non-volatile memory system with non-blocking control sync system |

| CN106708592B (zh) * | 2017-01-25 | 2021-12-03 | 北京鸿智电通科技有限公司 | 一种微控制器以及用于微控制器的代码烧录方法 |

| KR20200016777A (ko) * | 2018-08-07 | 2020-02-17 | 삼성전자주식회사 | 안전 로직을 포함하는 장치 |

| US11093164B2 (en) * | 2019-08-27 | 2021-08-17 | Micron Technology, Inc. | Handling bad blocks generated during a block erase operation |

| CN115062352B (zh) * | 2022-08-16 | 2022-12-02 | 湖南进芯电子科技有限公司 | 加密区域动态调节的数据处理方法、系统及电路结构 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1114456A (zh) * | 1994-04-25 | 1996-01-03 | 松下电器产业株式会社 | 半导体存储器装置及其驱动装置 |

| US5576987A (en) * | 1992-01-17 | 1996-11-19 | Sharp Kabushiki Kaisha | Semiconductor memory device |

| CN1258078A (zh) * | 1998-12-10 | 2000-06-28 | 西门子公司 | 存储设备的分布式块冗余 |

Family Cites Families (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR960003526B1 (ko) * | 1992-10-02 | 1996-03-14 | 삼성전자주식회사 | 반도체 메모리장치 |

| US4571707A (en) * | 1984-02-23 | 1986-02-18 | Nec Corporation | Memory circuit with improved redundant structure |

| JPS6141192A (ja) * | 1984-07-31 | 1986-02-27 | 株式会社河合楽器製作所 | 楽音装置 |

| US4933898A (en) | 1989-01-12 | 1990-06-12 | General Instrument Corporation | Secure integrated circuit chip with conductive shield |

| US5127041A (en) * | 1990-06-01 | 1992-06-30 | Spectrum Information Technologies, Inc. | System and method for interfacing computers to diverse telephone networks |

| EP1227504B1 (en) | 1991-08-28 | 2004-08-04 | Oki Electric Industry Co., Ltd. | Semiconductor memory device |

| US5379415A (en) * | 1992-09-29 | 1995-01-03 | Zitel Corporation | Fault tolerant memory system |

| JP2885597B2 (ja) * | 1993-03-10 | 1999-04-26 | 株式会社東芝 | 半導体メモリ |

| US5363334A (en) | 1993-04-10 | 1994-11-08 | Microchip Technology Incorporated | Write protection security for memory device |

| US5661694A (en) | 1993-05-14 | 1997-08-26 | Fujitsu Limited | Programmable semiconductor memory device |

| US6026052A (en) | 1994-05-03 | 2000-02-15 | Fujitsu Limited | Programmable semiconductor memory device |

| JPH07235198A (ja) | 1994-02-18 | 1995-09-05 | Fujitsu Ltd | 半導体記憶装置 |

| JP3476952B2 (ja) * | 1994-03-15 | 2003-12-10 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| JPH07335509A (ja) | 1994-06-03 | 1995-12-22 | Hitachi Ltd | 半導体集積回路装置 |

| JP3263259B2 (ja) | 1994-10-04 | 2002-03-04 | 株式会社東芝 | 半導体記憶装置 |

| JPH10143434A (ja) | 1996-11-11 | 1998-05-29 | Toshiba Corp | 半導体集積回路 |

| KR19990061992A (ko) * | 1997-12-31 | 1999-07-26 | 김영환 | 디램의 컬럼 리던던시 선택장치 |

| JPH11232884A (ja) | 1998-02-09 | 1999-08-27 | Hitachi Ltd | 不揮発性メモリ装置 |

| US6223290B1 (en) * | 1998-05-07 | 2001-04-24 | Intel Corporation | Method and apparatus for preventing the fraudulent use of a cellular telephone |

| JPH11328990A (ja) | 1998-05-15 | 1999-11-30 | Hitachi Ltd | 半導体集積回路装置およびそれを用いたメモリカード |

| US20010014036A1 (en) * | 1998-12-21 | 2001-08-16 | Karl Rapp | Lock bit for an electrically erasable memory word |

| JP4463378B2 (ja) | 2000-05-02 | 2010-05-19 | 富士通マイクロエレクトロニクス株式会社 | 不揮発性半導体記憶装置 |

| JP4184586B2 (ja) * | 2000-09-28 | 2008-11-19 | 株式会社東芝 | 半導体記憶装置 |

| ITRM20030039A1 (it) * | 2003-01-30 | 2004-07-31 | Micron Technology Inc | Sblocco di registro di protezione per chip. |

| JP5196965B2 (ja) * | 2007-11-12 | 2013-05-15 | 株式会社東芝 | 不揮発性半導体記憶装置 |

-

2000

- 2000-09-28 JP JP2000297443A patent/JP4184586B2/ja not_active Expired - Lifetime

-

2001

- 2001-09-14 TW TW090122891A patent/TW543200B/zh not_active IP Right Cessation

- 2001-09-20 CN CN2007101802315A patent/CN101154461B/zh not_active Expired - Lifetime

- 2001-09-20 CN CN200710180232XA patent/CN101154465B/zh not_active Expired - Lifetime

- 2001-09-20 CN CNB2004100421793A patent/CN100431045C/zh not_active Expired - Lifetime

- 2001-09-20 KR KR10-2001-0058271A patent/KR100458411B1/ko active IP Right Grant

- 2001-09-20 CN CN2007101802300A patent/CN101154459B/zh not_active Expired - Lifetime

- 2001-09-20 CN CNB011372443A patent/CN1178228C/zh not_active Expired - Lifetime

- 2001-09-21 US US09/957,019 patent/US6600676B2/en not_active Expired - Lifetime

-

2003

- 2003-05-22 US US10/442,995 patent/US6937512B2/en not_active Expired - Lifetime

-

2005

- 2005-08-02 US US11/194,716 patent/US7106627B2/en not_active Expired - Lifetime

-

2006

- 2006-09-08 US US11/530,340 patent/US7295469B2/en not_active Expired - Lifetime

-

2007

- 2007-07-02 US US11/772,271 patent/US7613046B2/en not_active Expired - Lifetime

-

2009

- 2009-10-09 US US12/576,638 patent/US7894259B2/en not_active Expired - Fee Related

-

2011

- 2011-01-24 US US13/012,030 patent/US8189389B2/en not_active Expired - Lifetime

-

2012

- 2012-05-14 US US13/471,143 patent/US8885408B2/en not_active Expired - Fee Related

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5576987A (en) * | 1992-01-17 | 1996-11-19 | Sharp Kabushiki Kaisha | Semiconductor memory device |

| CN1114456A (zh) * | 1994-04-25 | 1996-01-03 | 松下电器产业株式会社 | 半导体存储器装置及其驱动装置 |

| CN1258078A (zh) * | 1998-12-10 | 2000-06-28 | 西门子公司 | 存储设备的分布式块冗余 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR100458411B1 (ko) | 2004-11-26 |

| JP2002109893A (ja) | 2002-04-12 |

| US6937512B2 (en) | 2005-08-30 |

| CN1178228C (zh) | 2004-12-01 |

| US7106627B2 (en) | 2006-09-12 |

| US20100027333A1 (en) | 2010-02-04 |

| US7295469B2 (en) | 2007-11-13 |

| US20030206438A1 (en) | 2003-11-06 |

| CN100431045C (zh) | 2008-11-05 |

| US20110116315A1 (en) | 2011-05-19 |

| US6600676B2 (en) | 2003-07-29 |

| US20070025149A1 (en) | 2007-02-01 |

| US8189389B2 (en) | 2012-05-29 |

| CN101154459A (zh) | 2008-04-02 |

| US20050265092A1 (en) | 2005-12-01 |

| US20120224422A1 (en) | 2012-09-06 |

| US7894259B2 (en) | 2011-02-22 |

| US20020036930A1 (en) | 2002-03-28 |

| US20070280017A1 (en) | 2007-12-06 |

| CN1540668A (zh) | 2004-10-27 |

| TW543200B (en) | 2003-07-21 |

| CN101154461A (zh) | 2008-04-02 |

| JP4184586B2 (ja) | 2008-11-19 |

| KR20020025711A (ko) | 2002-04-04 |

| CN1346130A (zh) | 2002-04-24 |

| US8885408B2 (en) | 2014-11-11 |

| CN101154465A (zh) | 2008-04-02 |

| CN101154465B (zh) | 2011-10-05 |

| CN101154459B (zh) | 2012-03-21 |

| US7613046B2 (en) | 2009-11-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN101154461B (zh) | 半导体存储装置 | |

| US7342825B2 (en) | Nonvolatile semiconductor memory having plural data storage portions for a bit line connected to memory cells | |

| CN100527278C (zh) | 页面缓存器和包括页面缓存器的多状态非易失性存储设备 | |

| KR100674545B1 (ko) | 반도체 기억 장치 및 반도체 기억 장치의 프로그램 방법 | |

| KR100458408B1 (ko) | 비휘발성 반도체 기억 장치 | |

| US20050185468A1 (en) | Non-volatile semiconductor memory device | |

| KR19980087197A (ko) | 불휘발성 반도체 메모리 장치 | |

| JP3786513B2 (ja) | 不揮発性半導体記憶装置 | |

| JP5075992B2 (ja) | 半導体記憶装置 | |

| KR101124126B1 (ko) | 불휘발성 메모리 소자의 프로그램 방법 | |

| JP4703624B2 (ja) | 半導体記憶装置 | |

| JP4105188B2 (ja) | 不揮発性半導体記憶装置およびそのデータ消去方法 | |

| CN110888519B (zh) | 一种存储器的编程方法和系统 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| TR01 | Transfer of patent right | ||

| TR01 | Transfer of patent right |

Effective date of registration: 20170728 Address after: Tokyo, Japan Patentee after: Toshiba Storage Corporation Address before: Tokyo, Japan, Japan Patentee before: Toshiba Corp |

|

| CX01 | Expiry of patent term | ||

| CX01 | Expiry of patent term |

Granted publication date: 20111019 |