CN101366182B - 输出nand接口的nand闪存控制器 - Google Patents

输出nand接口的nand闪存控制器 Download PDFInfo

- Publication number

- CN101366182B CN101366182B CN2006800356310A CN200680035631A CN101366182B CN 101366182 B CN101366182 B CN 101366182B CN 2006800356310 A CN2006800356310 A CN 2006800356310A CN 200680035631 A CN200680035631 A CN 200680035631A CN 101366182 B CN101366182 B CN 101366182B

- Authority

- CN

- China

- Prior art keywords

- controller

- flash memory

- memory device

- nand

- nand interface

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0483—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells having several storage transistors connected in series

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/08—Error detection or correction by redundancy in data representation, e.g. by using checking codes

- G06F11/10—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's

- G06F11/1008—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's in individual solid state devices

- G06F11/1072—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's in individual solid state devices in multilevel memories

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/08—Error detection or correction by redundancy in data representation, e.g. by using checking codes

- G06F11/10—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's

- G06F11/1008—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's in individual solid state devices

- G06F11/1048—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's in individual solid state devices using arrangements adapted for a specific error detection or correction feature

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/08—Error detection or correction by redundancy in data representation, e.g. by using checking codes

- G06F11/10—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's

- G06F11/1008—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's in individual solid state devices

- G06F11/1068—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's in individual solid state devices in sector programmable memories, e.g. flash disk

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1668—Details of memory controller

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

Abstract

本发明公开了一种制作在控制器管芯上的用于在主机设备和闪存设备(例如,NAND闪存设备)之间连接的NAND控制器(130)。在一些实施例中,当前公开的NAND控制器包括制作在控制器管芯上的电子电路,控制器管芯与闪存管芯是不同的,第一接口(例如主机类型接口,如NAND接口)(144,142)用于在电子电路和闪存设备之间连接,和第二接口(例如闪存类型接口)用于在控制器和主机设备之间连接,其中第二接口是NAND接口。根据一些实施例,第一接口是管芯间接口。根据一些实施例,第一接口是NAND接口。包括当前公开的NAND控制器的系统也被公开。组合上述系统和用于利用NAND控制器读写数据的方法也被公开。

Description

技术领域

本发明涉及一种NAND(与非)闪存控制器,其向主计算机输出与标准NAND(与非)闪存设备输出的接口相同类型的接口。

背景技术

单比特与多比特闪存单元

多年来,闪存设备已经成为众所周知的。通常,闪存设备中的每个闪存单元存储一比特的信息。通过支持存储器单元的两种状态是传统的在闪存单元中存储比特的方法。一种状态代表逻辑“0”,另外一种状态代表逻辑“1”。

在闪存单元中,所述两种状态通过具有位于单元通道(连接单元晶体管的源极和漏极元件之处)上的浮动门,以及表示在浮动门中存储的电荷数量的有效状态实现。通常,一种状态是在浮动门中有零电荷并且在单元被擦除后为未写入状态(通常定义为表示“1”的状态),另一种状态是在浮动门中含有一定数量的负电荷(通常定义为表示“0”的状态)。在门中具有负电荷使单元晶体管的临界电压(也就是为了能够使晶体管导电而加载于晶体管控制门的电压)增高。可以通过检查单元的临界电压读取到所存储的比特。如果临界电压处于较高状态,则比特值为0,如果临界电压位于较低状态则比特值为1。实际上没有必要精确地读取单元的临界电压。所需要的就是正确地识别单元当前正处于两种状态中的哪一种。为了这个目的,必须将本单元的临界电压与一个处于两种状态之间的参考电压相比较,从而判断本单元的临界电压是否低于或高于参考值。

图1A(现有技术)图示了工作原理。特别地,图1A示出了大量单元的临界电压的分布情况。因为闪存设备中的单元在其特性以及性能上并不是完全相同(例如,由于杂质的浓度的不同,或者硅结构的缺陷),对所有的单元应用同样的编程操作不会使所有的单元具有完全相同的临界电压。作为替代的是,临界电压的分布如图1A所示。存储值为“1”的单元通常具有负的临界电压,使得大多数单元的临界电压接近图1A的左波峰(标注为1)的中心电压,而少数 单元的临界电压高于或低于左波峰的中心电压。类似地,存储值为“0”的单元通常具有正的临界电压,使得大多数单元的临界电压接近图1A的右波峰(标注为0)的中心电压,而少数单元的临界电压高于或低于右波峰的中心电压。

近年来,市场上出现了一种使用“多级单元”(MLC)的新的闪存设备。术语“多级单元”容易被误解,因为如上文所述,每单元单比特的闪存使用多级,也就是两级。因此,术语“单比特单元”(SBC)在下文中用于指两级存储单元,而术语“多比特单元”(MBC)在下文中用于指多于两级的、也就是每单元多于一个比特的存储单元。现在最普通的MBC闪存是每单元两个比特的,因此以下的举例使用这样的MBC存储器。然而,应当理解的是本发明同样适用于支持每单元超过两个比特的闪存设备。单个的存储两比特信息的MBC单元处于四种不同状态中的一种状态。因为单元的状态由单元的临界电压表示,MBC单元支持用于单元的临界电压的四种不同的有效范围。图1B(现有技术)显示了典型的每单元两比特的MBC单元的临界电压的分布。正如所预料的,图1B有四个波峰,每个波峰对应于一个状态。至于SBC,每个状态实际上是一个电压的范围而不是一个单独的电压。当读取单元内容时,单元的临界电压必须在明确的电压范围内被正确地识别。MBC闪存设备的现有技术的实例参见Harari的专利号为US5434825的美国专利申请,包括其全部内容作为参考,其实际上如同在这里完全被阐述。

设计用于MBC操作的、例如处于四种状态的单元通常可如两种状态的SBC单元操作。例如,其实际上如同在这里完全被阐述的,引用的Conley等人在申请号为6,426,893的美国专利作为参考,其公开了在同样设备中使用MBC与SBC模式,并且选择设备的某一部分在MBC模式下进行最高密度的操作,而其他部分在SBC模式下使用以提供更好的性能。

MBC设备提供重要的成本优势。一个每单元两比特的MBC设备只需要一个类似容量的SBC设备的硅晶片一半的空间。然而,使用MBC闪存存在缺点。MBC存储器的平均读写时间长于SBC存储器,导致了比较差的性能。并且,MBC的可靠性也低于SBC。MBC的临界电压范围之间的差别比SBC要小很多。从而,临界电压的干扰(例如,所存储的电荷的泄露导致临界电压的偏移或者来自操作相邻单元的干扰)在SBC中是可以忽略的,因为两种状态的区别非常大,但却可以导致一个MBC单元从一种状态转移至另一种状态,将导致 错误的比特。最终的结果是,从数据保持时间或者设备的擦、写循环的耐久性的方面来说,MBC单元的性能规格比较差。

NAND(与非)闪存设备

闪存设备通常分为NOR(或非)设备和NAND(与非)设备,名字来源于单独的存储单元在单元序列中的互联方式。NOR设备是随机访问的-访问NOR闪存设备的主计算机可以提供给该设备在它的地址指针上的任意地址,并且立即取回存储于设备数据指针上的那个地址中的数据。这与SRAM或者EPROM存储器的操作很相似。另一方面,NAND设备并非随机访问的而是顺序访问的。它不可能以上述用于NOR的方式去访问任何随机地址-而是主机必须写入字节序列到设备中,其定义了所要求的指令的类型(如,读,写,擦除,等等)和用于那个指令的地址。地址识别页面(单个操作中可以写入的闪存设备的最小的块)或者块(单个操作中可以擦除的闪存设备的最小的块),而并非单独的字节或单词。读和写指令序列的确含有单个字节或者单词的地址,但是事实上NAND闪存经常从存储单元中读出完整的页面或者把完整的页面写入到存储单元中。当页面的数据从队列中被读出并放入至设备内的缓冲区之后,主机可以通过使用选通信号连续地时钟输出它们一个接一个地访问数据字节或单词。

由于NAND设备的非随机访问,其不能被用于直接从闪存中运行代码。这与支持直接代码执行(通常称为“在适当的位置执行(eXecution in place)”或者“XIP”)的NOR设备相反。因此NOR设备是通常用于代码存储的。然而,NAND设备的优势使其作为数据存储非常有用。NAND设备比同样比特容量的NOR设备便宜,或者说-在同样的成本下NAND设备比NOR设备提供更多的存储的比特。而且,NAND设备的写入和擦除的性能比NOR设备快许多。这些优点使得NAND闪存技术成为用于存储数据的技术选择。

NAND接口协议

典型的SBC NAND设备是提供2G比特存储的东芝(Toshiba)TC58NVG1S3B。典型的MBC NAND设备是提供4G比特存储的东芝(Toshiba)TC58NVG2D4B。引用两种设备的数据单作为参考,其实际上如同在这里完全被阐述。

正如可以从前面提到的数据单中看出的,那两种NAND设备有着类似的接 口。这些NAND设备利用同样的电信号进行NAND闪存设备和主设备之间的命令谐调和数据传输。那些信号包括数据线和一些控制信号——ALE(允许地址锁存),CLE(允许命令锁存),WE\(允许写入)等等。SBC设备和MBC设备在它们的性能上并不是完全相同的——用于写MBC页所需要的时间远远多于用于写SBC页的时间。然而,两种设备使用的电信号和它们的功能是相同的。现有技术中这种接口协议的类型是“NAND接口”。尽管到目前为止,标准化组织还没有对“NAND接口协议”制定正式地标准化,但NAND闪存设备的生产商们都遵循同样的协议以支持NAND闪存功能的基本子集。这样做就使用户在将NAND设备应用到他们的电子产品时可以使用任何生厂商的NAND设备,而不用因为使用个别厂家的设备修改他们的硬件或软件。需要注意的是,即使NAND厂商提供超出此功能基本子集的额外功能,为了与其他厂商使用的协议相兼容也要确保提供了基本功能,至少是某种程度上。

本申请中的术语“NAND接口协议”(或者是简写“NAND接口”)是指发起设备和相应设备之间的接口协议,即使它不与定时参数完全兼容,不与NAND设备支持的其他命令完全兼容,或者包括NAND设备不支持的额外命令,但它一般都遵循主机设备和NAND闪存设备之间的基本读、写和擦除操作的协议。换句话说,术语“NAND接口”是指任何接口协议,其所使用的传输字节序列与当接口连接于东芝(Toshiba)TC58NVG1S3B NAND设备时用于读(操作码00H)、写(操作码80H)和擦除(操作码60H)的字节序列功能相同,并且也使用与上述NAND设备的CLE、ALE、CE、WE和RE信号功能相同的控制信号。

需要注意的是,“NAND接口协议”不是相对称的。因此,经常是由主机设备发起于NAND接口上的交互,而不是由闪存设备。

如果给定设备包括用于支持NAND接口协议(例如,利用NAND接口协议与其他设备交互)所需的元件(例如,硬件,软件,固件或者它们的任何形式的结合),那么给定设备(例如,控制器,闪存设备,主机设备,等等)被称为包含,包括或者具有一个“NAND接口”。

一个给定设备(如,控制器设备)的接口(例如,NAND接口或者与其他协议相关联的接口)可以是个“主机端接口”(如给定设备适于利用主机端接口与主机设备进行交互)或者给定设备的接口可以是“闪存设备端接口”(如,给 定设备适于利用闪存设备端接口与闪存设备进行交互)。术语“闪存设备端接口”、“闪设备端接口”和“闪端接口”在此互相交换地使用。

这些术语(即“主机端接口”和“闪存设备端接口”)不能与术语“主机类型接口”和“闪存类型接口”相混淆,在这里使用该术语以区分NAND接口协议的两侧,因为这个协议不是对称性的。此外,由于经常是主机发起交互,我们需要注意,如果一个给定设备包括用于实现NAND接口协议的主机端(即,用于标识一个NAND主机,和发起NAND协议交互)的必要的硬件和/或者软件,则该设备被称为具有“主机类型接口”。类似地,由于闪存设备从来不会发起交互,我们需要注意,如果一个给定设备包括用于实现NAND接口协议的闪存端(即用于表示NAND闪存设备)的必要的硬件和/或者软件,则该设备被称为具有“闪存类型接口”。

通常,“主机类型接口”(即那些扮演主机角色的)是“闪存设备端接口”(即他们与闪存设备或者效仿闪存设备的硬件进行交互)而“闪存类型接口”(即那些扮演闪存设备角色的)通常是“主机端接口”(即他们与主机设备或者效仿主机设备的硬件进行交互)。在这种应用中的术语“主机设备”(或者简写为“主机”)是指任何具有处理能力并且有与闪存设备进行接口的能力的设备。主机设备可以是个人电脑、PDA、移动电话、游戏控制台等等。

通常,NAND设备相对较难接口和用其来工作。一个原因是如上述的用于访问它们的相对复杂的协议(与NOR设备相比较而言)。另一个难题是当从NAND设备读取的数据存在误差。相反,NOR设备可以被假设总是返回正确的数据。NAND设备与生俱来的不可靠性需要利用误差侦查码(EDC)和误差纠正码(ECC)。

SBC NAND闪存的制造商通常建议用户应用误差纠正码,其能够纠正每个含有512字节数据的页面中1比特误差。但是MBC NAND闪存设备数据单通常建议应用能够修正每个含有512字节数据的页面中的4个比特误差的ECC。对于一个大小是2048字节的页面,如同在上述NSND设备中提及的(即的“大区块设备”),建议是在页面的512字节的每个区域中应用误差纠正。在此应用中,术语“N-比特ECC”指能够在512字节数据中修正N比特误差的ECC方案,而不考虑512字节是一页的大小、少于一页、还是多于一页。

NAND控制器

由于NAND设备的复杂性,通常会使用“NAND控制器”用于控制电子系统中的NAND设备的使用。确实可以通过没有插入NAND控制器的主机设备直接操作和利用NAND设备,而且存在如此操作的系统。但是,这种结构存在很多弊病。第一,主机必须单独地操作NAND设备的每个控制信号(例如,CLE或者ALE),这对于主机来说繁琐并且耗时。第二,支持EDC和ECC给主机带来沉重的负担-主机必须为每个页面的写操作计算奇偶比特,并且执行误差检测计算(以及一些误差纠正计算)。所有的这些使得这样的“无控制器”架构相对缓慢和低效。

使用NAND控制器显著地简化当利用NAND设备时主机的任务。处理器与控制器通过更方便使用的协议进行交互——写入页面的请求可以作为单个跟随着地址和数据的命令代码发出,而无需去为复杂的控制行序列和NAND命令码烦恼。控制器然后将主机控制协议转换为等价的NAND协议序列,当主机无需去做其他的任务的时候(或者就是等待着NAND操作结束,如果是这样要求的)。

现有技术中有些观点是关于NAND控制器在系统中所处何处。第一种方法如图2所示。图中NAND控制器114物理上被置于主机设备110A的主机处理器112A中。如果主机处理器112A是通过单管芯实现的,则控制器114被集成于同一管芯上。例如在一些由德克萨斯(Texas)工厂生产和销售的OMAP处理器的情形中。利用这种结构的制造系统,主机处理器与NAND控制器通常使用一些私有协议进行交互。因为交互位于主机处理器中,使用标准协议没有益处。

第二种现有技术方法如图3A-3B中所示。图中NAND控制器116是个分离的物理元件,处于主机110B的主机处理器112B和NAND设备120A之间。例如一些便携USB闪存设备(UFDs)中的情形,例如DiskOnKey制造的并由M-Systems闪存磁碟先锋销售的产品,其中有NAND控制器116被封装于UFD中,并且使用设备端NAND接口124与在一端的NAND设备120A进行交互并且与在另一端的主机处理器112B进行交互(使用利用USB协议主机端的USB接口122)。在使用这种结构的系统中,主机处理器通常使用标准协议例如USB或ATA与NAND控制器进行交互,由于交互是位于处理器外的,使用为其他目的由处理器支持的标准协议就非常方便。

需要注意的是,根据之前定义的术语,NAND接口124是一个“闪存设备端NAND接口”(即适用于与NAND闪存设备120A交互)但是同时,NAND接口124也是主机类型NAND接口(即适用于发起NAND协议交互)。

第三个现有技术方法如图4所示。图中NAND控制器118物理上置于NAND设备120B中。闪存设备和控制器甚至可以被封装于同一管芯上。例如在一些由MDOC存储设备制造厂生产由M-system闪存磁碟先锋销售的以及在由三星电子销售及生产的OneNAND设备的情形中。在使用这种结构架构的系统中,主机处理器112B通常与NAND控制器使用像USB的标准协议或者使用像上述MOC和OneNAND例子情形中的半标准协议进行交互。

我们可以从以上推论出现有技术中独立的NAND控制器(既不与NAND设备集成也不与主机处理器集成)通常在它的主机端具有一些标准的接口,在其闪存设备端具有NAND接口(例如,参见图3B)。实际上,在市场上可以找到输出多种接口类型-USB,SD(安全数码),MMC(多媒体卡)以及更多的NAND控制器。但是目前还找不到向主机输出NAND接口的独立的NAND控制器。实际上,有理由期望——没有内建NAND支持并且为此目的需要外部控制器的主机处理器,通常不具有NAND接口并且不能直接与输出NAND接口的设备相连,因此,控制器具有主机端NAND接口没有用处。另一方面,具有内建NAND支持的主机处理器通常还包括内建的NAND控制器,并且可以与NAND设备直接相连,因此不需要一个外部NAND控制器。

以上描述的现有技术遗留了一个未解决的问题。如图2所示,假设存在集成内建NAND控制器和NAND接口的主机处理器。该内建的控制器被设计与在某种可靠级别上的NAND设备一起工作。这是因为NAND控制器提供一定级别的误差检测和纠正,因此不能支持低可靠性的NAND设备。例如,具有一个比特ECC的NAND控制器可以与其生产厂家指定的仅要求该误差纠正级别的SBC NAND设备一起工作。这种控制器不能与每单元两个比特的MBCNAND设备一起工作,因为它们需要4个比特ECC,因此一些数据可能不会被正确地读入处理器中。同样,提供4比特ECC的NAND控制器可以与当前的每单元两比特的MBC NAND一起工作,但是不能与很可能要求更高级别ECC容量的下一代MBC NAND设备一起工作。

这是因为未来的MBC NAND设备被期望具有比当前的MBC设备更低的 可靠性和更强的ECC容量。减少可靠性和增加误差率的原因有两部分:

a.制造NAND设备的流程的持续的改进以生产更小型的存储单元。几年前NAND设备使用0.4微米流程,当前它们使用90纳米和70纳米技术,并且这种缩小的趋势可期望还在继续。随着存储单元尺寸的缩小带来的是低可靠性,因为小尺寸使得单元对在以前是不重要的物理作用和现象更加敏感。

b.当每个单元有多于两个比特每单元的MBC单元成为在商业上可用时,其肯定比SBC单元和每单元两比特MBC单元具有更低的可靠性。大量的状态必须由阈值电压区代表,这意味着状态之间的余量更小,即使更小的干扰和偏移导致数据读取的错误。当对ECC的要求从1比特ECC增长至4比特ECC时,在对SLC和每单元两比特MBC的比较中这种影响已经被证明。

现在回到带有内建NAND控制器114的主机处理器112A,假定控制器114只支持1比特ECC。那么这个处理器也许不能够使用MBC NAND,即使由于MBC NAND的低价格这是非常值得的。假如MBC NAND被连接到处理器内建的控制器的NAND接口,这可能是唯一连接到处理器的方法,那么MBCNAND给内建控制器有限容量的ECC产生了太多的误差以至于不能修正。

类似地,假如内建控制器支持4比特ECC,其可以利用SLC和每单元两比特MBC NAND。但是当在市场上出现有着低可靠性的NAND设备时,处理器不能从它们的低价格中受益,因为内建控制器不能够提供所要求的误差修正级别。

因此我们可以了解,每当使用包括设计成支持上一代NAND设备的内建NAND控制器的主机处理器的时候,现有技术的状态不能够为从新NAND设备的成本优势中受益的问题提供一个很好的解决方案。

对提供具有机械NAND控制器的主机设备和连续几代NAND闪存设备之间的兼容性的设备和方法有一个持续的需求。

发明内容

可以通过本发明的几个方面来满足前述的需求。

现在第一次公开用于连接主机设备和制作在闪存管芯上的闪存设备(例如,NAND闪存设备)的控制器。当前公开的控制器包括(a)制作在控制器管芯上的电子电路,控制器的管芯与闪存管芯不同,(b)用于在电子电路和闪存设备之间连接(例如,NAND闪存设备)第一接口(例如主机类型接口),和(c)用于在控制器和主机设备之间连接第二接口(例如闪存类型接口),其中第二接口是NAND接口。。

根据一些实施例,第一接口是管芯之间接口,

根据一些实施例,第一接口是NAND接口,

根据一些实施例,当前公开的控制器还包括(d)用于提供从第一和第二接口中的一个接收的数据的误差修证的误差修正模块。

根据一些实施例,本发明公开的控制器还包括(d)至少一个附加的用于与主机设备交互的主机端接口。

现在第一次公开一种数据存储系统,包括(a)制造在闪存管芯上的闪存设备,以及(b)当前公开的NAND控制器,其中控制器通过第一接口可以有效地与闪存设备通信。

根据一些实施例,当前公开的系统还包括(c)共同的封装,其中闪存设备和控制器都在这个共同的封装中提供。

根据一些实施例,当前公开的系统还包括(c)分开的各自的封装,其中每个闪存设备和控制器都在各自的封装中提供。

根据一些实施例,当前公开的系统还包括(c)印刷电路板,其上安装闪存设备和控制器,其中闪存管芯直接把安装在印刷电路板上而不需要封装。

根据一些实施例,当前公开的系统可以还包括(c)印刷电路板,其上安装有闪存设备和控制器,其中控制器管芯直接安装在印刷电路板上而不需要封装。

现在第一次公开一种数据存储系统,包括(a)主机设备,(b)制作在闪存管芯上的闪存设备,以及(c)当前公开的NAND控制器可以通过第一接口有效地与闪存设备通信,并通过第二接口与主机设备通信。

现在公开一种从主机设备写入数据的方法,包括以下步骤:

(a)提供制作在闪存管芯上的闪存设备和制作在控制器管芯上的控制器,闪存管芯不同控制器管芯,(b)根据NAND接口协议从主机设备向控制器发布写命令,以及(c)根据NAND接口协议从控制器向闪存设备发布写命令。

根据一些实施例,当前公开的方法还包括(d)通过控制器进行奇偶比特计算的步骤。

现在公开一种向主机设备读出数据的方法,包括以下步骤:

(a)提供制作在闪存管芯上的闪存设备和制作在控制器管芯上的控制器,闪存管芯不同于控制器管芯,(b)根据NAND接口协议从主机设备向控制器发布读命令,并且(c)根据NAND接口协议从控制器向闪存设备发送读命令。

根据一些实施例,当前公开的方法还包括以下步骤(d)把数据从闪存设备中取回到控制器,(e)把与所取回的数据相关的奇偶比特从闪存设备中取回到控制器,(f)根据所取回的奇偶比特修正所取回的数据,从而生成修正过的数据,以及(g)把修正过的数据从控制器中取回到主机设备。

现在第一次公开一种创建数据存储系统的方法,其包括以下步骤(a)提供制作在闪存管芯上的闪存设备,(b)提供当前公开的NAND控制器,以及(c)在闪存设备中配置闪存控制器使得闪存控制器通过第一接口能有效地与闪存设备进行通信。

根据一些实施例,当前公开的方法还包括以下步骤(d)在单个封装中封装闪存控制器和闪存设备。

根据一些实施例,闪存设备和闪存控制器位于分开的各自的封装中,并且这种配置包括彼此连接各自的封装。

根据一些实施例,当前公开的方法还包括以下步骤(d)安装闪存设备和控制器到印刷电路板上,其中安装包括直接将闪存设备管芯安装到印刷电路板上而不经过封装。

根据一些实施例,当前公开的方法还包括以下步骤(d)安装闪存设备和控制器到印刷电路板上,其中安装包括直接将控制器管芯冲压到印刷电路板上而不经过封装。

根据一些实施例,当前公开的方法还包括以下步骤(d)将数据存储系统配置到主机设备上使得闪存控制器通过第二接口能有效地与主机设备进行通信。

从下面的详细描述以及例子中,这些和其它的实施例将更加明显。

附图说明

图1A-1B提供大量存储单元的阈值电压的分布的图示说明(现有技术)。

图2提供了包含主机设备和NAND闪存设备的现有技术的系统的框图。

图3A提供了包含主机设备、NAND控制器和NAND闪存设备的现有技术的系统的框图。

图3B提供了包含具有主机端USB接口和闪存设备端NAND接口的现有技术的NAND控制器的框图。

图4提供了包含主机设备和NAND闪存设备的现有技术的系统的框图。

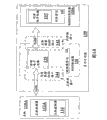

图5A提供了根据本发明的示例性实施例的包含在主机端的NAND接口和在闪存设备端的NAND接口的NAND控制器的框图。

图5B提供了根据本发明示例性实施例的,包括主机设备、图5A的NAND控制器以及NAND闪存设备的系统的框图。

图6A描述了图5B中描述的示例性系统的示例性管芯配置。

图6B描述了图5B中描述的示例性系统的示例性配置,其中NAND控制器和NAND闪存设备位于一个单独的多芯片封装中。

图6C描述了图5B中描述的示例性系统的示例性配置,其中NAND控制器和NAND闪存设备处于分开的各自的封装中。

图7示出了描述其中主机通过扩展NAND控制器将数据写入NAND存储设备的方法的流程图。

图8示出了描述其中主机通过扩展NAND控制器将数据从NAND存储设备读出的方法的流程图。

具体实施方式

现在,本发明以特别的示例性实施例的方式进行描述。可以理解的是本发明不限于这里公开的示例性实施例。也可以理解的是,并不是如任何特别的一条附加的权利要求中要求的控制器、包括控制器的系统以及所描述的读取的方法和所描述的数据的每一个特征都是对于实现本发明必要的。描述设备的各种各样的元素和特征,以使发明完整。也可以理解的是贯穿整个公开,每当流程或方法被示出或被描述时,可以任何次序或者同步的方式来执行方法的步骤,除非根据上下文很清楚地得知一个步骤依赖于其他先执行的步骤。

本发明第一次公开了一种新型的NAND控制器,其特征在于输出给主机端的接口是NAND接口。在一些实施例中,本发明公开的控制器在闪存设备两端都有NAND接口,其中控制器相对NAND设备扮演着主机的角色,而在主机设备端,其中控制器相对主机扮演NAND设备的角色。

为了本公开的目的,“NAND闪存设备”被定义为电子电路,包括多个NAND闪存单元以及用于在NAND闪存单元中存储数据的任何的必要的控制电路(例如:提供闪存类型接口的电路),其用于在闪存单元中存储数据。需要注意“NAND闪存设备”不是必须有其自己专有的处所,其可以与其他“设备”例如控制器安置在一起。在一些实例中,“NAND闪存设备”直接安装在印刷电路板上而不经过任何的封装。

此外,在一些实施例中,控制器包括误差修正的能力,其可以充分修正NAND设备低可靠性的许多错误。由于这些误差可以由控制器修正,控制器可以向主机呈示完全没有误差的闪存设备,或者有极少数量的误差-少到足以由主机的内置的NAND控制器的误差修正能力来处理。

注意图5A,其提供了根据本发明的一些实施例的控制器的示意性的框图。控制器130包括用于连接到NAND闪存设备的闪存设备端NAND接口142,。此外,需要注意闪存设备端NAND接口142也是主机类型NAND接口(即,适合于在NAND接口上发起交互行为,并且向NAND闪存设备呈现一个主机设备)。

控制器130还包括用于连接到支持NAND接口协议的主机设备的主机端的NAND接口144。这个主机端的NAND接口也是闪存类型的NAND接口(例如,控制器130适用于为主机呈现一个NAND闪存存储设备)。控制器可以选择性地包括一个或多个附加的主机端接口146,用于利用非NAND接口连接控制器到主机,例如USB或者MMC接口。

如图5A所示,控制器还包括ECC模块132,用于检测和纠正通过设备端接口142从NAND设备取回的数据中的所有或者一些误差。ECC模块132可以包括硬件、软件、固件或者它们的组合。在NAND控制器130向主机输出无误差NAND设备的情况下,ECC模块132可以纠正所有的误差。可选择地,ECC模块132可以只修正通过闪存设备端NAND接口142从NAND设备取回的数据中发现的一些误差。

在一个例子中,NAND设备可以具有需要4比特ECC的可靠性,并且ECC模块142纠正了足够多的误差以把数据的可靠性提高到一个使得主机的内建NAND控制器中的1比特ECC模块可以处理该数据的级别。

需要注意NAND控制器130还可以选择性地包括用于提供其他功能的一个或多个模块134(例如包括硬件、软件、固件或者它们的组合),如加密功能或者地址映射,其把从主机取回的逻辑闪存地址映射到发送到闪存设备的物理闪存地址。

注意图5B,其示出了图5A中描述的包括外部NAND控制器130(例如从主机设备分离出来的控制器)的示例性系统的示意性框图。通过设备端的NAND接口142,外部NAND控制器130与NAND闪存设备120A连接。通过主机端NAND接口144,NAND控制器130与主机设备110A连接。

需要注意的是,外部控制器130接口通过两个NAND接口142和144的连接是不同的。NAND接口协议是不对称的——存在发起方,其发起交互(根据之前定义术语的“主机类”),和响应方,其只响应发起信号(根据之前定义术语的“闪存类”)。

利用设备端的NAND接口142,外部NAND控制器130担当NAND接口协议的主机类部分,并且NAND设备130担当NAND接口协议的闪存类部分。利用主机端接口144,外部控制器130担当NAND接口协议的闪存类的部分,并且主机110A担当NAND接口协议中的主机类部分。

注意图6A,其示出了图5A中描述的示例性系统的管芯的示例性配置。这样,需要注意的是,NAND控制器130包括制作在控制器管芯131上的电子电路135,而NAND闪存设备120A包括制作在闪存管芯133上的电子电路137,控制器管芯131和闪存管芯133是截然不同的管芯。

需要注意的是,如图5A中描述的在NAND控制器130中的元件(即ECC模块132、闪存类NAND接口144、主机类NAND接口)至少一部分是由位于控制器管芯上的控制器电子电路135实现的。

位于控制器电子电路135和闪存电路137之间的接口142是“管芯内”接口。如在此处用到的,“管芯间接口”(例如管芯间NAND接口)能够有效地与两个处于不同管芯上的电子电路的不同的单元之间连接(如,为电子电路的不同的单元提供必要的物理以及逻辑构造以例如利用一个或多个特殊的协议进行互相通信)。这样,管芯间接口包括必要的物理元件(衰减器,输出输入驱动器等等),用于在处于分开的管芯上的电子电路的两个不同单元之间连接。

根据一些实施例,管芯间接口可以在制作在两个不同的以共同封装包封装中的管芯上的电子电路间连接。这个例子在图6B中说明,其中NAND控制器130和NAND闪存设备120A都位于共同的多芯片封装包139中。

可选地,管芯间接口可以在制作在以不同的封装包封装的两个不同的管芯的电子电路之间连接(例如,每个管芯都封装在其自己的封装包中)。这个例子在图6C说明,其中NAND控制器130和NAND闪存设备120A位于分开的各自的封装包中。特别地,NAND控制器130处于控制器封装包141中,而NAND闪存设备120A处于闪存封装包143中。这样,如图6C中所说明的,接口142是“封装包间接口”。

需要注意的是,处于共同封装包中的管芯(例如,如图6A中所示)以及处于分开的封装包中的管芯(例如,如图6B中所示)并非唯一可能的配置。

这样,可选地,在一些实例中,管芯间接口可以在制作在两个不同管芯上的电子电路之间连接,其中一个或者两个都根本没有封装。例如,在许多应用中,由于需要保存空间,主板上提供了(如安装,例如直接安装)完全未经封装的存储管芯。这样在一个例子中,需要注意是,在新一代电话的存储卡上,存储管芯经常完全未经封装就安装在主板上。如此处所用的,“直接安装”到印刷电路板上的管芯是事先未经封装就安装到印刷电路板上的。

图7示出了描述主机110A(例如在设备中包括NAND控制器114的主机)通过外部NAND控制器130向NAND存储设备120A写数据(例如一页数据)的方法的流程图。如图7所示,主机110A发布写命令410给外部控制器130(例如利用NAND接口协议发布的写命令,包括命令字节、地址字节和数据字节)。主机110A不必得知发布命令给控制器130的事实,并可以假定主机正与它有能力处理的标准NAND闪存存储设备的类型连接。

NAND控制器130接收到主机发布的写命令(例如通过主机端NAND接口144)。在接收到了写命令之后,控制器计算与数据字节相对应的ECC奇偶比特420(例如利用ECC模块132),并且发布写命令430给NAND设备(例如,通过闪存设备一侧接口142)。再一次,根据NAND接口协议发布命令,包括含有主机数据字节和相应的ECC奇偶比特的命令字节、地址字节和数据字节。NAND闪存设备不必得知其间接通过NAND控制器130而不是直接从主机设备110A中接收命令。在步骤440,NAND闪存设备120A存储接收到的数据字节的非易失性存储单元,这样实现了主机110A的请求。

图8示出描述其中主机110A(例如在设备中包括NAND控制器114的主机)通过外部NAND控制器130从NAND存储设备120A中读数据(例如数据 页)的方法的流程图。这样主机110A发布读命令410到外部控制器130(例如利用NAND接口协议发布的读命令,包括命令字节和地址字节)。如同上面的写命令一样,主机110A不必得知它发布命令给外部控制器130的事实,并可以假定主机正与它有能力处理的标准NAND设备类型连接。

外部NAND控制器130接收主机发布的读命令(例如通过主机端的NAND接口144)。在接收了读命令之后,外部控制器130发布读命令520(例如,通过设备端NAND接口142)给NAND设备120A。还是根据NAND接口协议发布命令,包括命令字节和地址字节。在步骤530,NAND闪存设备120A从非易失性单元序列中取回所请求的数据,其中当存储数据时,主机数据伴随着计算出来的ECC奇偶比特。在步骤540,将数据字节以及伴随的奇偶比特发送给外部NAND控制器。该发送根据NAND接口协议通过一系列由控制器生成的一系列该选通脉冲完成,每个依次读入控制器一个字节或者一个字(依据使用的NAND接口是8比特宽度还是16比特宽度)。在步骤550,外部NAND控制器130利用奇偶比特纠正数据字节中的误差(例如通过ECC模块132)。在步骤560,所修正的数据字节通过主机端的NAND接口144被发送给主机。发送还是根据NAND接口协议通过一系列由主机生成的读选通脉冲完成。主机110A现在具有了原来在闪存中存储的相同的数据字节。

现在可以看到,当利用集成设计为支持上一代NAND设备的内建NAND控制器的主机处理器时,本发明允许从新的NAND设备的低成本优势中受益。

在本申请的说明书和权利要求中,每个动词“包含”“包括”和“具有”以及其结合被用来表明动词的对象或者对象们并不必是成员、组件、元件或动词的主题或者主题们的部分的完整列表。

本发明通过实施例的详细描述来说明,其作为示例而不是去限制发明的范围。描述的实施例包括不同的特征,但不要求它们在发明的所有实施例中都要出现。本发明中的一些实施例只利用一些特征或特征的可能的组合。已经描述了本发明的实施例的变化,本领域技术人员可以想到,包括在描述的实施例中提及特征的不同组合的本发明的实施例。

Claims (49)

1.一种用于在主机设备和制作在闪存管芯上的闪存设备之间接口连接的控制器,该控制器包括:

a)制作在控制器管芯上的电子电路,所述控制器管芯与闪存管芯不同;

b)用于在所述电子电路和所述闪存设备之间接口连接的第一接口;

c)用于在控制器和主机设备之间接口连接的第二接口,其中所述的第二接口是NAND接口;

d)误差修正模块,用于为通过所述第一接口和第二接口中的一个接收的数据提供误差修正;以及

e)将从主机设备接收的逻辑闪存地址映射到发送给闪存设备的物理地址的模块。

2.如权利要求1所述的控制器,其中所述的第一接口是NAND接口。

3.如权利要求1所述的控制器,还包括:

f)至少一个附加的主机端接口,用于与主机设备接口连接。

4.一种数据存储系统,包括:

a)制作在闪存管芯上的闪存设备;和

b)如权利要求1所述的控制器,所述控制器操作用于通过所述第一接口与所述闪存设备通信。

5.如权利要求4所述的系统,还包括:

c)共同的封装,其中所述闪存设备和所述控制器都在所述共同的封装中提供。

6.如权利要求4所述的系统,还包括:

c)分开的各自的封装,

其中所述闪存设备和所述控制器每个都在各自所述的封装中提供。

7.如权利要求4所述的系统,还包括:

c)印刷电路板,其上安装所述闪存设备和所述控制器,其中所述闪存管芯直接安装在所述印刷电路板上。

8.如权利要求4所述的系统,还包括:

c)印刷电路板,其上安装所述闪存设备和所述控制器,其中所述控制器管芯直接安装在所述印刷电路板上。

9.一种数据存储系统,包括:

a)主机设备;

b)制作在闪存管芯上的闪存设备;以及

c)权利要求1中所述的控制器,其操作用于通过所述第一接口与所述闪存设备通信,以及通过所述第二接口与所述主机设备通信。

10.一种创建数据存储系统的方法,该方法包括:

a)提供制作在闪存管芯上的闪存设备;

b)提供如权利要求1所述的控制器;

c)对所述闪存设备配置所述控制器,使得所述控制器操作用于通过所述第一接口与所述的闪存设备通信。

11.如权利要求10所述的方法,还包括:

d)在单个封装里封装所述控制器和所述闪存设备。

12.如权利要求10所述的方法,其中所述闪存设备和所述控制器位于分开的各自的封装中,并且所述配置包括使各自的封装彼此连接。

13.如权利要求10所述的方法,还包括:

d)将所述闪存设备和所述控制器安装到印刷电路板上,其中所述安装包括将所述闪存管芯直接安装到所述印刷电路板上。

14.如权利要求10所述的方法,还包括:

d)安装所述闪存设备和所述控制器到印刷电路板上,其中所述的安装包括直接将所述控制器管芯安装到所述印刷电路板上。

15.如权利要求10所述的方法,还包括:

d)将数据存储系统配置到主机设备上使得所述控制器操作用于通过所述第二接口与所述主机设备通信。

16.一种从主机设备中写数据的方法,该方法包括:

a)提供制作在闪存管芯上的闪存设备和制作在控制器管芯上的控制器,所述闪存管芯不同于所述控制器管芯;

b)根据NAND接口协议从所述主机设备向所述控制器发布写命令;

c)根据NAND接口协议从所述控制器向所述闪存设备发布写命令;

d)由控制器进行奇偶比特计算;以及

e)将从主机设备接收的逻辑闪存地址映射到发送给闪存设备的物理闪存地址。

17.一种读数据到主机设备的方法,该方法包括:

a)提供制作在闪存管芯上的闪存设备和制作在控制器管芯上的控制器,所述闪存管芯不同于所述控制器管芯;

b)根据NAND接口协议,从主机设备向控制器发布读命令;

c)根据NAND接口协议,从控制器向闪存设备发布读命令;

d)从所述闪存设备中把数据取回到所述控制器;

e)把与从所述闪存设备中取回的数据相关的奇偶比特取回到所述控制器;

f)根据所述所取回的奇偶比特修正所述所取回的数据,从而生成修正过的数据;

g)从所述控制器中把所述修正过的数据取回到所述主机设备;以及

h)将从主机设备接收的逻辑闪存地址映射到发送给闪存设备的物理闪存地址。

18.一种用于在主机和闪存设备之间接口连接的控制器,该控制器包括:

配置为在主机和控制器之间使用NAND接口协议传输数据的第一NAND接口,其中第一NAND接口还被配置为从主机接收(i)读命令和写命令中的一个和(ii)逻辑地址;

配置为将从主机接收的逻辑地址转换为闪存设备的物理地址的地址转换模块;

配置为在控制器和闪存设备之间使用NAND接口协议根据从主机接收的读命令和写命令中的一个传输数据的第二NAND接口;和

ECC模块,配置为计算通过第一和第二NAND接口中的至少一个接收的数据的ECC比特。

19.如权利要求18所述的控制器,还包括加密模块。

20.如权利要求18所述的控制器,其中第一NAND接口使用的NAND接口协议与由第二NAND接口使用的NAND接口协议相同。

21.如权利要求18所述的控制器,其中第一NAND接口使用的NAND接口协议与由第二NAND接口使用的NAND接口协议不同。

22.如权利要求18所述的控制器,其中主机和控制器之间的总线与控制器和闪存设备之间的总线不同。

23.如权利要求18所述的控制器,其中控制器和闪存设备都位于共同的多芯片封装包中。

24.如权利要求18所述的控制器,其中控制器和闪存设备被封装在不同的封装包中。

25.如权利要求18所述的控制器,其中控制器和闪存设备被集成在相同的管芯上。

26.一种用于在主机和闪存设备之间接口连接的控制器,该控制器包括:

配置为在主机和控制器之间使用NAND接口协议传输数据的第一NAND接口,其中第一NAND接口还被配置为从主机接收(i)读命令和写命令中的一个和(ii)闪存设备的物理地址;

配置为在控制器和闪存设备之间使用NAND接口协议根据从主机接收的读命令和写命令中的一个传输数据的第二NAND接口;

ECC模块,配置为计算通过第一和第二NAND接口中的至少一个接收的数据的ECC比特;和

将从主机接收的逻辑闪存地址映射到发送给闪存设备的物理地址的模块。

27.如权利要求26所述的控制器,进一步包括加密模块。

28.如权利要求26所述的控制器,其中第一NAND接口使用的NAND接口协议与由第二NAND接口使用的NAND接口协议相同。

29.如权利要求26所述的控制器,其中第一NAND接口使用的NAND接口协议与由第二NAND接口使用的NAND接口协议不同。

30.如权利要求26所述的控制器,其中主机和控制器之间的总线与控制器和闪存设备之间的总线不同。

31.如权利要求26所述的控制器,其中控制器和闪存设备都位于共同的多芯片封装包中。

32.如权利要求26所述的控制器,其中控制器和闪存设备被封装在不同的封装包中。

33.如权利要求26所述的控制器,其中控制器和闪存设备被集成在相同的管芯上。

34.一种用于在主机和闪存设备之间接口连接的方法,该方法包括:

在与主机和闪存设备通信的控制器中执行:

接收(i)读命令和写命令中的一个和(ii)逻辑地址,其中通过控制器的第一NAND接口使用NAND接口协议接收(i)读命令和写命令中的一个和(ii)逻辑地址;

将从主机接收的逻辑地址转换成闪存设备的物理地址;

在主机和控制器之间根据从主机接收的读命令和写命令中的一个传输数据,其中通过控制器的第一NAND接口使用NAND接口协议传输数据;

在控制器和闪存设备的物理地址之间根据从主机接收的读命令和写命令中的一个传输数据,其中通过控制器的第二NAND接口使用NAND接口协议传输数据;和

计算通过第一和第二NAND接口中的至少一个接收的数据的ECC比特。

35.如权利要求34所述的方法,进一步包括对通过第一和第二NAND接口中的至少一个接收的数据执行加密功能。

36.如权利要求34所述的方法,其中第一NAND接口使用的NAND接口协议与由第二NAND接口使用的NAND接口协议相同。

37.如权利要求34所述的方法,其中第一NAND接口使用的NAND接口协议与由第二NAND接口使用的NAND接口协议不同。

38.如权利要求34所述的方法,其中主机和控制器之间的总线与控制器和闪存设备之间的总线不同。

39.如权利要求34所述的方法,其中控制器和闪存设备都位于共同的多管芯封装包中。

40.如权利要求34所述的方法,其中控制器和闪存设备被封装在不同的封装包中。

41.如权利要求34所述的方法,其中控制器和闪存设备被集成在相同的管芯上。

42.一种用于在主机和闪存设备之间接口连接的方法,该方法包括:

在与主机和闪存设备通信的控制器中执行:

从主机接收(i)读命令和写命令中的一个和(ii)闪存设备的物理地址,其中通过控制器的第一NAND接口使用NAND接口协议接收(i)读命令和写命令中的一个和(ii)物理地址;

在主机和控制器之间根据从主机接收的读命令和写命令中的一个传输数据,其中通过控制器的第一NAND接口使用NAND接口协议传输数据;

在控制器和闪存设备的物理地址之间根据从主机接收的读命令和写命令中的一个传输数据,其中通过控制器的第二NAND接口使用NAND接口协议传输数据;

计算通过第一和第二NAND接口中的至少一个接收的数据的ECC比特;和

将从主机接收的逻辑闪存地址映射到发送给闪存设备的物理地址。

43.如权利要求42所述的方法,进一步包括对于通过第一和第二NAND接口中的至少一个接收的数据执行加密功能。

44.如权利要求42所述的方法,其中第一NAND接口使用的NAND接口协议与由第二NAND接口使用的NAND接口协议相同。

45.如权利要求42所述的方法,其中第一NAND接口使用的NAND接口协议与由第二NAND接口使用的NAND接口协议不同。

46.如权利要求42所述的方法,其中主机和控制器之间的总线与控制器和闪存设备之间的总线不同。

47.如权利要求42所述的方法,其中控制器和闪存设备都位于共同的多芯片封装包中。

48.如权利要求42所述的方法,其中控制器和闪存设备被封装在不同的封装包中。

49.如权利要求42所述的方法,其中控制器和闪存设备被集成在相同的管芯上。

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US72009805P | 2005-09-26 | 2005-09-26 | |

| US60/720,098 | 2005-09-26 | ||

| US11/326,336 US7631245B2 (en) | 2005-09-26 | 2006-01-06 | NAND flash memory controller exporting a NAND interface |

| US11/326,336 | 2006-01-06 | ||

| PCT/IL2006/001101 WO2007034481A2 (en) | 2005-09-26 | 2006-09-20 | A nand flash memory controller exporting a nand interface |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN101366182A CN101366182A (zh) | 2009-02-11 |

| CN101366182B true CN101366182B (zh) | 2012-04-18 |

Family

ID=37889248

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN2006800356310A Active CN101366182B (zh) | 2005-09-26 | 2006-09-20 | 输出nand接口的nand闪存控制器 |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US7631245B2 (zh) |

| EP (2) | EP1929483A4 (zh) |

| JP (1) | JP2009510560A (zh) |

| KR (2) | KR20080050433A (zh) |

| CN (1) | CN101366182B (zh) |

| WO (1) | WO2007034481A2 (zh) |

Families Citing this family (172)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4818812B2 (ja) * | 2006-05-31 | 2011-11-16 | 株式会社日立製作所 | フラッシュメモリストレージシステム |

| US7012835B2 (en) | 2003-10-03 | 2006-03-14 | Sandisk Corporation | Flash memory data correction and scrub techniques |

| US7424659B2 (en) * | 2003-10-31 | 2008-09-09 | Sandisk Il Ltd. | System-in-package and method of testing thereof |

| US20060077119A1 (en) * | 2004-10-08 | 2006-04-13 | Sharp Laboratories Of America, Inc. | Methods and systems for receiving content at an imaging device |

| US8291295B2 (en) * | 2005-09-26 | 2012-10-16 | Sandisk Il Ltd. | NAND flash memory controller exporting a NAND interface |

| US7631245B2 (en) * | 2005-09-26 | 2009-12-08 | Sandisk Il Ltd. | NAND flash memory controller exporting a NAND interface |

| JP4997798B2 (ja) * | 2006-03-15 | 2012-08-08 | ソニー株式会社 | 不揮発性半導体記憶装置およびメモリシステム |

| WO2007132452A2 (en) * | 2006-05-12 | 2007-11-22 | Anobit Technologies | Reducing programming error in memory devices |

| WO2007132456A2 (en) * | 2006-05-12 | 2007-11-22 | Anobit Technologies Ltd. | Memory device with adaptive capacity |

| WO2007132457A2 (en) * | 2006-05-12 | 2007-11-22 | Anobit Technologies Ltd. | Combined distortion estimation and error correction coding for memory devices |

| WO2007132453A2 (en) | 2006-05-12 | 2007-11-22 | Anobit Technologies Ltd. | Distortion estimation and cancellation in memory devices |

| US7613043B2 (en) * | 2006-05-15 | 2009-11-03 | Apple Inc. | Shifting reference values to account for voltage sag |

| US8000134B2 (en) * | 2006-05-15 | 2011-08-16 | Apple Inc. | Off-die charge pump that supplies multiple flash devices |

| US7639542B2 (en) * | 2006-05-15 | 2009-12-29 | Apple Inc. | Maintenance operations for multi-level data storage cells |

| US7551486B2 (en) * | 2006-05-15 | 2009-06-23 | Apple Inc. | Iterative memory cell charging based on reference cell value |

| US7852690B2 (en) * | 2006-05-15 | 2010-12-14 | Apple Inc. | Multi-chip package for a flash memory |

| US7568135B2 (en) * | 2006-05-15 | 2009-07-28 | Apple Inc. | Use of alternative value in cell detection |

| US7639531B2 (en) * | 2006-05-15 | 2009-12-29 | Apple Inc. | Dynamic cell bit resolution |

| US7511646B2 (en) * | 2006-05-15 | 2009-03-31 | Apple Inc. | Use of 8-bit or higher A/D for NAND cell value |

| US7701797B2 (en) * | 2006-05-15 | 2010-04-20 | Apple Inc. | Two levels of voltage regulation supplied for logic and data programming voltage of a memory device |

| US7911834B2 (en) * | 2006-05-15 | 2011-03-22 | Apple Inc. | Analog interface for a flash memory die |

| JP2007323321A (ja) * | 2006-05-31 | 2007-12-13 | Toshiba Corp | 半導体記憶装置およびそのデータ送信方法 |

| US7567461B2 (en) * | 2006-08-18 | 2009-07-28 | Micron Technology, Inc. | Method and system for minimizing number of programming pulses used to program rows of non-volatile memory cells |

| US20080046630A1 (en) * | 2006-08-21 | 2008-02-21 | Sandisk Il Ltd. | NAND flash memory controller exporting a logical sector-based interface |

| US20080046641A1 (en) * | 2006-08-21 | 2008-02-21 | Sandisk Il Ltd. | NAND flash memory controller exporting a logical sector-based interface |

| US8060806B2 (en) | 2006-08-27 | 2011-11-15 | Anobit Technologies Ltd. | Estimation of non-linear distortion in memory devices |

| US7886204B2 (en) | 2006-09-27 | 2011-02-08 | Sandisk Corporation | Methods of cell population distribution assisted read margining |

| US7821826B2 (en) | 2006-10-30 | 2010-10-26 | Anobit Technologies, Ltd. | Memory cell readout using successive approximation |

| WO2008053472A2 (en) * | 2006-10-30 | 2008-05-08 | Anobit Technologies Ltd. | Reading memory cells using multiple thresholds |

| US7924648B2 (en) | 2006-11-28 | 2011-04-12 | Anobit Technologies Ltd. | Memory power and performance management |

| WO2008068747A2 (en) * | 2006-12-03 | 2008-06-12 | Anobit Technologies Ltd. | Automatic defect management in memory devices |

| US7593263B2 (en) * | 2006-12-17 | 2009-09-22 | Anobit Technologies Ltd. | Memory device with reduced reading latency |

| US7900102B2 (en) * | 2006-12-17 | 2011-03-01 | Anobit Technologies Ltd. | High-speed programming of memory devices |

| US8151166B2 (en) * | 2007-01-24 | 2012-04-03 | Anobit Technologies Ltd. | Reduction of back pattern dependency effects in memory devices |

| US7751240B2 (en) | 2007-01-24 | 2010-07-06 | Anobit Technologies Ltd. | Memory device with negative thresholds |

| WO2008111058A2 (en) * | 2007-03-12 | 2008-09-18 | Anobit Technologies Ltd. | Adaptive estimation of memory cell read thresholds |

| US20080250192A1 (en) * | 2007-04-05 | 2008-10-09 | Phison Electronics Corp. | Integrating flash memory system |

| US8001320B2 (en) * | 2007-04-22 | 2011-08-16 | Anobit Technologies Ltd. | Command interface for memory devices |

| US8429493B2 (en) | 2007-05-12 | 2013-04-23 | Apple Inc. | Memory device with internal signap processing unit |

| US8234545B2 (en) * | 2007-05-12 | 2012-07-31 | Apple Inc. | Data storage with incremental redundancy |

| US20080306723A1 (en) * | 2007-06-08 | 2008-12-11 | Luca De Ambroggi | Emulated Combination Memory Device |

| US8504897B2 (en) * | 2007-06-21 | 2013-08-06 | Megachips Corporation | Memory controller |

| US7966547B2 (en) * | 2007-07-02 | 2011-06-21 | International Business Machines Corporation | Multi-bit error correction scheme in multi-level memory storage system |

| US7925936B1 (en) | 2007-07-13 | 2011-04-12 | Anobit Technologies Ltd. | Memory device with non-uniform programming levels |

| US9207661B2 (en) * | 2007-07-20 | 2015-12-08 | GM Global Technology Operations LLC | Dual core architecture of a control module of an engine |

| US8259497B2 (en) | 2007-08-06 | 2012-09-04 | Apple Inc. | Programming schemes for multi-level analog memory cells |

| US8174905B2 (en) * | 2007-09-19 | 2012-05-08 | Anobit Technologies Ltd. | Programming orders for reducing distortion in arrays of multi-level analog memory cells |

| US7773413B2 (en) | 2007-10-08 | 2010-08-10 | Anobit Technologies Ltd. | Reliable data storage in analog memory cells in the presence of temperature variations |

| US8103936B2 (en) * | 2007-10-17 | 2012-01-24 | Micron Technology, Inc. | System and method for data read of a synchronous serial interface NAND |

| US8068360B2 (en) * | 2007-10-19 | 2011-11-29 | Anobit Technologies Ltd. | Reading analog memory cells using built-in multi-threshold commands |

| US8000141B1 (en) | 2007-10-19 | 2011-08-16 | Anobit Technologies Ltd. | Compensation for voltage drifts in analog memory cells |

| WO2009050703A2 (en) * | 2007-10-19 | 2009-04-23 | Anobit Technologies | Data storage in analog memory cell arrays having erase failures |

| WO2009063450A2 (en) * | 2007-11-13 | 2009-05-22 | Anobit Technologies | Optimized selection of memory units in multi-unit memory devices |

| US8225181B2 (en) | 2007-11-30 | 2012-07-17 | Apple Inc. | Efficient re-read operations from memory devices |

| US8209588B2 (en) * | 2007-12-12 | 2012-06-26 | Anobit Technologies Ltd. | Efficient interference cancellation in analog memory cell arrays |

| US8456905B2 (en) | 2007-12-16 | 2013-06-04 | Apple Inc. | Efficient data storage in multi-plane memory devices |

| US20090172246A1 (en) * | 2007-12-26 | 2009-07-02 | Sandisk Il Ltd. | Device and method for managing initialization thereof |

| US8085586B2 (en) * | 2007-12-27 | 2011-12-27 | Anobit Technologies Ltd. | Wear level estimation in analog memory cells |

| US8068365B2 (en) | 2008-02-04 | 2011-11-29 | Mosaid Technologies Incorporated | Non-volatile memory device having configurable page size |

| US8156398B2 (en) * | 2008-02-05 | 2012-04-10 | Anobit Technologies Ltd. | Parameter estimation based on error correction code parity check equations |

| US7924587B2 (en) * | 2008-02-21 | 2011-04-12 | Anobit Technologies Ltd. | Programming of analog memory cells using a single programming pulse per state transition |

| US7864573B2 (en) | 2008-02-24 | 2011-01-04 | Anobit Technologies Ltd. | Programming analog memory cells for reduced variance after retention |

| US8230300B2 (en) * | 2008-03-07 | 2012-07-24 | Apple Inc. | Efficient readout from analog memory cells using data compression |

| US8099539B2 (en) * | 2008-03-10 | 2012-01-17 | Lsi Corporation | Method and system of a shared bus architecture |

| US8400858B2 (en) | 2008-03-18 | 2013-03-19 | Apple Inc. | Memory device with reduced sense time readout |

| US8059457B2 (en) | 2008-03-18 | 2011-11-15 | Anobit Technologies Ltd. | Memory device with multiple-accuracy read commands |

| US8521979B2 (en) | 2008-05-29 | 2013-08-27 | Micron Technology, Inc. | Memory systems and methods for controlling the timing of receiving read data |

| US7979757B2 (en) | 2008-06-03 | 2011-07-12 | Micron Technology, Inc. | Method and apparatus for testing high capacity/high bandwidth memory devices |

| US7855931B2 (en) | 2008-07-21 | 2010-12-21 | Micron Technology, Inc. | Memory system and method using stacked memory device dice, and system using the memory system |

| US8756486B2 (en) * | 2008-07-02 | 2014-06-17 | Micron Technology, Inc. | Method and apparatus for repairing high capacity/high bandwidth memory devices |

| US8289760B2 (en) | 2008-07-02 | 2012-10-16 | Micron Technology, Inc. | Multi-mode memory device and method having stacked memory dice, a logic die and a command processing circuit and operating in direct and indirect modes |

| US7924613B1 (en) | 2008-08-05 | 2011-04-12 | Anobit Technologies Ltd. | Data storage in analog memory cells with protection against programming interruption |

| US7995388B1 (en) | 2008-08-05 | 2011-08-09 | Anobit Technologies Ltd. | Data storage using modified voltages |

| US8127204B2 (en) | 2008-08-15 | 2012-02-28 | Micron Technology, Inc. | Memory system and method using a memory device die stacked with a logic die using data encoding, and system using the memory system |

| US8949684B1 (en) | 2008-09-02 | 2015-02-03 | Apple Inc. | Segmented data storage |

| US8169825B1 (en) | 2008-09-02 | 2012-05-01 | Anobit Technologies Ltd. | Reliable data storage in analog memory cells subjected to long retention periods |

| US8482978B1 (en) | 2008-09-14 | 2013-07-09 | Apple Inc. | Estimation of memory cell read thresholds by sampling inside programming level distribution intervals |

| US8000135B1 (en) | 2008-09-14 | 2011-08-16 | Anobit Technologies Ltd. | Estimation of memory cell read thresholds by sampling inside programming level distribution intervals |

| TWI475378B (zh) * | 2008-10-09 | 2015-03-01 | Micron Technology Inc | 耦合至一主機之儲存系統、與儲存系統中之nand記憶體介接之控制器及管理nand記憶體裝置堆疊之方法 |

| WO2010041093A1 (en) | 2008-10-09 | 2010-04-15 | Federico Tiziani | Virtualized ecc nand |

| US8239734B1 (en) | 2008-10-15 | 2012-08-07 | Apple Inc. | Efficient data storage in storage device arrays |

| US8261159B1 (en) | 2008-10-30 | 2012-09-04 | Apple, Inc. | Data scrambling schemes for memory devices |

| TWI396202B (zh) * | 2008-11-14 | 2013-05-11 | Phison Electronics Corp | 錯誤校正控制器及其快閃記憶體晶片系統與錯誤校正方法 |

| US8208304B2 (en) * | 2008-11-16 | 2012-06-26 | Anobit Technologies Ltd. | Storage at M bits/cell density in N bits/cell analog memory cell devices, M>N |

| US8316201B2 (en) * | 2008-12-18 | 2012-11-20 | Sandisk Il Ltd. | Methods for executing a command to write data from a source location to a destination location in a memory device |

| US8248831B2 (en) * | 2008-12-31 | 2012-08-21 | Apple Inc. | Rejuvenation of analog memory cells |

| US8397131B1 (en) | 2008-12-31 | 2013-03-12 | Apple Inc. | Efficient readout schemes for analog memory cell devices |

| US8924661B1 (en) * | 2009-01-18 | 2014-12-30 | Apple Inc. | Memory system including a controller and processors associated with memory devices |

| US8228701B2 (en) | 2009-03-01 | 2012-07-24 | Apple Inc. | Selective activation of programming schemes in analog memory cell arrays |

| US8832354B2 (en) * | 2009-03-25 | 2014-09-09 | Apple Inc. | Use of host system resources by memory controller |

| US8259506B1 (en) | 2009-03-25 | 2012-09-04 | Apple Inc. | Database of memory read thresholds |

| US8238157B1 (en) | 2009-04-12 | 2012-08-07 | Apple Inc. | Selective re-programming of analog memory cells |

| US8479080B1 (en) | 2009-07-12 | 2013-07-02 | Apple Inc. | Adaptive over-provisioning in memory systems |

| US20110040924A1 (en) | 2009-08-11 | 2011-02-17 | Selinger Robert D | Controller and Method for Detecting a Transmission Error Over a NAND Interface Using Error Detection Code |

| US20110041039A1 (en) * | 2009-08-11 | 2011-02-17 | Eliyahou Harari | Controller and Method for Interfacing Between a Host Controller in a Host and a Flash Memory Device |

| US20110041005A1 (en) * | 2009-08-11 | 2011-02-17 | Selinger Robert D | Controller and Method for Providing Read Status and Spare Block Management Information in a Flash Memory System |

| US8205038B2 (en) * | 2009-10-14 | 2012-06-19 | Giga-Byte Technology Co., Ltd. | Flash memory accessing apparatus and accessing method thereof |

| US8495465B1 (en) | 2009-10-15 | 2013-07-23 | Apple Inc. | Error correction coding over multiple memory pages |

| US8677054B1 (en) | 2009-12-16 | 2014-03-18 | Apple Inc. | Memory management schemes for non-volatile memory devices |

| US8595411B2 (en) | 2009-12-30 | 2013-11-26 | Sandisk Technologies Inc. | Method and controller for performing a sequence of commands |

| US8443263B2 (en) * | 2009-12-30 | 2013-05-14 | Sandisk Technologies Inc. | Method and controller for performing a copy-back operation |

| US8694814B1 (en) | 2010-01-10 | 2014-04-08 | Apple Inc. | Reuse of host hibernation storage space by memory controller |

| US8677203B1 (en) | 2010-01-11 | 2014-03-18 | Apple Inc. | Redundant data storage schemes for multi-die memory systems |

| KR101096268B1 (ko) | 2010-04-01 | 2011-12-22 | 주식회사 하이닉스반도체 | 커맨드디코더 및 반도체 메모리 장치 |

| US8694853B1 (en) | 2010-05-04 | 2014-04-08 | Apple Inc. | Read commands for reading interfering memory cells |

| CN101908131B (zh) * | 2010-06-01 | 2013-03-27 | 福建新大陆电脑股份有限公司 | 基于usb接口的条码解码装置 |

| US8572423B1 (en) | 2010-06-22 | 2013-10-29 | Apple Inc. | Reducing peak current in memory systems |

| US8595591B1 (en) | 2010-07-11 | 2013-11-26 | Apple Inc. | Interference-aware assignment of programming levels in analog memory cells |

| US8555050B2 (en) | 2010-07-15 | 2013-10-08 | Broadcom Corporation | Apparatus and method thereof for reliable booting from NAND flash memory |

| US9104580B1 (en) | 2010-07-27 | 2015-08-11 | Apple Inc. | Cache memory for hybrid disk drives |

| US8645794B1 (en) | 2010-07-31 | 2014-02-04 | Apple Inc. | Data storage in analog memory cells using a non-integer number of bits per cell |

| US8856475B1 (en) | 2010-08-01 | 2014-10-07 | Apple Inc. | Efficient selection of memory blocks for compaction |

| US8694854B1 (en) | 2010-08-17 | 2014-04-08 | Apple Inc. | Read threshold setting based on soft readout statistics |

| US9021181B1 (en) | 2010-09-27 | 2015-04-28 | Apple Inc. | Memory management for unifying memory cell conditions by using maximum time intervals |

| KR101401379B1 (ko) * | 2010-10-13 | 2014-05-30 | 한국전자통신연구원 | 낸드 플래시 메모리의 데이터 입출력 방법과 그 방법을 이용한 임베디드 시스템 |

| US8400808B2 (en) | 2010-12-16 | 2013-03-19 | Micron Technology, Inc. | Phase interpolators and push-pull buffers |

| US20120167100A1 (en) * | 2010-12-23 | 2012-06-28 | Yan Li | Manual suspend and resume for non-volatile memory |

| US8819328B2 (en) | 2010-12-30 | 2014-08-26 | Sandisk Technologies Inc. | Controller and method for performing background operations |

| US20120297248A1 (en) * | 2011-05-17 | 2012-11-22 | Alan David Bennett | Block write handling after corruption |

| US8694719B2 (en) | 2011-06-24 | 2014-04-08 | Sandisk Technologies Inc. | Controller, storage device, and method for power throttling memory operations |

| US9218852B2 (en) | 2011-06-30 | 2015-12-22 | Sandisk Technologies Inc. | Smart bridge for memory core |

| US9003102B2 (en) | 2011-08-26 | 2015-04-07 | Sandisk Technologies Inc. | Controller with extended status register and method of use therewith |

| US9195530B1 (en) | 2011-09-06 | 2015-11-24 | Western Digital Technologies, Inc. | Systems and methods for improved data management in data storage systems |

| US8700834B2 (en) | 2011-09-06 | 2014-04-15 | Western Digital Technologies, Inc. | Systems and methods for an enhanced controller architecture in data storage systems |

| US8713357B1 (en) | 2011-09-06 | 2014-04-29 | Western Digital Technologies, Inc. | Systems and methods for detailed error reporting in data storage systems |

| US8707104B1 (en) | 2011-09-06 | 2014-04-22 | Western Digital Technologies, Inc. | Systems and methods for error injection in data storage systems |

| JP2013061799A (ja) * | 2011-09-13 | 2013-04-04 | Toshiba Corp | 記憶装置、記憶装置の制御方法およびコントローラ |

| KR101300443B1 (ko) * | 2011-09-22 | 2013-08-27 | 서울대학교산학협력단 | 바이패스 경로를 이용하여 신뢰성 검증을 할 수 있는 플래시 메모리 저장 장치, 및 이를 이용한 플래시 메모리 저장 장치의 신뢰성 검증 시스템 및 방법 |

| CN102436426A (zh) * | 2011-11-04 | 2012-05-02 | 忆正存储技术(武汉)有限公司 | 一种内嵌式存储器及内嵌式存储系统 |

| US8687421B2 (en) | 2011-11-21 | 2014-04-01 | Sandisk Technologies Inc. | Scrub techniques for use with dynamic read |

| US8700961B2 (en) | 2011-12-20 | 2014-04-15 | Sandisk Technologies Inc. | Controller and method for virtual LUN assignment for improved memory bank mapping |

| US9208070B2 (en) | 2011-12-20 | 2015-12-08 | Sandisk Technologies Inc. | Wear leveling of multiple memory devices |

| US9116620B2 (en) | 2011-12-30 | 2015-08-25 | Sandisk Technologies Inc. | Controller and method for memory aliasing for different flash memory types |

| US9141308B2 (en) | 2011-12-30 | 2015-09-22 | Sandisk Technologies Inc. | Controller and method for using a transaction flag for page protection |

| US20130191580A1 (en) * | 2012-01-23 | 2013-07-25 | Menahem Lasser | Controller, System, and Method for Mapping Logical Sector Addresses to Physical Addresses |

| US9058419B2 (en) | 2012-03-14 | 2015-06-16 | GM Global Technology Operations LLC | System and method for verifying the integrity of a safety-critical vehicle control system |

| US9053008B1 (en) | 2012-03-26 | 2015-06-09 | Western Digital Technologies, Inc. | Systems and methods for providing inline parameter service in data storage devices |

| US8760922B2 (en) | 2012-04-10 | 2014-06-24 | Sandisk Technologies Inc. | System and method for micro-tiering in non-volatile memory |

| KR101979732B1 (ko) * | 2012-05-04 | 2019-08-28 | 삼성전자 주식회사 | 비휘발성 메모리 컨트롤러 및 비휘발성 메모리 시스템 |

| US8856431B2 (en) * | 2012-08-02 | 2014-10-07 | Lsi Corporation | Mixed granularity higher-level redundancy for non-volatile memory |

| US8938656B2 (en) | 2012-09-14 | 2015-01-20 | Sandisk Technologies Inc. | Data storage device with intermediate ECC stage |

| US9471484B2 (en) | 2012-09-19 | 2016-10-18 | Novachips Canada Inc. | Flash memory controller having dual mode pin-out |

| CN102929655A (zh) * | 2012-09-26 | 2013-02-13 | 瑞斯康达科技发展股份有限公司 | 向闪存芯片中烧写数据文件的方法、预处理方法及装置 |

| US8990670B2 (en) * | 2012-09-28 | 2015-03-24 | Intel Corporation | Endurance aware error-correcting code (ECC) protection for non-volatile memories |

| US9257203B2 (en) | 2012-12-06 | 2016-02-09 | Micron Technology, Inc. | Setting a default read signal based on error correction |

| US9171597B2 (en) | 2013-08-30 | 2015-10-27 | Micron Technology, Inc. | Apparatuses and methods for providing strobe signals to memories |

| CN104425014B (zh) * | 2013-09-02 | 2018-02-27 | 华邦电子股份有限公司 | 序列式nand型闪存、闪存装置及其操作方法 |

| US9230689B2 (en) | 2014-03-17 | 2016-01-05 | Sandisk Technologies Inc. | Finding read disturbs on non-volatile memories |

| KR20150116352A (ko) | 2014-04-07 | 2015-10-15 | 삼성전자주식회사 | 메모리 제어 방법 및 시스템 |

| KR102211709B1 (ko) | 2014-05-19 | 2021-02-02 | 삼성전자주식회사 | 신호 송수신 특성을 향상한 불휘발성 메모리 시스템, 호스트 장치, 불휘발성 메모리 시스템 및 호스트의 동작방법 |

| JP2014238871A (ja) * | 2014-08-01 | 2014-12-18 | マイクロン テクノロジー, インク. | 単一の仮想化されたeccアルゴリズムを提供するコントローラと、このコントローラを含む記憶システム、及びこの記憶システムを管理する方法 |

| US9767045B2 (en) | 2014-08-29 | 2017-09-19 | Memory Technologies Llc | Control for authenticated accesses to a memory device |

| US9552171B2 (en) | 2014-10-29 | 2017-01-24 | Sandisk Technologies Llc | Read scrub with adaptive counter management |

| US9978456B2 (en) | 2014-11-17 | 2018-05-22 | Sandisk Technologies Llc | Techniques for reducing read disturb in partially written blocks of non-volatile memory |

| US9349479B1 (en) | 2014-11-18 | 2016-05-24 | Sandisk Technologies Inc. | Boundary word line operation in nonvolatile memory |

| US9449700B2 (en) | 2015-02-13 | 2016-09-20 | Sandisk Technologies Llc | Boundary word line search and open block read methods with reduced read disturb |

| TWI567633B (zh) * | 2015-07-07 | 2017-01-21 | 鈺群科技股份有限公司 | 通用序列匯流排相容的隨身碟的啟動方法及其相關隨身碟 |

| US9653154B2 (en) | 2015-09-21 | 2017-05-16 | Sandisk Technologies Llc | Write abort detection for multi-state memories |

| US9946642B2 (en) | 2015-11-13 | 2018-04-17 | Samsung Electronics Co., Ltd | Distributed multimode storage management |

| US9940028B2 (en) * | 2015-11-13 | 2018-04-10 | Samsung Electronics Co., Ltd | Multimode storage device |

| JP2018022383A (ja) * | 2016-08-04 | 2018-02-08 | 東芝メモリ株式会社 | メモリシステム |

| US10740174B2 (en) | 2016-11-29 | 2020-08-11 | Taiwan Semiconductor Manufacturing Company, Ltd. | Memory address protection circuit and method |

| CN108958961B (zh) * | 2017-05-22 | 2021-11-30 | 上海宝存信息科技有限公司 | 数据储存装置以及数据错误管理方法 |

| US11099789B2 (en) | 2018-02-05 | 2021-08-24 | Micron Technology, Inc. | Remote direct memory access in multi-tier memory systems |

| US20190243787A1 (en) * | 2018-02-05 | 2019-08-08 | Micron Technology, Inc. | Memory Systems having Controllers Embedded in Packages of Integrated Circuit Memory |

| US10782908B2 (en) | 2018-02-05 | 2020-09-22 | Micron Technology, Inc. | Predictive data orchestration in multi-tier memory systems |

| US11416395B2 (en) | 2018-02-05 | 2022-08-16 | Micron Technology, Inc. | Memory virtualization for accessing heterogeneous memory components |

| US10852949B2 (en) | 2019-04-15 | 2020-12-01 | Micron Technology, Inc. | Predictive data pre-fetching in a data storage device |

| US11861022B2 (en) * | 2020-05-20 | 2024-01-02 | Silicon Motion, Inc. | Method and computer program product and apparatus for encrypting and decrypting physical-address information |

| US11556416B2 (en) | 2021-05-05 | 2023-01-17 | Apple Inc. | Controlling memory readout reliability and throughput by adjusting distance between read thresholds |

| US11847342B2 (en) | 2021-07-28 | 2023-12-19 | Apple Inc. | Efficient transfer of hard data and confidence levels in reading a nonvolatile memory |

| US11822813B2 (en) | 2021-12-28 | 2023-11-21 | Samsung Electronics Co., Ltd. | Storage device, operation method of storage device, and storage system using the same |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP1146428A1 (en) * | 2000-04-13 | 2001-10-17 | Yao, Li-ho | Multi-interface memory card and adapter module for the same |

| CN1649032A (zh) * | 2004-01-29 | 2005-08-03 | 群联电子股份有限公司 | 具防写功能的微型存储装置 |

Family Cites Families (92)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5268870A (en) * | 1988-06-08 | 1993-12-07 | Eliyahou Harari | Flash EEPROM system and intelligent programming and erasing methods therefor |

| US5430859A (en) | 1991-07-26 | 1995-07-04 | Sundisk Corporation | Solid state memory system including plural memory chips and a serialized bus |

| US6230233B1 (en) | 1991-09-13 | 2001-05-08 | Sandisk Corporation | Wear leveling techniques for flash EEPROM systems |

| US5532962A (en) | 1992-05-20 | 1996-07-02 | Sandisk Corporation | Soft errors handling in EEPROM devices |

| US5404485A (en) | 1993-03-08 | 1995-04-04 | M-Systems Flash Disk Pioneers Ltd. | Flash file system |

| US5799168A (en) | 1996-01-05 | 1998-08-25 | M-Systems Flash Disk Pioneers Ltd. | Standardized flash controller |

| US5818757A (en) | 1996-07-22 | 1998-10-06 | Invox Technology | Analog and multi-level memory with reduced program disturb |

| JP3565687B2 (ja) | 1997-08-06 | 2004-09-15 | 沖電気工業株式会社 | 半導体記憶装置およびその制御方法 |

| US5937425A (en) | 1997-10-16 | 1999-08-10 | M-Systems Flash Disk Pioneers Ltd. | Flash file system optimized for page-mode flash technologies |

| JP3638770B2 (ja) * | 1997-12-05 | 2005-04-13 | 東京エレクトロンデバイス株式会社 | テスト機能を備える記憶装置 |

| US5943283A (en) | 1997-12-05 | 1999-08-24 | Invox Technology | Address scrambling in a semiconductor memory |

| JPH11297066A (ja) * | 1998-04-10 | 1999-10-29 | Ricoh Co Ltd | 半導体装置 |

| US6034882A (en) | 1998-11-16 | 2000-03-07 | Matrix Semiconductor, Inc. | Vertically stacked field programmable nonvolatile memory and method of fabrication |

| US6498851B1 (en) | 1998-11-25 | 2002-12-24 | Sandisk Corporation | Data encryption and signal scrambling using programmable data conversion arrays |

| US6181599B1 (en) | 1999-04-13 | 2001-01-30 | Sandisk Corporation | Method for applying variable row BIAS to reduce program disturb in a flash memory storage array |

| US6426893B1 (en) * | 2000-02-17 | 2002-07-30 | Sandisk Corporation | Flash eeprom system with simultaneous multiple data sector programming and storage of physical block characteristics in other designated blocks |

| JP2001297038A (ja) | 2000-04-11 | 2001-10-26 | Toshiba Corp | データ記憶装置および記録媒体並びに記録媒体制御方法 |

| US6631085B2 (en) | 2000-04-28 | 2003-10-07 | Matrix Semiconductor, Inc. | Three-dimensional memory array incorporating serial chain diode stack |

| US6420215B1 (en) | 2000-04-28 | 2002-07-16 | Matrix Semiconductor, Inc. | Three-dimensional memory array and method of fabrication |

| US20030120858A1 (en) | 2000-09-15 | 2003-06-26 | Matrix Semiconductor, Inc. | Memory devices and methods for use therewith |

| US7020739B2 (en) | 2000-12-06 | 2006-03-28 | Tdk Corporation | Memory controller, flash memory system having memory controller and method for controlling flash memory device |

| US6591330B2 (en) | 2001-06-18 | 2003-07-08 | M-Systems Flash Disk Pioneers Ltd. | System and method for flexible flash file |

| US6760805B2 (en) | 2001-09-05 | 2004-07-06 | M-Systems Flash Disk Pioneers Ltd. | Flash management system for large page size |

| TW516118B (en) | 2001-09-11 | 2003-01-01 | Leadtek Research Inc | Decoding conversion device and method capable of supporting multiple memory chips and their application system |

| GB0123416D0 (en) * | 2001-09-28 | 2001-11-21 | Memquest Ltd | Non-volatile memory control |

| GB0123415D0 (en) * | 2001-09-28 | 2001-11-21 | Memquest Ltd | Method of writing data to non-volatile memory |

| GB0123412D0 (en) | 2001-09-28 | 2001-11-21 | Memquest Ltd | Memory system sectors |

| US6778436B2 (en) * | 2001-10-10 | 2004-08-17 | Fong Piau | Apparatus and architecture for a compact flash memory controller |

| US6859856B2 (en) | 2001-10-23 | 2005-02-22 | Flex P Industries Sdn. Bhd | Method and system for a compact flash memory controller |

| US6704852B2 (en) | 2001-11-16 | 2004-03-09 | Key Technology Corporation | Control device applicable to flash memory card and method for building partial lookup table |

| US6977847B2 (en) | 2001-11-23 | 2005-12-20 | M-Systems Flash Disk Pioneers Ltd. | Detecting partially erased units in flash devices |

| TWI240861B (en) | 2002-01-11 | 2005-10-01 | Integrated Circuit Solution In | Data access method and architecture of flash memory |

| US6683817B2 (en) * | 2002-02-21 | 2004-01-27 | Qualcomm, Incorporated | Direct memory swapping between NAND flash and SRAM with error correction coding |

| US20030206442A1 (en) * | 2002-05-02 | 2003-11-06 | Jerry Tang | Flash memory bridiging device, method and application system |

| US6721820B2 (en) | 2002-05-15 | 2004-04-13 | M-Systems Flash Disk Pioneers Ltd. | Method for improving performance of a flash-based storage system using specialized flash controllers |

| US7081377B2 (en) | 2002-06-27 | 2006-07-25 | Sandisk 3D Llc | Three-dimensional memory |

| KR100448905B1 (ko) * | 2002-07-29 | 2004-09-16 | 삼성전자주식회사 | 낸드플래쉬메모리를 시스템구동 및 저장용으로 사용하는장치 |

| JP4129381B2 (ja) * | 2002-09-25 | 2008-08-06 | 株式会社ルネサステクノロジ | 不揮発性半導体記憶装置 |

| US7096313B1 (en) * | 2002-10-28 | 2006-08-22 | Sandisk Corporation | Tracking the least frequently erased blocks in non-volatile memory systems |

| US7171536B2 (en) | 2002-10-28 | 2007-01-30 | Sandisk Corporation | Unusable block management within a non-volatile memory system |

| KR101122511B1 (ko) | 2002-10-28 | 2012-03-15 | 쌘디스크 코포레이션 | 비휘발성 저장 시스템들에서 자동 웨어 레벨링 |

| US20050055479A1 (en) | 2002-11-21 | 2005-03-10 | Aviad Zer | Multi-module circuit card with inter-module direct memory access |

| US8037229B2 (en) | 2002-11-21 | 2011-10-11 | Sandisk Technologies Inc. | Combination non-volatile memory and input-output card with direct memory access |

| CN1717662B (zh) * | 2002-11-28 | 2010-04-28 | 株式会社瑞萨科技 | 存储器模块、存储器系统和信息仪器 |

| US7225357B2 (en) * | 2003-01-21 | 2007-05-29 | Zentek Technology Japan, Inc. | SDIO card development system |

| US7069370B2 (en) | 2003-01-31 | 2006-06-27 | Toshiba Corporation | USB memory storage apparatus with integrated circuit in a connector |

| JP4550439B2 (ja) | 2003-02-28 | 2010-09-22 | 東芝メモリシステムズ株式会社 | Ecc制御装置 |

| JP2004355163A (ja) * | 2003-05-28 | 2004-12-16 | Renesas Technology Corp | データ処理装置および電子機器 |

| US6988175B2 (en) | 2003-06-30 | 2006-01-17 | M-Systems Flash Disk Pioneers Ltd. | Flash memory management method that is resistant to data corruption by power loss |

| KR100560767B1 (ko) | 2003-09-02 | 2006-03-13 | 삼성전자주식회사 | 탈착 가능한 저장 장치를 포함하는 시스템 및 그것의 제어방법 |

| US7012835B2 (en) | 2003-10-03 | 2006-03-14 | Sandisk Corporation | Flash memory data correction and scrub techniques |

| TWI226643B (en) | 2003-10-31 | 2005-01-11 | C One Technology Corp | Simulated SmartMedia/xD-Picture memory card using any nonvolatile memory |

| US7594135B2 (en) | 2003-12-31 | 2009-09-22 | Sandisk Corporation | Flash memory system startup operation |

| US7350044B2 (en) | 2004-01-30 | 2008-03-25 | Micron Technology, Inc. | Data move method and apparatus |

| US7136973B2 (en) | 2004-02-04 | 2006-11-14 | Sandisk Corporation | Dual media storage device |

| US8019928B2 (en) | 2004-02-15 | 2011-09-13 | Sandisk Il Ltd. | Method of managing a multi-bit-cell flash memory |

| JP4398750B2 (ja) * | 2004-02-17 | 2010-01-13 | 株式会社東芝 | Nand型フラッシュメモリ |

| US7177977B2 (en) | 2004-03-19 | 2007-02-13 | Sandisk Corporation | Operating non-volatile memory without read disturb limitations |

| KR100648243B1 (ko) | 2004-03-19 | 2006-11-24 | 삼성전자주식회사 | 낸드 플래시 메모리를 사용하는 메모리 카드 |

| JP4357331B2 (ja) * | 2004-03-24 | 2009-11-04 | 東芝メモリシステムズ株式会社 | マイクロプロセッサブートアップ制御装置、及び情報処理システム |

| US7406572B1 (en) | 2004-03-26 | 2008-07-29 | Cypress Semiconductor Corp. | Universal memory circuit architecture supporting multiple memory interface options |

| US7057939B2 (en) | 2004-04-23 | 2006-06-06 | Sandisk Corporation | Non-volatile memory and control with improved partial page program capability |

| US7139199B2 (en) | 2004-06-28 | 2006-11-21 | Intel Corporation | Flash memory file system with transacted operations |

| JP2008511929A (ja) * | 2004-08-30 | 2008-04-17 | シリコン ストレージ テクノロジー、 インク. | 携帯電話の不揮発性メモリを管理するシステムおよび方法 |

| JP4406339B2 (ja) * | 2004-09-21 | 2010-01-27 | 株式会社東芝 | コントローラ、メモリカード及びその制御方法 |

| US7149119B2 (en) | 2004-09-30 | 2006-12-12 | Matrix Semiconductor, Inc. | System and method of controlling a three-dimensional memory |

| JP4828816B2 (ja) * | 2004-10-25 | 2011-11-30 | 株式会社東芝 | メモリカード、半導体装置、及びメモリカードの制御方法 |

| US7149111B2 (en) * | 2004-12-17 | 2006-12-12 | Msystems Ltd. | Method of handling limitations on the order of writing to a non-volatile memory |

| US20060239450A1 (en) | 2004-12-21 | 2006-10-26 | Michael Holtzman | In stream data encryption / decryption and error correction method |

| US6980471B1 (en) | 2004-12-23 | 2005-12-27 | Sandisk Corporation | Substrate electron injection techniques for programming non-volatile charge storage memory cells |

| US7177191B2 (en) | 2004-12-30 | 2007-02-13 | Sandisk 3D Llc | Integrated circuit including memory array incorporating multiple types of NAND string structures |

| US7187583B2 (en) | 2005-01-25 | 2007-03-06 | Phison Electronics Corp. | Method for reducing data error when flash memory storage device using copy back command |

| JP4198124B2 (ja) * | 2005-04-27 | 2008-12-17 | 株式会社ハギワラシスコム | 1チップ型半導体記憶デバイス |

| JP2006323739A (ja) * | 2005-05-20 | 2006-11-30 | Renesas Technology Corp | メモリモジュール、メモリシステム、及び情報機器 |

| US7362604B2 (en) | 2005-07-11 | 2008-04-22 | Sandisk 3D Llc | Apparatus and method for programming an array of nonvolatile memory cells including switchable resistor memory elements |

| US7345907B2 (en) | 2005-07-11 | 2008-03-18 | Sandisk 3D Llc | Apparatus and method for reading an array of nonvolatile memory cells including switchable resistor memory elements |

| US7362611B2 (en) | 2005-08-30 | 2008-04-22 | Micron Technology, Inc. | Non-volatile memory copy back |

| US7218552B1 (en) | 2005-09-09 | 2007-05-15 | Sandisk Corporation | Last-first mode and method for programming of non-volatile memory with reduced program disturb |

| US7170788B1 (en) | 2005-09-09 | 2007-01-30 | Sandisk Corporation | Last-first mode and apparatus for programming of non-volatile memory with reduced program disturb |

| US7631245B2 (en) | 2005-09-26 | 2009-12-08 | Sandisk Il Ltd. | NAND flash memory controller exporting a NAND interface |

| US7640424B2 (en) | 2005-10-13 | 2009-12-29 | Sandisk Corporation | Initialization of flash storage via an embedded controller |

| US7379330B2 (en) | 2005-11-08 | 2008-05-27 | Sandisk Corporation | Retargetable memory cell redundancy methods |

| US7262994B2 (en) | 2005-12-06 | 2007-08-28 | Sandisk Corporation | System for reducing read disturb for non-volatile storage |

| US7349258B2 (en) | 2005-12-06 | 2008-03-25 | Sandisk Corporation | Reducing read disturb for non-volatile storage |

| US7355888B2 (en) | 2005-12-19 | 2008-04-08 | Sandisk Corporation | Apparatus for programming non-volatile memory with reduced program disturb using modified pass voltages |

| US7355889B2 (en) | 2005-12-19 | 2008-04-08 | Sandisk Corporation | Method for programming non-volatile memory with reduced program disturb using modified pass voltages |

| KR20070076849A (ko) | 2006-01-20 | 2007-07-25 | 삼성전자주식회사 | 메모리 카드의 카피백 동작을 수행하는 장치 및 방법 |

| US7852690B2 (en) | 2006-05-15 | 2010-12-14 | Apple Inc. | Multi-chip package for a flash memory |

| US20080046641A1 (en) | 2006-08-21 | 2008-02-21 | Sandisk Il Ltd. | NAND flash memory controller exporting a logical sector-based interface |

| US20080046630A1 (en) | 2006-08-21 | 2008-02-21 | Sandisk Il Ltd. | NAND flash memory controller exporting a logical sector-based interface |

| US8127200B2 (en) | 2006-12-24 | 2012-02-28 | Sandisk Il Ltd. | Flash memory device and system with randomizing for suppressing errors |

| US7865473B2 (en) | 2007-04-02 | 2011-01-04 | International Business Machines Corporation | Generating and indicating incremental backup copies from virtual copies of a data set |

-

2006

- 2006-01-06 US US11/326,336 patent/US7631245B2/en active Active

- 2006-09-20 JP JP2008531880A patent/JP2009510560A/ja active Pending

- 2006-09-20 CN CN2006800356310A patent/CN101366182B/zh active Active

- 2006-09-20 WO PCT/IL2006/001101 patent/WO2007034481A2/en active Application Filing

- 2006-09-20 KR KR1020087007225A patent/KR20080050433A/ko not_active Application Discontinuation

- 2006-09-20 EP EP06796108A patent/EP1929483A4/en not_active Withdrawn

- 2006-09-20 KR KR1020097027656A patent/KR20100021497A/ko not_active Application Discontinuation

- 2006-09-20 EP EP09009022A patent/EP2110746A1/en not_active Ceased

-

2009

- 2009-11-02 US US12/610,868 patent/US7886212B2/en active Active

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP1146428A1 (en) * | 2000-04-13 | 2001-10-17 | Yao, Li-ho | Multi-interface memory card and adapter module for the same |

| CN1649032A (zh) * | 2004-01-29 | 2005-08-03 | 群联电子股份有限公司 | 具防写功能的微型存储装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US7886212B2 (en) | 2011-02-08 |

| WO2007034481A3 (en) | 2007-09-07 |

| CN101366182A (zh) | 2009-02-11 |

| JP2009510560A (ja) | 2009-03-12 |

| KR20080050433A (ko) | 2008-06-05 |

| KR20100021497A (ko) | 2010-02-24 |

| US20100049909A1 (en) | 2010-02-25 |

| WO2007034481A2 (en) | 2007-03-29 |

| EP2110746A1 (en) | 2009-10-21 |

| EP1929483A2 (en) | 2008-06-11 |

| US7631245B2 (en) | 2009-12-08 |

| US20070074093A1 (en) | 2007-03-29 |

| EP1929483A4 (en) | 2009-06-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN101366182B (zh) | 输出nand接口的nand闪存控制器 | |

| US10861509B2 (en) | Asynchronous/synchronous interface | |

| US7392343B2 (en) | Memory card having a storage cell and method of controlling the same | |

| US8335123B2 (en) | Power management of memory systems | |

| CN101202106B (zh) | 非易失性存储系统及其相应的编程方法 | |

| CN102239524B (zh) | 逻辑单元操作 | |

| US8762703B2 (en) | Boot partitions in memory devices and systems | |

| US7916557B2 (en) | NAND interface | |

| US9208901B2 (en) | Memory buffer having accessible information after a program-fail | |

| US7970982B2 (en) | Memory card and memory system having the same | |

| CN109841253B (zh) | 半导体存储装置及其复位方法 | |

| CN102591738B (zh) | 数据管理方法、存储器控制器与嵌入式存储器储存装置 | |

| CN110209433B (zh) | 一种识别不同型号集中器的方法 | |

| US10978133B2 (en) | Memory device and memory system comprising the same | |

| US10719270B2 (en) | Raising usage rates of memory blocks with a free MSB page list | |

| CN114816234A (zh) | 存取管理的方法、存储器装置、电子装置以及控制器 | |

| CN1496066A (zh) | 对信号线上的通信进行控制的系统和方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| ASS | Succession or assignment of patent right |

Owner name: INNOVATIVE STORAGE SYSTEMS, INC. Free format text: FORMER OWNER: MILSYS LTD. Effective date: 20150429 |

|

| C41 | Transfer of patent application or patent right or utility model | ||

| TR01 | Transfer of patent right |

Effective date of registration: 20150429 Address after: American California Patentee after: Creative Memory Systems Inc Address before: Israel Kfar Saba Patentee before: Milsys Ltd. |