CN101853809B - 半导体元件及其制造方法和液晶显示器及其制造方法 - Google Patents

半导体元件及其制造方法和液晶显示器及其制造方法 Download PDFInfo

- Publication number

- CN101853809B CN101853809B CN201010167923.8A CN201010167923A CN101853809B CN 101853809 B CN101853809 B CN 101853809B CN 201010167923 A CN201010167923 A CN 201010167923A CN 101853809 B CN101853809 B CN 101853809B

- Authority

- CN

- China

- Prior art keywords

- film

- layer

- semiconductor film

- dielectric film

- semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 181

- 238000004519 manufacturing process Methods 0.000 title claims description 41

- 239000004973 liquid crystal related substance Substances 0.000 title description 28

- 238000000034 method Methods 0.000 claims abstract description 196

- 239000000463 material Substances 0.000 claims abstract description 55

- 238000007599 discharging Methods 0.000 claims abstract description 19

- 239000000758 substrate Substances 0.000 claims description 87

- 239000002131 composite material Substances 0.000 claims description 72

- 239000004020 conductor Substances 0.000 claims description 61

- 239000012535 impurity Substances 0.000 claims description 34

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 34

- 239000010936 titanium Substances 0.000 claims description 32

- 230000015572 biosynthetic process Effects 0.000 claims description 31

- 229910052719 titanium Inorganic materials 0.000 claims description 31

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 claims description 30

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 claims description 25

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 claims description 24

- 239000004642 Polyimide Substances 0.000 claims description 17

- 229920001721 polyimide Polymers 0.000 claims description 17

- 239000000377 silicon dioxide Substances 0.000 claims description 17

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 claims description 14

- 229920002120 photoresistant polymer Polymers 0.000 claims description 14

- SMZOUWXMTYCWNB-UHFFFAOYSA-N 2-(2-methoxy-5-methylphenyl)ethanamine Chemical compound COC1=CC=C(C)C=C1CCN SMZOUWXMTYCWNB-UHFFFAOYSA-N 0.000 claims description 12

- NIXOWILDQLNWCW-UHFFFAOYSA-N 2-Propenoic acid Natural products OC(=O)C=C NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 claims description 12

- 239000011248 coating agent Substances 0.000 claims description 10

- 238000000576 coating method Methods 0.000 claims description 10

- 239000002245 particle Substances 0.000 claims description 10

- 230000004888 barrier function Effects 0.000 claims description 9

- 238000009832 plasma treatment Methods 0.000 claims description 9

- 238000010276 construction Methods 0.000 claims description 8

- 239000001257 hydrogen Substances 0.000 claims description 7

- 229910052739 hydrogen Inorganic materials 0.000 claims description 7

- 125000004435 hydrogen atom Chemical group [H]* 0.000 claims description 6

- 125000000217 alkyl group Chemical group 0.000 claims description 5

- 125000003118 aryl group Chemical group 0.000 claims description 5

- 125000001424 substituent group Chemical group 0.000 claims description 5

- 238000009713 electroplating Methods 0.000 claims description 4

- 229910052725 zinc Inorganic materials 0.000 claims description 3

- 239000011701 zinc Substances 0.000 claims description 3

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 claims description 2

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 claims description 2

- 229910001195 gallium oxide Inorganic materials 0.000 claims description 2

- 150000002222 fluorine compounds Chemical group 0.000 claims 2

- 230000008569 process Effects 0.000 abstract description 59

- 229910052751 metal Inorganic materials 0.000 abstract description 13

- 239000002184 metal Substances 0.000 abstract description 13

- 239000010408 film Substances 0.000 description 313

- 239000010410 layer Substances 0.000 description 108

- 238000005530 etching Methods 0.000 description 36

- 239000007789 gas Substances 0.000 description 29

- 238000002347 injection Methods 0.000 description 19

- 239000007924 injection Substances 0.000 description 19

- 230000003647 oxidation Effects 0.000 description 19

- 238000007254 oxidation reaction Methods 0.000 description 19

- -1 siloxanes Chemical class 0.000 description 19

- 229910052581 Si3N4 Inorganic materials 0.000 description 18

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 18

- 230000014509 gene expression Effects 0.000 description 18

- 229910052710 silicon Inorganic materials 0.000 description 18

- 239000010703 silicon Substances 0.000 description 18

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 18

- 239000011347 resin Substances 0.000 description 17

- 229920005989 resin Polymers 0.000 description 17

- 239000010409 thin film Substances 0.000 description 16

- 239000010949 copper Substances 0.000 description 13

- 239000012212 insulator Substances 0.000 description 13

- 239000007788 liquid Substances 0.000 description 13

- 150000002894 organic compounds Chemical class 0.000 description 12

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 11

- 239000001301 oxygen Substances 0.000 description 11

- 229910052760 oxygen Inorganic materials 0.000 description 11

- 238000007781 pre-processing Methods 0.000 description 11

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 11

- 239000004372 Polyvinyl alcohol Substances 0.000 description 10

- 238000010586 diagram Methods 0.000 description 10

- 230000037230 mobility Effects 0.000 description 10

- 229920002451 polyvinyl alcohol Polymers 0.000 description 10

- 239000002904 solvent Substances 0.000 description 10

- 230000006870 function Effects 0.000 description 9

- 238000005401 electroluminescence Methods 0.000 description 8

- 239000011159 matrix material Substances 0.000 description 8

- 238000004544 sputter deposition Methods 0.000 description 8

- PNEYBMLMFCGWSK-UHFFFAOYSA-N Alumina Chemical compound [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 7

- 239000004952 Polyamide Substances 0.000 description 7

- 238000013461 design Methods 0.000 description 7

- 229920002647 polyamide Polymers 0.000 description 7

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 6

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 6

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 6

- 239000012298 atmosphere Substances 0.000 description 6

- 239000000460 chlorine Substances 0.000 description 6

- 229910052802 copper Inorganic materials 0.000 description 6

- 239000000203 mixture Substances 0.000 description 6

- 229910021332 silicide Inorganic materials 0.000 description 6

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 6

- 229910052709 silver Inorganic materials 0.000 description 6

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 5

- 229910018557 Si O Inorganic materials 0.000 description 5

- 229910052782 aluminium Inorganic materials 0.000 description 5

- 230000005540 biological transmission Effects 0.000 description 5

- 229910052799 carbon Inorganic materials 0.000 description 5

- 238000001035 drying Methods 0.000 description 5

- 230000000694 effects Effects 0.000 description 5

- 229910052738 indium Inorganic materials 0.000 description 5

- 239000002105 nanoparticle Substances 0.000 description 5

- 238000012545 processing Methods 0.000 description 5

- 239000002994 raw material Substances 0.000 description 5

- 230000027756 respiratory electron transport chain Effects 0.000 description 5

- 239000004332 silver Substances 0.000 description 5

- 125000006850 spacer group Chemical group 0.000 description 5

- 238000004528 spin coating Methods 0.000 description 5

- 239000011787 zinc oxide Substances 0.000 description 5

- WUPHOULIZUERAE-UHFFFAOYSA-N 3-(oxolan-2-yl)propanoic acid Chemical compound OC(=O)CCC1CCCO1 WUPHOULIZUERAE-UHFFFAOYSA-N 0.000 description 4

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 4

- KRHYYFGTRYWZRS-UHFFFAOYSA-M Fluoride anion Chemical compound [F-] KRHYYFGTRYWZRS-UHFFFAOYSA-M 0.000 description 4

- UQSXHKLRYXJYBZ-UHFFFAOYSA-N Iron oxide Chemical compound [Fe]=O UQSXHKLRYXJYBZ-UHFFFAOYSA-N 0.000 description 4

- 229910003902 SiCl 4 Inorganic materials 0.000 description 4

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 4

- MCMNRKCIXSYSNV-UHFFFAOYSA-N Zirconium dioxide Chemical compound O=[Zr]=O MCMNRKCIXSYSNV-UHFFFAOYSA-N 0.000 description 4

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 4

- 229910052796 boron Inorganic materials 0.000 description 4

- 229910052980 cadmium sulfide Inorganic materials 0.000 description 4

- 239000013078 crystal Substances 0.000 description 4

- 210000002858 crystal cell Anatomy 0.000 description 4

- 230000009977 dual effect Effects 0.000 description 4

- 238000011049 filling Methods 0.000 description 4

- 230000004907 flux Effects 0.000 description 4

- 239000010931 gold Substances 0.000 description 4

- 238000003384 imaging method Methods 0.000 description 4

- MRNHPUHPBOKKQT-UHFFFAOYSA-N indium;tin;hydrate Chemical compound O.[In].[Sn] MRNHPUHPBOKKQT-UHFFFAOYSA-N 0.000 description 4

- 230000003993 interaction Effects 0.000 description 4

- XEEYBQQBJWHFJM-UHFFFAOYSA-N iron Substances [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 4

- 239000012528 membrane Substances 0.000 description 4

- 239000003960 organic solvent Substances 0.000 description 4

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 4

- ZWEHNKRNPOVVGH-UHFFFAOYSA-N 2-Butanone Chemical compound CCC(C)=O ZWEHNKRNPOVVGH-UHFFFAOYSA-N 0.000 description 3

- XEKOWRVHYACXOJ-UHFFFAOYSA-N Ethyl acetate Chemical compound CCOC(C)=O XEKOWRVHYACXOJ-UHFFFAOYSA-N 0.000 description 3

- KFZMGEQAYNKOFK-UHFFFAOYSA-N Isopropanol Chemical compound CC(C)O KFZMGEQAYNKOFK-UHFFFAOYSA-N 0.000 description 3

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 3

- ZLMJMSJWJFRBEC-UHFFFAOYSA-N Potassium Chemical compound [K] ZLMJMSJWJFRBEC-UHFFFAOYSA-N 0.000 description 3

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 3

- 239000000853 adhesive Substances 0.000 description 3

- 230000001070 adhesive effect Effects 0.000 description 3

- 239000004411 aluminium Substances 0.000 description 3

- 238000004380 ashing Methods 0.000 description 3

- 125000004429 atom Chemical group 0.000 description 3

- 230000008901 benefit Effects 0.000 description 3

- 230000000903 blocking effect Effects 0.000 description 3

- 238000005229 chemical vapour deposition Methods 0.000 description 3

- 230000008878 coupling Effects 0.000 description 3

- 238000010168 coupling process Methods 0.000 description 3

- 238000005859 coupling reaction Methods 0.000 description 3

- 239000002270 dispersing agent Substances 0.000 description 3

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 3

- 229910052737 gold Inorganic materials 0.000 description 3

- 150000002484 inorganic compounds Chemical class 0.000 description 3

- 229910010272 inorganic material Inorganic materials 0.000 description 3

- 238000003475 lamination Methods 0.000 description 3

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 3

- 239000003595 mist Substances 0.000 description 3

- 238000002156 mixing Methods 0.000 description 3

- 229910052757 nitrogen Inorganic materials 0.000 description 3

- 230000001699 photocatalysis Effects 0.000 description 3

- 238000007146 photocatalysis Methods 0.000 description 3

- 238000001020 plasma etching Methods 0.000 description 3

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 3

- 238000005498 polishing Methods 0.000 description 3

- 229910052700 potassium Inorganic materials 0.000 description 3

- 239000011591 potassium Substances 0.000 description 3

- 239000000243 solution Substances 0.000 description 3

- 229910052718 tin Inorganic materials 0.000 description 3

- 238000005406 washing Methods 0.000 description 3

- HYZJCKYKOHLVJF-UHFFFAOYSA-N 1H-benzimidazole Chemical compound C1=CC=C2NC=NC2=C1 HYZJCKYKOHLVJF-UHFFFAOYSA-N 0.000 description 2

- CSCPPACGZOOCGX-UHFFFAOYSA-N Acetone Chemical compound CC(C)=O CSCPPACGZOOCGX-UHFFFAOYSA-N 0.000 description 2

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 2

- LFQSCWFLJHTTHZ-UHFFFAOYSA-N Ethanol Chemical compound CCO LFQSCWFLJHTTHZ-UHFFFAOYSA-N 0.000 description 2

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 2

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 2

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 2

- 229910002367 SrTiO Inorganic materials 0.000 description 2

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 2

- 229910052786 argon Inorganic materials 0.000 description 2

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 2

- AQCDIIAORKRFCD-UHFFFAOYSA-N cadmium selenide Chemical compound [Cd]=[Se] AQCDIIAORKRFCD-UHFFFAOYSA-N 0.000 description 2

- 229910052791 calcium Inorganic materials 0.000 description 2

- 239000011575 calcium Substances 0.000 description 2

- 239000003795 chemical substances by application Substances 0.000 description 2

- 229910052801 chlorine Inorganic materials 0.000 description 2

- 239000011651 chromium Substances 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 229910052733 gallium Inorganic materials 0.000 description 2

- 229910052732 germanium Inorganic materials 0.000 description 2

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 238000010438 heat treatment Methods 0.000 description 2

- 229910052734 helium Inorganic materials 0.000 description 2

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 2

- 229910003437 indium oxide Inorganic materials 0.000 description 2

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 2

- 239000011810 insulating material Substances 0.000 description 2

- 238000009413 insulation Methods 0.000 description 2

- 239000011229 interlayer Substances 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 229910052758 niobium Inorganic materials 0.000 description 2

- 239000010955 niobium Substances 0.000 description 2

- URLJKFSTXLNXLG-UHFFFAOYSA-N niobium(5+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Nb+5].[Nb+5] URLJKFSTXLNXLG-UHFFFAOYSA-N 0.000 description 2

- 238000007747 plating Methods 0.000 description 2

- 238000007639 printing Methods 0.000 description 2

- 239000010948 rhodium Substances 0.000 description 2

- 239000000565 sealant Substances 0.000 description 2

- 229910052814 silicon oxide Inorganic materials 0.000 description 2

- 238000005507 spraying Methods 0.000 description 2

- 230000006641 stabilisation Effects 0.000 description 2

- 238000011105 stabilization Methods 0.000 description 2

- 238000003860 storage Methods 0.000 description 2

- 229910052712 strontium Inorganic materials 0.000 description 2

- CIOAGBVUUVVLOB-UHFFFAOYSA-N strontium atom Chemical compound [Sr] CIOAGBVUUVVLOB-UHFFFAOYSA-N 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- ZNOKGRXACCSDPY-UHFFFAOYSA-N tungsten trioxide Chemical compound O=[W](=O)=O ZNOKGRXACCSDPY-UHFFFAOYSA-N 0.000 description 2

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 2

- 229910052726 zirconium Inorganic materials 0.000 description 2

- 229910017073 AlLi Inorganic materials 0.000 description 1

- 229910017083 AlN Inorganic materials 0.000 description 1

- PIGFYZPCRLYGLF-UHFFFAOYSA-N Aluminum nitride Chemical compound [Al]#N PIGFYZPCRLYGLF-UHFFFAOYSA-N 0.000 description 1

- DKPFZGUDAPQIHT-UHFFFAOYSA-N Butyl acetate Natural products CCCCOC(C)=O DKPFZGUDAPQIHT-UHFFFAOYSA-N 0.000 description 1

- OYPRJOBELJOOCE-UHFFFAOYSA-N Calcium Chemical compound [Ca] OYPRJOBELJOOCE-UHFFFAOYSA-N 0.000 description 1

- VEXZGXHMUGYJMC-UHFFFAOYSA-M Chloride anion Chemical compound [Cl-] VEXZGXHMUGYJMC-UHFFFAOYSA-M 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 1

- 241001232787 Epiphragma Species 0.000 description 1

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 1

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 1

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 1

- 229910001051 Magnalium Inorganic materials 0.000 description 1

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 1

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- 229910003251 Na K Inorganic materials 0.000 description 1

- XYFCBTPGUUZFHI-UHFFFAOYSA-N Phosphine Chemical compound P XYFCBTPGUUZFHI-UHFFFAOYSA-N 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 description 1

- 229910003087 TiOx Inorganic materials 0.000 description 1

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 1

- JFBZPFYRPYOZCQ-UHFFFAOYSA-N [Li].[Al] Chemical compound [Li].[Al] JFBZPFYRPYOZCQ-UHFFFAOYSA-N 0.000 description 1

- OWXLRKWPEIAGAT-UHFFFAOYSA-N [Mg].[Cu] Chemical compound [Mg].[Cu] OWXLRKWPEIAGAT-UHFFFAOYSA-N 0.000 description 1

- JHYLKGDXMUDNEO-UHFFFAOYSA-N [Mg].[In] Chemical compound [Mg].[In] JHYLKGDXMUDNEO-UHFFFAOYSA-N 0.000 description 1

- 125000003158 alcohol group Chemical group 0.000 description 1

- 150000001298 alcohols Chemical class 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 230000003667 anti-reflective effect Effects 0.000 description 1

- 229910052787 antimony Inorganic materials 0.000 description 1

- WATWJIUSRGPENY-UHFFFAOYSA-N antimony atom Chemical compound [Sb] WATWJIUSRGPENY-UHFFFAOYSA-N 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- 229910052790 beryllium Inorganic materials 0.000 description 1

- ATBAMAFKBVZNFJ-UHFFFAOYSA-N beryllium atom Chemical compound [Be] ATBAMAFKBVZNFJ-UHFFFAOYSA-N 0.000 description 1

- 238000001574 biopsy Methods 0.000 description 1

- 229910052793 cadmium Inorganic materials 0.000 description 1

- BDOSMKKIYDKNTQ-UHFFFAOYSA-N cadmium atom Chemical compound [Cd] BDOSMKKIYDKNTQ-UHFFFAOYSA-N 0.000 description 1

- 239000012159 carrier gas Substances 0.000 description 1

- 239000003054 catalyst Substances 0.000 description 1

- 210000004027 cell Anatomy 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- SLLGVCUQYRMELA-UHFFFAOYSA-N chlorosilicon Chemical compound Cl[Si] SLLGVCUQYRMELA-UHFFFAOYSA-N 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 238000005253 cladding Methods 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 238000005336 cracking Methods 0.000 description 1

- 238000002425 crystallisation Methods 0.000 description 1

- 230000008025 crystallization Effects 0.000 description 1

- 230000001351 cycling effect Effects 0.000 description 1

- 238000000354 decomposition reaction Methods 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 238000010790 dilution Methods 0.000 description 1

- 239000012895 dilution Substances 0.000 description 1

- 229910001882 dioxygen Inorganic materials 0.000 description 1

- PZPGRFITIJYNEJ-UHFFFAOYSA-N disilane Chemical compound [SiH3][SiH3] PZPGRFITIJYNEJ-UHFFFAOYSA-N 0.000 description 1

- 238000004090 dissolution Methods 0.000 description 1

- 239000000428 dust Substances 0.000 description 1

- 238000005868 electrolysis reaction Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 150000002148 esters Chemical class 0.000 description 1

- 238000002474 experimental method Methods 0.000 description 1

- 239000004744 fabric Substances 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- XPBBUZJBQWWFFJ-UHFFFAOYSA-N fluorosilane Chemical compound [SiH3]F XPBBUZJBQWWFFJ-UHFFFAOYSA-N 0.000 description 1

- 238000002309 gasification Methods 0.000 description 1

- SCCCLDWUZODEKG-UHFFFAOYSA-N germanide Chemical compound [GeH3-] SCCCLDWUZODEKG-UHFFFAOYSA-N 0.000 description 1

- 229910021397 glassy carbon Inorganic materials 0.000 description 1

- 229910002804 graphite Inorganic materials 0.000 description 1

- 239000010439 graphite Substances 0.000 description 1

- 238000009499 grossing Methods 0.000 description 1

- 230000005283 ground state Effects 0.000 description 1

- 239000001307 helium Substances 0.000 description 1

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 1

- FUZZWVXGSFPDMH-UHFFFAOYSA-M hexanoate Chemical compound CCCCCC([O-])=O FUZZWVXGSFPDMH-UHFFFAOYSA-M 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 229910052741 iridium Inorganic materials 0.000 description 1

- GKOZUEZYRPOHIO-UHFFFAOYSA-N iridium atom Chemical compound [Ir] GKOZUEZYRPOHIO-UHFFFAOYSA-N 0.000 description 1

- 229910052742 iron Inorganic materials 0.000 description 1

- 229910052743 krypton Inorganic materials 0.000 description 1

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 description 1

- 238000005499 laser crystallization Methods 0.000 description 1

- 229910052744 lithium Inorganic materials 0.000 description 1

- 210000004072 lung Anatomy 0.000 description 1

- 229910052749 magnesium Inorganic materials 0.000 description 1

- 239000011777 magnesium Substances 0.000 description 1

- SJCKRGFTWFGHGZ-UHFFFAOYSA-N magnesium silver Chemical compound [Mg].[Ag] SJCKRGFTWFGHGZ-UHFFFAOYSA-N 0.000 description 1

- WPBNNNQJVZRUHP-UHFFFAOYSA-L manganese(2+);methyl n-[[2-(methoxycarbonylcarbamothioylamino)phenyl]carbamothioyl]carbamate;n-[2-(sulfidocarbothioylamino)ethyl]carbamodithioate Chemical compound [Mn+2].[S-]C(=S)NCCNC([S-])=S.COC(=O)NC(=S)NC1=CC=CC=C1NC(=S)NC(=O)OC WPBNNNQJVZRUHP-UHFFFAOYSA-L 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- 229910052754 neon Inorganic materials 0.000 description 1

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 1

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 1

- QJGQUHMNIGDVPM-UHFFFAOYSA-N nitrogen group Chemical group [N] QJGQUHMNIGDVPM-UHFFFAOYSA-N 0.000 description 1

- AHLBNYSZXLDEJQ-FWEHEUNISA-N orlistat Chemical compound CCCCCCCCCCC[C@H](OC(=O)[C@H](CC(C)C)NC=O)C[C@@H]1OC(=O)[C@H]1CCCCCC AHLBNYSZXLDEJQ-FWEHEUNISA-N 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- 150000002927 oxygen compounds Chemical class 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 238000001259 photo etching Methods 0.000 description 1

- 229920003023 plastic Polymers 0.000 description 1

- 239000004033 plastic Substances 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 230000010287 polarization Effects 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 238000012958 reprocessing Methods 0.000 description 1

- 229910052702 rhenium Inorganic materials 0.000 description 1

- WUAPFZMCVAUBPE-UHFFFAOYSA-N rhenium atom Chemical compound [Re] WUAPFZMCVAUBPE-UHFFFAOYSA-N 0.000 description 1

- 229910052703 rhodium Inorganic materials 0.000 description 1

- MHOVAHRLVXNVSD-UHFFFAOYSA-N rhodium atom Chemical compound [Rh] MHOVAHRLVXNVSD-UHFFFAOYSA-N 0.000 description 1

- 229910052707 ruthenium Inorganic materials 0.000 description 1

- 229910052706 scandium Inorganic materials 0.000 description 1

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- VSZWPYCFIRKVQL-UHFFFAOYSA-N selanylidenegallium;selenium Chemical compound [Se].[Se]=[Ga].[Se]=[Ga] VSZWPYCFIRKVQL-UHFFFAOYSA-N 0.000 description 1

- ABTOQLMXBSRXSM-UHFFFAOYSA-N silicon tetrafluoride Chemical compound F[Si](F)(F)F ABTOQLMXBSRXSM-UHFFFAOYSA-N 0.000 description 1

- 239000002002 slurry Substances 0.000 description 1

- 229910052708 sodium Inorganic materials 0.000 description 1

- 239000011734 sodium Substances 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 1

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 1

- 229910052714 tellurium Inorganic materials 0.000 description 1

- PORWMNRCUJJQNO-UHFFFAOYSA-N tellurium atom Chemical compound [Te] PORWMNRCUJJQNO-UHFFFAOYSA-N 0.000 description 1

- 229920001187 thermosetting polymer Polymers 0.000 description 1

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 1

- 229910001887 tin oxide Inorganic materials 0.000 description 1

- HLLICFJUWSZHRJ-UHFFFAOYSA-N tioxidazole Chemical compound CCCOC1=CC=C2N=C(NC(=O)OC)SC2=C1 HLLICFJUWSZHRJ-UHFFFAOYSA-N 0.000 description 1

- 150000003608 titanium Chemical class 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- 238000009834 vaporization Methods 0.000 description 1

- 230000008016 vaporization Effects 0.000 description 1

- 230000000007 visual effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66742—Thin film unipolar transistors

- H01L29/6675—Amorphous silicon or polysilicon transistors

- H01L29/66765—Lateral single gate single channel transistors with inverted structure, i.e. the channel layer is formed after the gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/283—Deposition of conductive or insulating materials for electrodes conducting electric current

- H01L21/288—Deposition of conductive or insulating materials for electrodes conducting electric current from a liquid, e.g. electrolytic deposition

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/124—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or layout of the wiring layers specially adapted to the circuit arrangement, e.g. scanning lines in LCD pixel circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/127—Multistep manufacturing methods with a particular formation, treatment or patterning of the active layer specially adapted to the circuit arrangement

- H01L27/1274—Multistep manufacturing methods with a particular formation, treatment or patterning of the active layer specially adapted to the circuit arrangement using crystallisation of amorphous semiconductor or recrystallisation of crystalline semiconductor

- H01L27/1285—Multistep manufacturing methods with a particular formation, treatment or patterning of the active layer specially adapted to the circuit arrangement using crystallisation of amorphous semiconductor or recrystallisation of crystalline semiconductor using control of the annealing or irradiation parameters, e.g. using different scanning direction or intensity for different transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/1292—Multistep manufacturing methods using liquid deposition, e.g. printing

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/45—Ohmic electrodes

- H01L29/456—Ohmic electrodes on silicon

- H01L29/458—Ohmic electrodes on silicon for thin film silicon, e.g. source or drain electrode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/4908—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET for thin film semiconductor, e.g. gate of TFT

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78603—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the insulating substrate or support

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42384—Gate electrodes for field effect devices for field-effect transistors with insulated gate for thin film field effect transistors, e.g. characterised by the thickness or the shape of the insulator or the dimensions, the shape or the lay-out of the conductor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78696—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the structure of the channel, e.g. multichannel, transverse or longitudinal shape, length or width, doping structure, or the overlap or alignment between the channel and the gate, the source or the drain, or the contacting structure of the channel

Abstract

在常规TFT制成反向交错式的情况下,形成岛形半导体区域时需要通过曝光、显影和液滴释放来形成光刻胶掩模。这导致了处理次数和材料数量的增加。根据本发明,由于在形成源极区和漏极区之后,用作沟道区的部分被用作沟道保护膜的绝缘膜所覆盖形成岛形半导体膜,可以简化工艺,并且这样可以只利用金属掩模而不用光刻胶掩模来制造半导体元件。

Description

本申请是申请日为2004年11月5日,申请号为200480040428.3,国际申请号为PCT/JP2004/016797,发明名称为“半导体元件及其制造方法和液晶显示器及其制造方法”的专利申请的分案申请。

技术领域

本发明涉及一种采用以喷墨法为代表的液滴释放技术制成的半导体元件,以及其制造方法。更具体来说,本发明涉及一种用于以液晶显示器或电致发光显示器为代表的显示器中的半导体元件,以及其制造方法。

背景技术

在制造半导体元件时,人们认识到可以利用液滴释放装置来形成薄膜或布线图案,它们分别用于半导体元件中,以降低设备成本并简化生产过程。

在此情况下,各种布线如用于形成半导体元件的门电极、扫描线、信号线、和像素电极根据该工序制成,即,将导电材料溶解或分散在溶剂中而形成的复合材料通过液滴释放装置的喷嘴释放到衬底或薄膜上从而直接绘制出这样的各种布线(参见例如公开号为No.2003-126760的日本专利申请)。

为了制造用于以有源矩阵液晶显示器(LCD)或有源矩阵电致发光显示器为代表的显示器中的半导体元件,如薄膜晶体管(TFT),需要建立一种结构和方法,其最适用于液滴释放法,并且不同于由重复进行成膜过程、布图过程、和蚀刻过程而制成的TFT。随着TFT衬底尺寸的增加,例如,大于1×1m或其两或三倍大的衬底,需要简化由液滴释放法制造TFT的结构和方法。

特别是,在上述TFT呈反向交错式(下门极式)时,典型的有沟道保护式或沟道蚀刻式,则半导体膜和含有n型杂质的半导体膜遍布形成于衬底之上;并利用形成岛形半导体区域的光刻胶掩模对所形成的半导体膜进行蚀刻;然后,用金属掩模或类似物将形成的含有n型杂质的半导体膜划分成源极区和漏极区。因此,在形成岛形半导体区域时需要通过曝光、显影、和液滴释放来形成光刻胶掩模。这导致处理次数和材料种类数增加。

鉴于上述原因,本发明的目的在于提供一种制造半导体元件的方法,该元件具有合适的状态能够通过液滴释放有效地形成。根据本发明,可以高产量地实现在各种尺寸的衬底上以高通量制造高稳定性的半导体元件,并减少生产时间。

以下是本发明解决上述问题的各方面。

本发明的一个方面提供了一种制造半导体元件的方法,包括步骤:通过在衬底上释放含有第一导电材料的复合材料而形成门电极层;在门电极层上形成门极绝缘膜;在门极绝缘膜上形成半导体膜;在半导体膜上形成含单一导电类型杂质元素的半导体膜;通过在含单一导电性类型杂质元素的半导体膜上释放含有第二导电材料的复合材料而形成源极区和漏极区;在半导体膜中用作沟道区的部分上形成绝缘膜;以及利用源电极、漏电极、和绝缘膜作为掩模通过去除半导体膜而形成岛形半导体膜。

也就是说,通过液滴释放在衬底上形成门电极层;通过薄膜成型方法如CVD或溅射法重叠形成门极绝缘膜、半导体膜、含单一导电性类型杂质元素的半导体膜(下文中称为单一导电性半导体膜);并通过液滴释放形成源极和漏极。然后,通过蚀刻等方法去除曝光的单一导电性半导体膜以形成源极区和漏极区。再然后,将能够用液滴释放等方法形成的绝缘膜形成于其上以覆盖并防止用作半导体膜沟道区的部分移动。此外,该绝缘膜起着沟道保护膜的作用。利用源电极、漏电极、和绝缘膜作为掩模通过蚀刻等方法去除曝光的半导体膜而形成岛形半导体膜。通过上述过程,可得到外观上类似于沟道保护形式的半导体元件。而且,利用液晶元件、有机电致发光元件等提供发光元件可获得预期的液晶显示器或发光显示器,其通过像素电极与源电极或漏电极连接而形成。

本发明的另一个方面是,在向衬底上释放含第一导电材料的复合材料之前预处理衬底中至少具有门电极层的部分。预处理过程包括,形成含钛、氧化钛或类似物的层;由具有硅(Si)氧(O)键合形成骨架并至少包括氢取代基,或至少一种选自氟化物、烷基、和芳烃基取代基的物质形成膜;等离子处理等等。等离子处理过程优选在大气压下进行。

本发明还有另一个方面是,形成源极区和漏极区;通过CVD或溅射法在源极区和漏极区形成第一绝缘膜;在第一绝缘膜上和半导体膜中用作沟道区的部分上形成第二绝缘膜;以及形成起沟道保护膜作用的绝缘膜以具有两层结构。第二绝缘膜不仅起到沟道保护膜的作用,还起着掩模的作用以便去除衬底上通过CVD等方法遍布形成的第一保护膜。作为第一绝缘膜,可采用含硅的绝缘膜,优选氮化硅膜。作为第二绝缘膜,可以使用任何绝缘膜,只要其能够通过液滴释放法选择性地形成。优选地,可采用由具有硅(Si)氧(O)键合形成骨架并至少包括氢取代基,或至少一种选自氟化物、烷基、和芳烃基取代基的物质形成的膜作为第二绝缘膜。绝缘膜不限于两层结构;该膜可具有三层或多层结构。

具有硅氧键合形成骨架并至少包括氢取代基,或至少一种选自氟化物、烷基、和芳烃基取代基的物质被称为基于硅氧烷的树脂。基于硅氧烷的树脂是一种耐热平面膜或耐热夹层(HRIL)膜。在下文中,术语“耐热平面膜”、“耐热夹层膜”、“耐热树脂”或“HRIL”包括基于硅氧烷的树脂。

作为形成导电材料或绝缘膜的液滴释放法,根据所要成膜的性质不仅可以采用喷墨法还可以采用胶版印刷或丝网印刷法。

根据本发明的半导体元件包括形成于衬底上的含钛或氧化钛的层;该层上形成的门电极层;门极电极层上形成的门极绝缘膜;门极绝缘膜上形成的半导体膜;半导体膜上形成的一对n型杂质区;插在这对n型杂质区之间并形成于半导体膜之上的绝缘膜;以及在这对n型杂质区上形成的导电层。

绝缘膜优选形成的厚度为100nm或以上以用作沟道保护膜。此外,绝缘膜可形成叠层结构。例如,下层可以由通过CVD或溅射法形成的膜如氮化硅膜制成;上层可由通过液滴释放法形成的膜,如耐热树脂如聚酰亚胺、丙烯酸、或硅氧烷制成。或者,两层都可由通过液滴释放法形成的膜制成。具有绝缘膜的半导体膜优选形成厚度在10nm或以上。

通常,源极区和漏极区可通过在形成岛形半导体膜之后蚀刻掉单一导电性半导体膜而形成。因此,在形成岛形半导体膜之前需要提供光刻胶掩模。反之,根据本发明,在源极区和漏极区形成之后,形成了起沟道保护膜作用的绝缘膜以覆盖用作沟道区的部分,然后形成岛形半导体膜。因此,不需要形成光刻胶掩模,这样可以简化程序。如上所述,本发明提供了形成半导体元件新手段,其结合了利用源电极和漏电极金属掩模形成源极区和漏极区以去除单一导电性半导体膜的方法,和用于形成沟道保护膜以防止沟道区移动的专用于沟道保护型的方法。根据本发明的上述实施方案,可以只利用源电极和漏电极金属掩模而不用任何光刻胶掩模来制造半导体元件。

在衬底上释放含第一导电材料的复合材料之前,可在衬底上至少具有门电极层的部分进行预处理过程,例如形成氧化钛(TiOx)等等。因此,可提高衬底和导电膜,如通过液滴释放法形成的门电极层之间的粘性。

通过形成厚度小于其它半导体膜的具绝缘膜的半导体膜,可将n型杂质区完全划分为源极区和漏极区。通过形成厚度在10nm或以上的具绝缘膜的半导体膜,可获得足够大的沟道迁移率。

通过形成厚度在100nm或以上的绝缘膜,可提高作为沟道保护膜的功能,并确保防止沟道区损坏。因此,可提供具有高迁移率的稳定半导体元件。此外,为了获得上述优点,形成包括第一绝缘膜和第二绝缘膜的两层结构或三层或以上叠层结构构成绝缘膜很有效。

发明内容

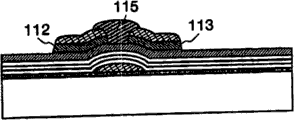

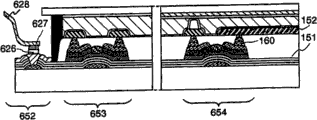

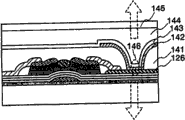

参考图1A至1D解释半导体元件和制造该半导体元件的方法。

将所谓的光催化物质如钛或氧化钛;或耐热树脂如聚酰亚胺、丙烯酸或硅氧烷形成于衬底100至少具有门电极层的部分上。这里,形成了氧化钛膜132。或者,可进行等离子处理。这种预处理使得提高衬底100和通过释放含导电材料的复合材料制成的导电膜之间的粘性。在形成氧化钛的情况下,可提高透光率。氧化钛可以直接形成,也可以在形成钛膜之后通过烘烤导电膜形成。除了钛或氧化钛之外,还可以形成光催化物质如钛酸锶(SrTiO3)、硒化镉(CdSe)、钽酸钾(KTaO3)、硫化镉(CdS)、氧化锆(ZrO2)、氧化铌(Nb2O5)、氧化锌(ZnO)、氧化铁(Fe2O3)、或氧化钨(WO3)。尽可能多地进行上述预处理过程可提高衬底和导电膜之间的粘性。

在对衬底100的表面进行预处理的情况下,在所述预处理部分上释放含第一导电材料的复合材料可形成门电极层102。这里,门电极层指由至少包括TFT门电极部分的单层或多层导电体所构成的层。通过释放所述复合材料形成门电极层;在100℃下干燥所述复合材料;然后在200到350℃的氮化或氧化气氛中烘烤所述复合材料15到30分钟。然而,不只限于上述条件。

作为第一导电材料,可以根据所述导电膜的功能采用各种材料。典型的实例有银(Ag)、铜(Cu)、金(Au)、镍(Ni)、铂(Pt)、铬(Cr)、锡(Sn)、钯(Pd)、铱(Ir)、铑(Rh)、钌(Ru)、铼(Re)、钨(W)、铝(Al)、钽(Ta)、铟(In)、碲(Te)、钼(Mo)、镉(Cd)、锌(Zn)、铁(Fe)、钛(Ti)、硅(Si)、锗(Ge)、锆(Zr)、钡(Ba)、硬铅、含锑氧化锡、氟化物掺杂的氧化锌、碳、石墨、玻璃碳、锂、铍、钠、镁、钾、钙、钪、锰、锆、镓、铌、钠钾合金、镁铜混合物、镁银混合物、镁铝混合物、镁铟混合物、铝氧化铝混合物、锂铝混合物等等,或者颗粒及其类似物如卤化银,或可分散纳米颗粒;或者用作导电膜的氧化铟锡(ITO)、氧化锌(ZnO)、有掺镓的氧化锌组成的氧化镓锌(GZO)、由氧化铟和2-20%氧化锌组成的氧化铟锡(IZO)、有机铟、氮化钛等等。

上述导电材料中可以含有硅(Si)或氧化硅(SiOx),尤其在上述材料用于形成透明导电膜的情况下。例如,可以使用由含硅氧化物的ITO构成的导电材料(下文中称为ITSO)。此外,通过层叠这些导电材料形成的层可以制成预期的导电膜。

用于液滴释放装置的喷嘴直径设定在0.1到50μm(优选0.6到26μm),释放量设定在0.00001到50pl(优选0.0001到10pl)。释放量随着喷嘴直径的增加而增加。物体和喷嘴释放口优选尽可能地彼此接近,以将液滴输送到预定的部位。物体和释放口之间的距离优选设定在大约0.1到2mm。

考虑到特定的电阻值,从释放口释放的复合材料优选通过将金、银或铜溶解或分散在溶剂中形成。更优选地,可使用低电阻的银或铜。在使用铜的情况下,优选同时提供隔膜作为防范杂质的措施。作为溶剂,可以使用酯类,如乙酸丁酯或乙酸乙酯;醇类如异丙醇或乙醇;有机溶剂如甲乙酮或丙酮;等等。在使用铜导线的情况下作为隔膜,可采用具有绝缘性或导电性的含氮物质,如氮化硅、氧氮化硅、氮化铝、氮化钛、或氮化钽(TaN)以便通过液滴释放形成隔膜。

用于液滴释放的复合材料优选粘度在300mPa·s或以下以防止干燥并以便从释放口中顺利地释放出。复合材料的粘度、表面张力等可以根据溶剂或应用来控制。例如,由ITO、ITSO、有机铟和有机锡溶解或分散在溶剂中形成的复合材料粘度在5到50mPa·s,由银溶解或分散在溶剂中形成的复合材料粘度在5到20mPa·s,由金溶解或分散在溶剂中形成的复合材料粘度在10到20mPa·s。

导电材料的颗粒直径优选尽可能小,优选在0.1μm或以下,以防止阻塞并制造高清图案,尽管这取决于各喷嘴的直径、图案形式等等。通过已知方法如电解法、喷雾法、或湿还原法形成的复合材料的粒径大约在0.5到10μm。在该复合材料通过汽化法形成的情况下,由分散剂保护的纳米分子具有大约7nm的微小直径。而且,表面被成膜剂覆盖的该纳米颗粒可以稳定地分散在溶剂中而不会在室温下聚集,这正表现出类似于液体的性质。因此,优选使用成膜剂。

或者,门电极层可通过释放含颗粒的复合材料形成,其中单一导电性类型的材料被另一种导电材料所覆盖。在这种情况下,两导电材料之间优选具有缓冲层。由Ag覆盖Cu形成的颗粒的结构可以为,在Cu和Ag之间具有Ni或NiB缓冲层。

在烘烤含导电材料的复合材料的过程中通过有效地利用混有10到30%标度比氧气的气体,可减小形成门电极层的导电膜的电阻率,并且可将导电膜制成薄而光滑的膜。参见图8A到8C,给出了烘烤过程中导电膜状态变化的概观。图8A表示了含有导电材料如Ag的纳米浆料502通过喷嘴501释放在玻璃衬底500上的状态。该纳米浆料通过导电材料分散或溶解在有机溶剂中而形成。此外,该有机溶剂中还含有称为粘合剂的分散剂或热固性树脂。该粘合剂尤其可防止纳米浆料的开裂和不均匀烘烤。通过干燥和烘烤过程,有机溶剂汽化,分散剂分解去除,然后纳米浆料固化并同时因粘合剂而收缩。因此,纳米颗粒彼此熔合以固化该纳米浆料。同时,纳米颗粒的尺寸从数十nm长大到数千nm,相邻生长的纳米颗粒融合并连在一起形成金属链。另一方面,大多数剩下的有机成分(约80到90%)被挤出金属链之外。结果,形成了含金属链的导电膜503和由覆盖表面的有机成分构成的膜504(图8B)。在氮气和氧气存在的情况下烘烤纳米浆料502时,由有机成分构成的膜504可通过气体中的氧气与由有机成分构成的膜504中包含的碳或氢反应而去除。在烘烤气氛中不含氧气的情况下,由有机成分构成的膜504可通过氧等离子处理等去除(图8C)。如上所述,由有机成分构成的膜504按照下面的工序去除,即在氮气和氧气存在的情况下烘烤或干燥纳米浆料,并进行氧等离子处理。因此,含金属链的导电膜503可制成薄而光滑的薄膜,并降低其电阻率。

此外,通过减压下释放含导电材料的复合材料,该复合材料中的溶剂挥发,从而缩短了随后的热处理(干燥或烘烤)时间。

除了干燥和烘烤过程之外,可对表面进行平整或平滑处理。作为处理手段,有CMP(化学机械抛光);或者在导电膜上形成具有平面性的绝缘膜之后通过蚀刻形成平整导电膜的方法。

作为衬底,可以采用由绝缘体如玻璃衬底,石英衬底或氧化铝所构成的衬底;具有耐热性能够承受后处理中的处理温度的塑料衬底等等。在这种情况下,可形成底绝缘膜用以防止杂质从衬底上扩散,如氧化硅(SiOx)、氮化硅(SiNx)、氧氮化硅(SiOxNy)(x>y)、氮氧化硅(SiNxOy)(x>y)等等(x,y=1,2...)。或者,可以使用金属如不锈钢、或具有绝缘膜如氧化硅或氮化硅的半导体衬底。

门极绝缘膜103形成于门电极层上。门极绝缘层通过薄膜成型方法如等离子CVD、溅射法等等由单层或叠层含氮化硅、氧化硅、氮氧化硅、或氧氮化硅的膜制成。这里,氧化硅膜、氮化硅膜、以及氧化硅膜顺序形成于衬底上。然而,并不仅限于此结构、材料和方法。

半导体膜104形成于门极绝缘膜103上。该半导体膜由无定型半导体、结晶半导体或半无定型半导体制成。作为这些半导体,可以使用含硅、锗化硅(SiGe)等作为其主要成分的半导体膜。半导体膜可通过等离子CVD形成,优选厚度在10到100nm。

在上述半无定型半导体中,简单解释一下SAS(半无定型硅)。SAS可以通过硅化物气体的生长放电分解获得。作为典型的硅化物气体可以采用SiH4。也可以采用其它的硅化物气体如Si2H6、SiH2Cl2、SiHCl3、SiCl4、SiF4等等。通过用一种或多种选自氢、氢和氦、氩、氪和氖的稀有气体元素来稀释硅化物气体可容易地制成SAS。稀释率优选在10到1000倍的范围。当然,用于成膜的反应产物通过在大约0.1到133Pa的减压条件下生长放电分解而形成。1MHz到120MHz,优选13MHz到60MHz的高频电流可供形成生长放电。加热衬底的温度优选为300℃或以下,更优选在100到200℃。

通过在硅化物气体中混入碳化物气体如CH4或C2H6,或锗化物气体如GeH4或GeF4可将能带宽度控制在1.5到2.4eV,或0.9到1.1eV。

当特意不掺入杂质以控制价电子时,SAS表现出弱n型导电性。其随着氧气轻易地混入半导体膜而增强,因为生长放电在高于形成无定型半导体时的电流下进行。因此,在成膜同时或之后,通过在TFT的具有沟道形成区的第一半导体膜中掺入p型杂质可以控制阈值。作为赋予p型的杂质,通常可使用硼。可将1到1000ppm的杂质气体如B2H6或BF3混入硅化物气体中。在用硼作为赋予p型的杂质时,硼浓度可以在1×1014到6×1016个原子/cm3。通过上述SAS形成沟道形成区,可获得1到10cm2/V·sec的电子场效应迁移率。

根据以下步骤可获得结晶半导体膜,即在含有催化剂如镍的溶液中处理无定型半导体膜;在500到750℃下进行加热结晶处理过程以获得结晶硅半导体膜;进行激光结晶化过程以提高结晶度。

利用乙硅烷(Si2H6)和氟化锗(GeF4)原料气体,通过LPCVD(低压CVD)直接形成多晶半导体膜可获得结晶半导体膜。LPCVD可以但不仅限于在Si2H6/GeF4=20/0.9的气流比,成膜温度400到500℃,载气为He或Ar的条件下进行。

n型半导体膜105形成于半导体膜104之上。作为n型杂质元素,可以使用砷(Ar)和磷(P)。在形成n型半导体膜的情况下,利用等离子CVD法通过SiH4、H2和PH3(磷化氢)混合气体的生长放电分解可形成n型(n+)硅膜。可制成含p型杂质元素如硼(B)的半导体膜来代替n型半导体膜105。

通过在n型半导体膜105上释放含第二导电材料的复合材料可形成源电极108和漏电极109。可以从上述对第一导电材料的描述中适当地选择所述第二导电材料、导电颗粒的结构、释放条件、干燥条件、烘烤条件等等。此外,第一和第二导电材料以及第一和第二颗粒结构可以相同或不同(图1A)。

尽管未示出,但可以在向n型半导体膜105上释放所述含第二导电材料的复合材料之前进行预处理过程,用以提高n型半导体膜105和源电极108之间的粘性,以及n型半导体膜105和漏电极109之间的粘性。预处理过程可以用类似于形成门电极102的预处理方法进行。

利用源电极108和漏电极109作为掩模,以含氯气体如Cl2、BCl3、SiCl4或CCl4;氟化物气体如CF4、SF6、NF3或CHF3;或O2作为蚀刻气体,通过等离子蚀刻n型半导体膜105形成源极区112和漏极区113。然而,并不仅限于该条件。蚀刻过程可利用大气等离子来进行。在这种情况下,优选用CF4和O2的混合气体作为蚀刻气体。在用相同的半导体制成n型半导体膜105和半导体膜104时,需要注意蚀刻速度和蚀刻时间,因为当蚀刻n型半导体膜105时还一同蚀刻了半导体膜104。然而,在沟道形成区处的半导体膜形成厚度为5nm或更高,优选10nm或更高,更优选50nm或更高的情况下,即使蚀刻了半导体膜104的一部分,也可以获得足够的TFT迁移率。

通过在半导体膜104的沟道区进行液滴释放而形成了绝缘膜115。由于绝缘膜115起沟道保护膜的作用,因而可通过释放耐热树脂如硅氧烷,或具有耐蚀刻性和绝缘性的物质如丙烯酸、苯并环丁烯、聚酰胺、聚酰亚胺、苯并咪唑、或聚乙烯醇来形成。优选使用硅氧烷和聚酰亚胺。为防止沟道区蚀刻过度,可形成厚度在100nm或更高,优选200nm或更高的绝缘膜115(图1B)。因此,如图1B所示,绝缘膜115可制成类似于垛的形状位于源电极108和漏电极109上方。

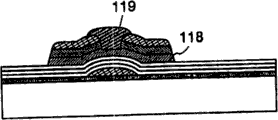

然后,利用源电极108、漏电极109和绝缘膜115作为掩模,以含氯气体如Cl2、BCl3、SiCl4或CCl4;氟化物气体如CF4、SF6、NF3或CHF3;或O2作为蚀刻气体,通过等离子蚀刻半导体膜104形成岛形半导体膜118。然而,并不仅限于该条件。蚀刻过程可利用大气等离子来进行。在这种情况下,优选用CF4和O2的混合气体作为蚀刻气体。而且,由于用作沟道保护膜的绝缘膜115形成于岛形半导体膜118中的沟道区119上,沟道区119在上述蚀刻过程中不会由于过度蚀刻而损坏。因此,不用任何光刻胶掩模就可以制造出具有稳定性和高迁移率的沟道保护型TFT(沟道截断环型)(图1C)。

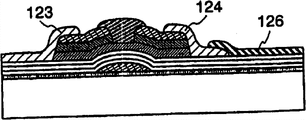

通过释放含第三导电材料的复合材料形成源极布线123和漏极布线124以便与源电极108和漏电极109相接触,并通过将源极布线123和漏极布线124与像素电极126相连接,可提供由含有有机化合物或无机化合物的层构成的液晶元件或发光元件(通常为采用电致发光的发光元件)。因此,可制成有源矩阵液晶显示器或薄显示器如电致发光装置,分别可通过由上述方法制成的半导体元件来控制。可以从上述对第一导电材料的描述中适当地选择所述第三导电材料、导电颗粒的结构、释放条件、干燥条件、烘烤条件等等。此外,第二和第三导电材料以及第二和第三颗粒结构可以相同或不同。像素电极优选通过ITO、ITSO、ZnO、GZO、IZO、有机铟、有机锡等的液滴释放法制成(图1D)。

尽管未示出,但可以在形成源极布线123、漏极布线124和像素电极126时进行预处理过程以便提高与下层之间的粘性。预处理过程可通过类似于形成门电极层102的预处理方法来进行。

如上所述,根据本发明,在源极区112和漏极区113形成之后,用作沟道区的部分被起沟道保护膜作用的绝缘膜115所覆盖从而形成岛形半导体膜。因此,不需要光刻胶掩模,这样可简化工序。本发明提供了形成半导体元件新手段,其结合了利用源电极和漏电极金属掩模形成源极区和漏极区以去除单一导电性半导体膜的方法,和用于形成沟道保护膜以防止沟道区移动的专用于沟道保护型的方法。根据上述构造,可以只利用源电极和漏电极金属掩模而不用任何光刻胶掩模来制造半导体元件。结果,可简化工序,并通过节约材料而大大降低成本。可以以低成本高产量地实现高通量地制造高稳定性的半导体元件,以减少生产时间,尤其是在大于1×1m或其两或三倍大的衬底上。

在根据本发明的半导体元件中,可以提高衬底和导电膜(如通过液滴释放法形成的门电极层等)之间的粘性,因为衬底中至少具有门电极层的部分经过了处理,例如形成了氧化钛等等。

通过形成具有绝缘膜的半导体膜部分,厚度小于其它半导体膜,无疑可将n型杂质区划分成源极区和漏极区。而且,通过形成具有厚度在5nm以上,优选10nm以上的半导体膜的半导体膜部分,可获得足够大的沟道迁移率。

在根据本发明的半导体元件中,用作沟道保护膜的绝缘膜115形成于沟道区119上,因此,沟道区119在半导体膜104的蚀刻过程中不会由于过度蚀刻而损坏。因而,半导体元件具有稳定性和高迁移率。通过形成厚度在100nm或以上的绝缘膜,必然可以提高绝缘膜作为沟道保护膜的功能以防沟道区的损坏。因而,可得到具有高迁移率的高稳定性半导体元件。为获得上述优点,有效的是使绝缘膜形成由第一绝缘膜和第二绝缘膜组成的双层结构,或者由三或多层组成的多层结构。

附图简要说明

在附图中:

图1A到1D是表示根据本发明的TFT工艺示意图;

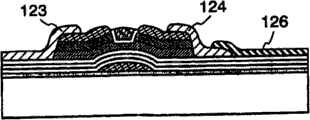

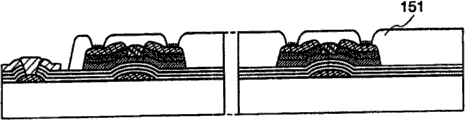

图2A到2D是表示根据本发明的TFT工艺示意图;

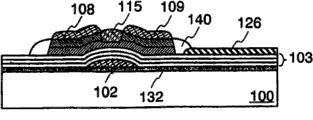

图3A到3C是表示根据本发明的液晶显示屏工艺示意图;

图4A和4B是表示根据本发明的液晶显示屏工艺示意图;

图5A到5C是表示根据本发明的液晶显示屏工艺示意图;

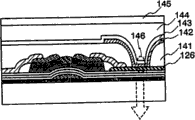

图6A到6C是表示根据本发明的电致发光屏工艺示意图;

图7A到7C是表示根据本发明的顶发光装置、底发光装置、以及双重发光装置的示意图;

图8A到8C是表示用于形成氧化钛膜的方法示意图;

图9A到9C表示根据本发明的电器设备的一个实施例示意图;

图10表示了液滴释放系统的构造;

图11A和11B是表示根据实施方案采用间距为像素间距的n倍的喷嘴,通过分别布设偶数行和奇数行的布线而形成的布线示意图。

图12A到12D是表示根据实施方案用具有不同释放口直径的多个喷嘴释放形成的像素电极示意图;

图13A到13C是表示根据实施方案用具有不同释放口直径的多个喷嘴释放形成的平面布线示意图;

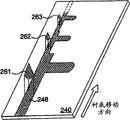

图14是表示根据实施方案用具有不同释放口直径的多个喷嘴释放形成的不同行宽布线示意图;以及

图15A到15C是表示根据实施方案用具有不同释放口直径的多个喷嘴释放形成的、填充有导电材料的开口部分示意图;

本发明的最佳实施方案

实施例1

在实施例1中,解释了在衬底上形成门电极层之前预处理该衬底的情形。

第一种方法,可在衬底100上直接形成氧化钛膜132,如图1A中所示。通过旋涂法、液体释放法、喷涂法、溅射法、CVD等等可使氧化钛膜132遍布形成于衬底上。之后,通过液滴释放法在氧化钛膜132上形成门电极层102。由此,通过在其之间插入氧化钛膜132可提高衬底100和门电极层102之间的粘性。形成门电极层102之后,通过蚀刻过程可留下或去除该门电极层102周围的氧化钛膜132。而且,蚀刻处理优选在大气压下进行。此外,可以形成钛膜来代替形成氧化钛膜。这里,门电极层102可通过在氧化钛膜上层叠Ag/Cu而形成。或者,在氧化钛膜上可以只层叠Cu。

第二种方法,可选择性地通过液滴释放形成氧化钛膜。作为液滴释放法,除了喷墨法之外还可以采用丝网印刷或胶版印刷。或者,可以使用溶胶凝胶。之后,可通过液滴释放法在氧化钛层或氧化钛层内表面上选择性地形成门电极层。此外,可形成钛膜来代替形成氧化钛膜。

第三种方法,通过旋涂法、液滴释放法、溅射法、CVD等等在衬底上遍布形成钛膜;通过液滴释放法将用于形成门电极层的含导电材料的复合材料选择性地形成于钛膜上(图8A)。然后,将复合材料干燥并烘烤。同时,氧化该钛膜505。这样,在复合材料的周围形成了氧化钛膜506。氧化钛膜有优良的透光性。例如,在底部发光装置中可有效地利用氧化钛膜以从衬底上发光,如图6C和7B所示。通过旋涂法、液滴释放法、溅射法、CVD等等在衬底上遍布形成钛膜之后,在选择性地释放用于形成门电极层的含导电材料的复合材料之前,可通过热处理形成氧化钛膜。

在上述第一到第三种方法中,可用所谓的光催化物质来代替形成钛膜和氧化钛膜,例如钛酸锶(SrTiO3)、硒化镉(CdSe)、钽酸钾(KTaO3)、硫化镉(CdS)、氧化锆(ZrO2)、氧化铌(Nb2O5)、氧化锌(ZnO)、氧化铁(Fe2O3)、氧化钨(WO3)等等。或者,对于氧化物来说,可使用被氧化之前的物质(Zr、Nb、Zn、Fe、W等)。

第四种方法,通过在衬底上形成耐热树脂,如聚酰亚胺、丙烯酸、硅氧烷等等可提高衬底和电极层之间的粘性。这些材料可遍布形成于衬底上或形成有门电极层的区域上。在该材料遍布形成于衬底上的情况下,通过蚀刻或灰化可去除门电极层周围所残留的膜。

第五种方法,可通过等离子处理形成有衬底和门电极层的部分来提高粘性。优选但不限于在大气压下进行等离子处理。

实施例2

在实施例2中,解释了通过两层层叠形成起沟道保护膜作用的绝缘膜的情形。

如图1B所示,利用源电极108和漏电极109作为掩模,通过蚀刻n型半导体膜105形成源极区112和漏极区113。然后,通过CVD、溅射法等方法将氮化硅膜133遍布形成于整个表面(图2A)。通过液滴释放法在用作半导体膜的沟道区的区域上和氮化硅膜133上形成绝缘膜115。由于绝缘膜115不用作沟道保护膜而是用于去除氮化硅膜133的掩模,因而通过释放耐热树脂如硅氧烷、或具有耐蚀刻性和绝缘性的物质如丙烯酸、苯并环丁烯、聚酰胺、聚酰亚胺、苯并咪唑、或聚乙烯醇的复合材料来形成绝缘膜115。优选使用硅氧化和聚酰亚胺。为防止沟道保护区蚀刻过度,优选形成氮化硅膜133和绝缘膜115的总厚度在100nm或以上,更优选在200nm或以上(图2B)。

利用绝缘膜115作为掩模蚀刻掉氮化硅膜133从而剩下绝缘膜115、134,它们分别起到沟道保护膜的作用。绝缘膜134毋庸置疑是由氮化硅膜形成的。利用氯化物气体,通常有Cl2、BCl3、SiCl4、CCl4等;氟化物气体通常有CF4、SF6、NF3、CHF3等;或O2作为蚀刻气体,通过等离子蚀刻法可蚀刻氮化硅膜。然而,蚀刻气体并不仅限于此。蚀刻处理可采用大气压等离子法。

双层沟道保护膜可提高作为沟道保护膜的功能,防止沟道区域损坏,并提供具有高迁移率的稳定半导体元件。或者,可通过层叠三或多层形成沟道保护膜。其底层并不仅限于氮化硅膜;也可以使用含有其它硅的绝缘膜。这种沟道保护膜可通过选择性地层叠能够通过液滴释放法成膜的膜如绝缘膜115而形成。

利用源电极108、漏电极109和绝缘膜115、134作为掩模蚀刻半导体膜104从而形成岛形半导体膜118。用作沟道保护膜的绝缘膜115形成于该岛形半导体膜118中的沟道区119上。因此,可防止由于上述蚀刻过程中的过度蚀刻造成的损坏。因而,可以不用任何光刻胶掩膜而制造出具有稳定性和高度迁移率的沟道保护(沟道截断环)型TFT(图2C)。

通过释放含第三导电材料的复合材料形成源极布线123和漏极布线124,从而以实施方案中所述的方式与源电极108和漏电极109相接触。而且,源极布线123或漏极布线124与像素电极相连接。然后,通过含有机化合物或无机化合物(通常为利用电致发光的发光元件)的层形成液晶元件或发光元件。因此,可得到薄显示器如有源矩阵液晶显示器或有源矩阵电致发光显示器,它们分别可以通过由上述过程制成的半导体元件来控制(图2D)。

实施例3

在实施例3中,解释了通过液滴释放与电镀法相结合用以形成导电膜的方法。

首先,通过液滴释放形成含Ag的复合材料。在这种情况下,为在几到几十μm的较窄行宽中形成厚布线,需要反复释放Ag。或者,可通过将具有Ag的衬底浸泡在含Cu的电镀溶液中,或者直接将该电镀溶液喷在衬底上来增加行宽。通过液滴释放形成的复合材料尤其具有许多不规则性,因此可容易地进行电镀。此外,由于Ag价格昂贵,镀Cu使得成本降低。通过该实施例的方法用于形成布线的导电材料并不仅限于上述种类。

在镀Cu之后,通过形成缓冲层,如NiB等来平面化处理该具有不规则性的导电膜表面。然后,优选形成门极绝缘膜。

实施例4

在实施例4中,参考图3A至5C解释了根据本发明用于制造有源矩阵LCD屏板的方法。

第一种方法,通过液滴释放在按照本发明制造的TFT上选择性地形成平面膜151,并通过液滴释放在不形成平面膜151的区域上形成分别与源电极和漏电极连接的源极布线和漏极布线152,如图3A所示。此外,与像素TFT 654相连的源极布线或漏极布线可用作像素电极,如图3A所示。当然,可分别形成像素电极以连接源极布线或漏极布线。源电极、漏电极、源极布线、和漏极布线可由相同或不同的导电材料制成。

该方法不采用接触孔形成于平面膜中的设计。然而,其在外观上似乎形成了接触孔。因此,该方法被称为松散接触。作为平面膜,优选形成有机树脂,如丙烯酸、聚酰亚胺或聚酰胺,或者具有Si-O键和Si-CHx价的绝缘膜,其由作为原材料的基于硅氧烷的材料制成。

之后,将液晶层154插在TFT衬底和相对衬底之间。这些物质通过密封剂159粘合在一起。TFT衬底上形成了圆柱隔块158。该圆柱隔块158可沿着形成于像素电极上的接触孔凹部形成。圆柱隔块158优选形成的高度在3到10μm,尽管这取决于液晶材料。接触部分的凹部相当于接触孔。通过形成沿该凹部的隔块可防止液晶取向的变形。

取向膜153形成于TFT衬底上。然后进行摩擦处理。接着,在相对衬底155上形成透明导电膜156和取向膜157。之后,通过密封剂将TFT衬底和相对衬底贴合在一起用以在其之间注入液晶。这样,形成了液晶层154。因而,完成了有源矩阵液晶显示器。此外,液晶层154可通过逐滴加入液晶而形成。特别地,这在采用大于1m的大有源矩阵衬底制造液晶显示器情况下是非常有效的方法。

而且,取向膜153、157,以及圆柱隔块158可通过液滴释放法选择性地形成。特别地,这在采用大于1m的大有源矩阵衬底制造液晶显示器的情况下是非常有效的方法。

下面说明端部652。如图1或类似图中所示,门极绝缘膜留在除TFT元件之外的区域中。因此,需要用于连接与门电极层同时形成的布线171和FPC 628(柔性印制电路)的接触孔。这里,将要形成接触孔的区域周围被通过液滴释放法形成的导体172所覆盖,用该导体作为掩模形成了接触孔。通过液滴释放法释放与导体172相同或不同的导体173以填充接触孔。这样,导体172和173可形成于门极绝缘膜上。根据已知的方法通过各向异性导电膜627将导体172、173和FPC 628与端电极626粘合,可将布线171与FPC 628相连。端电极626优选通过透明导电膜形成。

FPC部分中的接触孔在制造TFT的过程中可以打开。或者,通过在形成源极布线和漏极布线的同时形成导体172或173可以打开接触孔。液滴释放法的一个优点在于,复合材料可被选择性地释放在预定的位点。一个液滴释放工序优选起到多个常规工序的作用。

通过上述过程,完整制造采用根据本发明制造的TFT的有源矩阵LCD屏板。TFT可通过实施方案或实施例中所述的方法形成。这里,一个晶体管具有一个像素。然而,也可以两或多个晶体管具有一个像素。TFT的极性可以是n型或p型的。TFT可制成由n型TFT和p型TFT构成的CMOS结构。其类似于驱动电路TFT 653的情形。在形成CMOS结构的情况下,用于连接各TFT的布线可在选择性地形成上述平面膜之后,通过在开口部分中液滴释放含导电材料的复合材料而形成。

第二种方法,如图3B所示,筒形导体160(也称为柱、塞等等)通过液滴释放形成于按照本发明制造的TFT的源电极和漏电极上。作为形成柱体的导电材料,可以使用类似于形成上述门电极层或类似物的材料。平面膜150通过液滴释放等方式形成于筒形导体160上。作为平面膜,通过选择性地液滴释放,优选形成有机树脂,如丙烯酸、聚酰亚胺或聚酰胺,或者具有Si-O键和Si-CHx价的绝缘膜,其由作为原材料的基于硅氧烷的材料制成。

在平面膜形成于柱体上的情况下,可蚀刻平面膜和柱体的表面以获得具有平面表面的柱体,如图3C所示。用于连接源电极和漏电极的源极布线和漏极布线152通过液滴释放形成于平面膜上。与像素TFT654相连的源极布线和漏极布线152可用作像素电极,如图3C所示。毋庸置疑,像素电极可分别制成以连接源极布线或漏极布线。此外,源电极、漏电极、柱体、源极布线、以及漏极布线由相同或不同的导电材料制成。

之后,液晶元件的成型过程与第一种方法相同。FPC部分中的接触孔可在制造TFT的过程中打开。或者,通过在形成柱体、源极布线和漏极布线的同时形成导体172或173可以打开接触孔。

第三种方法,如图4A中所示,相对于平面膜151的材料具有液体流动(liquid-shedding)性质的筒形绝缘体(下文中称为柱绝缘体161)形成于根据本发明通过液滴释放法制造的源电极和漏电极之上;平面膜151形成于柱绝缘体161的周围。做为柱绝缘体的材料,可以使用水溶性有机树脂如在CF4等离子体中处理过具有液体流动性质的PVA(聚乙烯醇)。作为平面膜,优选选择性地通过液滴释放法形成有机树脂,如丙烯酸、聚酰亚胺或聚酰胺,或者由作为原材料的基于硅氧烷的材料制成、具有Si-O键和Si-CHx价的绝缘膜。在柱绝缘体161的周围形成平面膜151之后,柱绝缘体161可通过水洗、蚀刻等方法容易地去除。在通过蚀刻去除的情况下,优选进行各向异性蚀刻以防接触孔成倒锥形。而且,由于柱绝缘体如PVA具有绝缘性,即使部分绝缘体留在了接触孔的侧壁处也不会引起任何问题。

之后,与源电极和漏电极通过接触孔连接的源极布线和漏极布线152通过液滴释放形成于平面膜上。与像素TFT 654连接的源极布线或漏极布线152可用作像素电极,如图4B中所示。毋庸置疑,像素电极可分别制成以连接源极布线或漏极布线。此外,源电极、漏电极、柱体、源极布线、以及漏极布线由相同或不同的导电材料制成。在接触孔由于去除上述柱绝缘体的过程而形成倒锥形的情况下,可通过液滴释放法层叠含有导电材料的复合材料以填充源极布线和漏极布线形成中的接触孔。

形成液晶的过程与第一种方法中相同。FPC部分中的接触孔可在制造TFT的过程中打开。或者,通过在形成源极布线和漏极布线的同时形成导体172或173可以打开接触孔。

第四种方法,如图5A中所示,相对于平面膜151的材料的液体流动材料162形成于根据本发明通过液滴释放、旋涂、喷溅等方法制成的TFT源电极和漏电极上;通过PVA、聚酰亚胺等制成的掩模163形成于要形成接触孔的区域中;利用PVA等去除液体流动材料162;平面膜151形成于剩余的液体流动材料162的周围。作为形成液体流动材料162的材料,可以使用氟代硅烷偶联剂如FAS(氟硅烷)或类似物。可选择性地通过液滴释放法形成掩模163如PVA、聚酰亚胺等等。液体流动材料162可通过氧气灰化或大气压等离子体去除。此外,PVA制成的掩模163还可通过水洗容易地去除,或者由聚酰亚胺形成的掩膜163可以通过剥离器N300容易地去除。

在液体流动材料162留在要形成接触孔的区域中的状态下(图5B),可通过液滴释放、旋涂等方法制成平面膜151。由于液体流动材料162留在要形成接触孔的区域中,其上就不形成平面膜。而且,接触孔并不会形成倒锥形。作为平面膜,优选选择性地通过液滴释放法形成有机树脂,如丙烯酸、聚酰亚胺或聚酰胺,或者由作为原材料的基于硅氧烷的材料制成、具有Si-O键和Si-CHx价的绝缘膜。平面膜151形成之后,液体流动材料162可通过氧气灰化或大气压力法去除。

之后,与源电极和漏电极通过接触孔连接的源极布线和漏极布线152通过液滴释放形成于平面膜上。与像素TFT 654连接的源极布线或漏极布线152可用作像素电极,如图5C中所示。毋庸置疑,像素电极可分别制成以连接源极布线或漏极布线。此外,源电极、漏电极、源极布线、以及漏极布线由相同或不同的导电材料制成。

形成液晶的过程与第一种方法中相同。FPC部分中的接触孔可在制造TFT的过程中打开。或者,通过在形成源极布线和漏极布线的同时形成导线172或173可以打开接触孔。

在上述第一到第四种方法中,图3A到5C中未示出,可通过预处理过程在衬底和门电极层之间插入TiOx膜等等来提高它们之间的粘性。预处理过程可在形成源极布线、漏极布线、柱体、像素电极、导体172、导体173等的情况下进行。作为预处理过程,可采用实施方案和实施例中所述的处理。

此外,优选在源电极和漏电极上形成防止杂质在TFT上扩散的钝化膜(未示出)。钝化膜可以由氮化硅、氧化硅、氮氧化硅、氧氮化硅、氧氮化铝;或其它绝缘材料例如氧化铝、类金刚石碳(DLC)、或者含氮的碳(CN),通过薄膜成型法如等离子CVD、或喷溅法形成。该材料可以与用于形成沟道保护膜的材料相同。或者,这些材料可以为叠层结构。此外,钝化膜可以由含绝缘材料颗粒的复合材料通过液滴释放法形成。

像素电极可以不提供平面膜而间接形成于衬底上,并且可以在其上形成取向膜(未示出)。在这种情况下,TFT优选由绝缘盖膜或钝化膜所覆盖。

实施例5

在实施例5中,参考图6A至6C解释了根据本发明用于制造有源矩阵电致发光屏板的方法。

首先,如图6A所示,根据实施例和实施方案中所述的上述方法制造TFT。然后,将用于改善阶梯覆盖(也称为边覆盖)的绝缘体140形成于岛型半导体的至少侧面处。形成源极布线123和漏极布线124,分别与TFT的源电极108和漏电极109相接触。源电极和漏电极与像素电极126(一般来说为空穴注入电极(阳极))相连。在这种情况下,布线可以以良好的覆盖率光滑地形成,因为布线层下具有边覆盖。因此,可防止断裂(图6B)。

此外,可形成具有叠层构造的像素电极126。例如,采用叠层构造的ITSO,其中TFT侧ITSO的氧化硅浓度优选设定成低浓度(1到6原子%),发光元件侧ITSO的氧化硅浓度优选设定成高浓度(7到15原子%)。像素电极126的表面可以通过CMP平整化或者通过聚乙烯醇多孔物体抛光。CMP抛光之后,像素电极126的表面可以用紫外线照射或在氧气等离子体中处理。

通过蚀刻形成像素电极126之后,铟、锡、氧化铟、或氧化锡从形成像素电极126的导电层内部释放出来,所述导电层通过光刻胶剥离过程、水清洗(水洗涤)过程、紫外线照射过程等等形成。因此,硅、氧化硅、氮化硅等等沉积在导电层表面或表面附近的层内,从而形成由沉积材料作为主要成分的阻挡层。由硅、氧化硅、氮化硅等通过汽相淀积、喷溅等方法可特意形成阻挡层。该阻挡层可增加空穴注入电极的逸出功并提高空穴注入性。

TFT、布线、以及像素电极的顶部可以由液滴释放法选择性地形成的堤(bank)所覆盖。作为堤141,优选采用具有Si-O键和Si-CHx价、由有机树脂如丙烯酸、聚酰亚胺、或聚酰胺,或者作为原材料的基于硅氧烷的材料制成的绝缘膜。

然后,形成含有机化合物(也称为电致发光层,下文中称为“有机化合物层142”)的层,以便与堤141开口处的像素电极126相接触。该有机化合物层142可由单层或叠层构成。例如,该有机化合物层142可具有构造:1)阳极/空穴注入层/空穴传输层/发光层/电子传输层/阴极;2)阳极/空穴注入层/发光层/电子传输层/阴极;3)阳极/空穴注入层/空穴传输层/发光层/电子传输层/电子注入层/阴极;4)阳极/空穴注入层/空穴传输层/发光层/空穴阻断层/电子传输层/阴极;5)阳极/空穴注入层/空穴传输层/发光层/空穴阻断层/电子传输层/电子注入层/阴极,等等。

形成电子注入电极143(阴极)以覆盖有机化合物层142。电子注入电极143可通过已知的具有低逸出功的材料制成,如Ca、Al、CaF、MgAg、或AlLi。通过在堤141的开口处重叠像素电极126、有机化合物层142和电子注入电极143可形成发光元件146。钝化膜144形成于电子注入电极143之上(图6C)。

上述发光元件由插在电极对之间含有有机化合物或无机化合物的叠层式发光层构成,其分别具有不同的载体传输性质。空穴从电极注入而电子从另一电极注入。该发光元件利用了从电极注入的空穴和从另一电极注入的电子彼此重组以激发发射中心,并且当受激分子回到基态时以光的形式辐射能量的现象。形成电极的材料的逸出功大小(从金属或半导体的表面将电子吸引到该表面之外所需的最小能量)是该发光层的空穴注入和电子注入性质的指标。用于注入空穴的电极优选具有大逸出功,而用于注入电子的电极优选具有小逸出功。

优选在相对衬底145上形成波长板、偏振板、以及抗反射膜。作为波长板,可顺序形成λ/4和λ/2以设定慢轴。

为完成图6C中所示的状态,优选通过不易漏气的气密性保护膜(多层膜、紫外固化树脂膜等等)或覆盖材料包装该发光元件以防暴露于空气中。

实施例6

在实施例5中,解释了根据本发明制造的底发光装置,如图6C所示。实施例6中,解释了图7A所示的顶发光装置和图7C所示的双重发光装置,其分别根据本发明制造。

首先说明双重发光装置。作为空穴注入电极的材料,可以采用如实施例5中所用的透明导电膜,如ITO、ITSO、ZnO、IZO或GZO。在用ITSO作为像素电极126的情况下,可重叠含有不同浓度氧化硅的多层ITSO层。优选地,底ITSO层(位于源极布线或漏极布线侧)优选具有低浓度的氧化硅,顶ITSO层(位于发光层侧)优选具有高浓度的氧化硅。因此,像素电极126和TFT之间的连接可保持低电阻,并可提高向电致发光层注入空穴的效率。当然,可通过层叠其它材料和ITSO(例如顺序层叠ITO层和ITSO层)来制成像素电极。或者,可形成由其它材料构成的叠层。

作为电子注入电极143,可使用厚度在1到10nm的薄铝膜,即含由痕量Li或类似物的铝膜来透过发光层中产生的光线。这样,可获得顶和底表面都能发出发光元件中所产生的光线的双重发光装置(图7C)。

在图7A到7C中,附图标记141和142表示堤;142为有机化合物层;144为钝化膜;145为相对衬底;而146为发光元件。

接着,参见图7A说明顶发光装置。一般来说,光线从衬底对侧发出(上方)的顶发光装置可通过以下步骤获得:如图7B所示的用作空穴注入电极的像素电极126和底发光式电子注入电极143交换,含有机化合物的层反向层叠以翻转TFT(采用n型TFT)的极性。在电极和含有有机化合物的层反向层叠如图7A中所示的情况下,通过含不同浓度氧化硅的发光氧化物导电层构成的叠层构造制成像素电极126可得到具有改善的发光效率和低功耗的高稳定性发光装置。作为电子注入电极143,可采用具有反光性的金属电极或类似物。

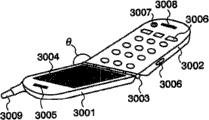

实施例7

采用了实施例4中所述的液晶显示屏板或实施例5、6中所述的电致发光屏板的电器实例有,电视接收装置、便携书(电子书)、手机,如图9A到9C中所示。

图9A表示了电视接收装置,其中采用液晶或电致发光元件的显示模块2002设置在外壳2001中;接受器2005接收综合电视广播,并通过调制解调器2004连接到无线或有线通信网从而单向(发射器到接收器)和双向(发射器和接收器之间,或者接收器之间)交换信息。该电视接收装置可通过设在外壳中或无线遥控器2006中的开关来操控。遥控器2006可具有显示部分2007用以显示信息。

除了主屏幕2003之外,该电视接收装置还可以具有由第二显示模块制成、上面用来显示频道或音量的小屏幕2008。主屏幕2003可通过具有良好视角的电致发光显示模块制成。小屏幕可由能以低功耗显示图像的液晶显示模块制成。为了优先减小功耗,主屏幕2003可由液晶显示模块制成,小屏幕可由能够使小屏幕闪烁的电致发光显示模块制成。

图9B显示了由主体3101、显示部分3102、3103、存储介质3104、操作开关3105、天线3106等等构成的便携书(电子书)。

图9C表示了一种手机。附图标记3001表示显示屏、3002表示操作面板。显示屏3001和操作面板3002通过连接部分3003彼此连接。连接部分3003处由显示屏3001上具有显示部分3004的面与操作面板3002上具有操作键3006的面之间的角度θ可以任意改变。该手机还包括声音输出部分3005、操作键3006、电源开关3007、声音输入部分3008、天线3009。

实施例8

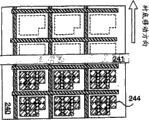

根据本发明的半导体元件优选通过图10中所示的液滴释放系统制成。首先,进行电路设计,如CAD、CAM、CAE等等,并通过电路设计工具800确定薄膜和对齐标记的预定设计。

将包括设计好的薄膜和对齐标记设计的薄膜图案数据801输入计算机802,以便通过信息网络如存储介质或LAN(局域网)来控制液滴释放装置。根据薄膜图案的数据801,在液滴释放装置803的其它喷嘴(用于从细小端部开口中喷涂液体或气体的装置)中选择具有最佳直径的释放口的喷嘴,其中储存有形成薄膜的材料的复合材料,或者其连接着储存有该复合材料的罐;然后,确定液滴释放装置803扫描路径(移动路径)。在预先确定了最佳喷嘴的情况下,只需要确定喷嘴的移动路径。

对齐标记817通过光刻技术或激光在将会有薄膜的衬底804上形成。将具有对齐标记的衬底放在液滴释放装置中的台816上,该对齐标记的位置由安装在该装置中的成像工具805测得,然后,其作为位置信息807通过图像处理装置806输入计算机802中。计算机802验证通过CAD等方法设计的薄膜图案的数据801以及由成像装置805获得的位置信息807,从而使衬底804和液滴释放工具803对齐。

之后,通过控制器808控制的液滴释放工具803按照预定的扫描路径释放复合材料818,并形成预期的薄膜图案809。通过选择释放口的直径可以适当的控制释放量。然而,释放量会随一些条件而发生轻微变化,例如释放口的移动速度、释放口和衬底之间的距离、复合材料的释放速度、释放空间的气氛、释放空间的温度或湿度。因此,需要控制这些条件。优选预先通过实验或估算确定最佳条件,并且优选将这些结果对每种复合材料建立数据库。

作为薄膜图案数据的有,用于例如液晶显示器或电致发光显示器的有源矩阵TFT衬底的电路图或类似物。图10表示了用于这种有源矩阵TFT衬底的导电膜的循环电路图示意图。附图标记821表示所说的门极布线;822是源极信号线(第二布线);823是像素电极,或空穴注入电极或电子注入电极;820是衬底;而824是对齐标记。当然,薄膜图案809对应于薄膜图案信息中的门极布线821。

此外,液滴释放工具803可具有但不仅限于喷嘴810、811和812的一体化组合。各喷嘴具有多个释放口813、814和815。上述薄膜图案809通过在喷嘴810中选择预定的释放口813而形成。

液滴释放工具803优选具有多个不同释放口、释放量、或喷嘴间距的喷嘴,以便能制造出具有各种行宽的薄膜图案并改进生产时间。释放口之间的距离优选越窄越好。此外,液滴释放工具803优选具有长度在1m以上的喷嘴,以便在大小在1×1m或以上或其两三倍大的衬底上高通量地进行释放。液滴释放工具803可以是伸缩自如的以便自由控制释放口之间的距离。为获得高分辨率,即描绘出平滑的图案,可以倾斜喷嘴或喷头。因而,可以在大块区域如矩形区域上制图。

一个喷头可以平行具有不同间距的喷头的喷嘴。在这种情况下,释放口的直径可以相同或不同。在如上所述采用多个喷嘴的液滴释放装置的情况下,需要提供不在使用中的喷嘴等待位置。该等待位置可具有供气工具和多孔喷头以将等待位置中的气氛替换成与复合材料溶剂气体相同的气氛。因此,可在一定程度上防止干燥。而且,可具有供给干净空气的清洁单元或类似物以减少工作位中的灰尘。

在释放口之间的距离由于喷嘴803规格而不能变窄的情况下,喷嘴间距可设计成显示器中像素的整数倍。这样,如图11A和11B中所示,通过移动衬底804可将复合材料释放于衬底804上。作为成像工具805,可采用利用半导体元件将强弱光转换成电信号的照相机CCD(电耦合装置)。

上述方法是为了通过液滴释放装置803沿着预定的路径扫描台816上的固定衬底以形成薄膜图案809。另一方面,步骤中可形成薄膜图案809,即,固定液滴释放装置803、将台809沿着薄膜图案的数据801确定的路径在XYθ方向上传送。在液滴释放装置803具有多个喷嘴的情况下,需要确定具有最佳直径释放口的喷嘴,其储存有包含形成薄膜的材料的复合材料,或者连接着用于储存该复合材料的罐。

此外,可以使用具有多余量的多个喷嘴。例如,当喷嘴812(或811)首先释放复合材料时,可以控制释放条件以便喷嘴810与喷嘴812(或811)同时释放复合材料。因此,就算前喷嘴出现某些问题例如释放口阻塞,复合材料也可以从后喷嘴810中释放,并且其至少可以防止布线中断或类似问题。

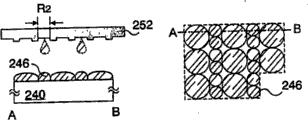

上述方法只利用了喷嘴810的一种预定释放口来形成薄膜图案809。或者如图12A到15C中所示,根据要形成的行宽或薄膜厚度,可使用多个喷嘴来释放复合材料。

图12A到12D以及图13A到13C表示了,例如,在衬底240上形成像素电极图案244。这里,使用了由不同大小R1、R2和R3(R1>R2>R3)的三个喷嘴251到253构成的液滴释放工具241。首先,利用具有最大直径释放口的喷嘴251释放复合材料245(图12B或13A)。接着,用释放口的直径小于喷嘴251的喷嘴252在不能制图或者由最大直径释放口造成的具有不规则性的部位处选择性地释放复合材料246(图12C或13B)。之后,平整化图案表面,按需要使用具有最小直径释放口的喷嘴253选择性释放复合材料247(图12D或13C)。该方法可有效地用于制造较大的导体如像素电极。该方法可制造没有不规则度的平面图案。

图14表示了布线图案248形成于衬底240上的状态。作为液滴释放装置,可使用上述喷嘴251至253。由于从这些喷嘴中释放出的各液滴261到263的量有所不同,很容易制成具有不同行宽的图案,如图14中所示。

图15A到15C表示了通过顺序地释放复合材料以填充开口部分213来形成,例如导电膜的方法。附图标记210表示衬底;211为半导体或导体;而212为绝缘体。绝缘体212具有开口213。通过包括多个喷嘴251到253的液滴释放工具释放复合材料,所述喷嘴设置成多行,释放口在上述各行的同轴方向排列。开口直径由下向上变大。首先,通过释放口直径为R3的喷嘴253将复合材料填充到开口213中直至底部(图15A)。然后,通过释放口直径为R2的喷嘴252将复合材料填充到开口213中直至中部(图15B)。再接着,通过释放口直径为R1的喷嘴251将复合材料填充到开口213中直至顶部(图15C)。根据该方法,通过释放复合材料填充开口可形成平面导电层。这样,具有高长宽比开口的绝缘体212可在不产生空隙的情况下具有平面布线。

如上所述,用于形成薄膜或布线的液滴释放系统包括用于输入表示薄膜图案的数据的输入工具;用于设定喷嘴移动路径以释放含形成薄膜的材料的复合材料的设定工具;用于检测形成于衬底上的对齐标记的成像工具;以及用于控制喷嘴移动路径的控制工具。因此,在液滴释放过程中需要精确控制喷嘴或衬底移动路径。通过在计算机中安装控制复合材料释放条件的程序以便控制液滴释放系统,可以精确地控制条件,例如衬底或喷嘴的移动速度、释放量、喷射距离、喷射速度、释放气氛、释放温度、释放湿度、衬底的加热温度等等。

因此,可以在预定的部位以较短的生产时间精确和高通量地制造预定宽度、厚度和形状的薄膜或布线。而且,可以提高生产产量,包括:利用薄膜或布线制成的半导体元件,如TFT;利用半导体元件制造的发光装置,如液晶显示器或有机电致发光显示器;LSI或类似物。尤其是,根据本发明,可在任何部位形成薄膜或布线,并可控制图案的宽度、厚度和形状。因此,可以低成本和高产量地制造大小在1×1m或以上或其两三倍大的大面积半导体衬底。

工业实用性

根据本发明,通过上述方法形成源极区和漏极区,用作沟道区的部分被用作沟道保护膜的绝缘膜所覆盖,从而形成岛形半导体膜。因此,由于不需要光刻胶掩模,可以简化工艺过程。如上所述,本发明的一方面在于提供形成半导体元件的新手段,其结合了利用源电极和漏电极金属掩模去除单一导电性半导体膜的方法,和用于形成沟道保护膜以防止沟道区移动的专用于沟道保护型的方法。根据上述构造可以只使用源电极和漏电极金属掩模而不用任何光刻胶掩模来制造半导体元件。因此,半导体元件及制造该半导体元件的方法适用于提供最佳的构造以及具有适当条件通过液滴释放法有效制成的工艺。

Claims (25)

1.一种电致发光显示器,所述电致发光显示器包括:

形成于衬底整个表面上的包含氧化钛的层;

形成于所述包含氧化钛的层上的门电极层;

与门电极层顶表面和包含氧化钛的层的顶表面接触形成的门板绝缘膜;

形成于所述门极绝缘膜上的半导体膜;

形成于所述半导体膜上的一对n型杂质区;

插在该对n型杂质区之间并形成于所述半导体膜一部分上的绝缘膜;

形成于该对n型杂质区上的导电层;和

与所述导电层电连接的像素电极;

其中所述绝缘膜与所述导电层接触;

其中所述绝缘膜被形成为具有叠层结构;且

其中所述门电极层由透明导电膜形成。

2.一种电致发光显示器,所述电致发光显示器包括:

形成于衬底整个表面上的包含氧化钛的层;

形成于所述包含氧化钛的层上的门电极层;

与门电极层顶表面和包含氧化钛的层的顶表面接触形成的门极绝缘膜;

形成于所述门极绝缘膜上的半导体膜;

形成于所述半导体膜上的一对n型杂质区;

插在该对n型杂质区之间并形成于所述半导体膜一部分上的厚度为100nm或更大的绝缘膜;

形成于该对n型杂质区上的导电层;和

与所述导电层电连接的像素电极;

其中所述绝缘膜与所述导电层接触;

其中所述绝缘膜被形成为具有叠层结构;且

其中所述门电极层由透明导电膜形成。

3.一种电致发光显示器,所述电致发光显示器包括:

形成于衬底整个表面上的包含氧化钛的层;

形成于所述包含氧化钛的层上的门电极层;

与门电极层顶表面和包含氧化钛的层的顶表面接触形成的门极绝缘膜;

形成于所述门极绝缘膜上的半导体膜;

形成于所述半导体膜上的一对n型杂质区;

插在该对n型杂质区之间并形成于所述半导体膜一部分上的绝缘膜;

形成于该对n型杂质区上的导电层;和

与所述导电层电连接的像素电极;

其中上面形成有绝缘膜的所述半导体膜中作为沟道区的部分的厚度小于其它半导体膜的厚度,并且上面形成有绝缘膜的所述半导体膜中作为沟道区的部分的厚度为10nm或更大;

其中所述绝缘膜与所述导电层接触;

其中所述绝缘膜被形成为具有叠层结构;且

其中所述门电极层由透明导电膜形成。

4.根据权利要求1至3中任一项所述的电致发光显示器,其中所述绝缘膜包括至少一种选自以下组的物质:聚酰亚胺、丙烯酸以及具有硅氧键合形成骨架并至少包括氢取代基或至少一种选自氟化物、烷基和芳烃基的取代基的物质。

5.根据权利要求1至3中任一项所述的电致发光显示器,其中所述电致发光显示器被包括在选自电视接收装置、电子书和手机的至少一种中。

6.一种制造电致发光显示器的方法,包括:

通过在衬底上释放含有第一导电材料的复合材料而形成门电极层;

在所述门电极层上形成门极绝缘膜;

在所述门极绝缘膜上形成第一半导体膜;

在所述第一半导体膜上形成含导电性类型杂质元素的第二半导体膜;

通过在所述含导电性类型杂质元素的第二半导体膜上释放含有第二导电材料的复合材料而形成源电极和漏电极;

利用源电极和漏电极作为掩模通过去除所述含导电性类型杂质元素的第二半导体膜而形成源极区和漏极区;

在形成源极区和漏极区之后,在所述第一半导体膜的一部分上形成绝缘膜;

利用所述源电极、漏电极和绝缘膜作为掩模通过去除第一半导体膜而形成岛形半导体膜;以及

形成与源电极和漏电极之一电连接的像素电极。

7.一种制造电致发光显示器的方法,包括:

在衬底的至少一部分上形成包含钛的层;

通过在包含钛的层上释放含有第一导电材料的复合材料而形成门电极层;

在所述门电极层上形成门极绝缘层;

在所述门极绝缘层上形成第一半导体膜;

在所述第一半导体膜上形成含导电性类型杂质元素的第二半导体膜;

通过在所述含导电性类型杂质元素的第二半导体膜上释放含有第二导电材料的复合材料而形成源电极和漏电极;

利用源电极和漏电极作为掩模通过去除所述含导电性类型杂质元素的第二半导体膜而形成源极区和漏极区;

在形成源极区和漏极区之后,在所述第一半导体膜的一部分上形成绝缘膜;

利用所述源电极、漏电极和绝缘膜作为掩模通过去除第一半导体膜而形成岛形半导体膜;以及

形成与源电极和漏电极之一电连接的像素电极。

8.根据权利要求6或7所述的制造电致发光显示器的方法,其中所述绝缘膜包括至少一种选自以下组的物质:聚酰亚胺、丙烯酸以及具有硅氧键合形成骨架并至少包括氢取代基或至少一种选自氟化物、烷基和芳烃基的取代基的物质。

9.根据权利要求6或7所述的制造电致发光显示器的方法,其中所述第一半导体膜的所述一部分包含沟道区。

10.根据权利要求7所述的制造电致发光显示器的方法,其中所述包含钛的层包含氧化钛。

11.根据权利要求6或7所述的制造电致发光显示器的方法,其中所述电致发光显示器被包括在选自电视接收装置、电子书和手机的至少一种中。

12.一种制造半导体元件的方法,所述方法包括:

在衬底的整个表面上形成包含氧化钛的层;

通过在所述包含氧化钛的层上释放含有氧化锌(ZnO)的复合材料而形成门电极层;

在所述门电极层上形成门极绝缘膜;和

在所述门极绝缘膜上形成半导体膜。

13.根据权利要求12的制造半导体元件的方法,所述方法包括:

在所述半导体膜上形成源极区和漏极区;

形成作为沟道保护膜的绝缘膜,以覆盖作为沟道区的部分;和

在不提供光刻胶掩模的情况下形成岛形半导体膜。

14.根据权利要求12所述的制造半导体元件的方法,其中所述半导体元件被包括在选自电视接收装置、电子书和手机的至少一种中。

15.根据权利要求12所述的制造半导体元件的方法,其中所述复合材料具有0.5至10μm的粒径。

16.根据权利要求12所述的制造半导体元件的方法,所述方法还包括:

将所述衬底浸在电镀溶液中。

17.根据权利要求12所述的制造半导体元件的方法,所述方法还包括:

在释放所述复合材料之前,对至少将提供门电极层的部分进行等离子处理。

18.一种制造半导体元件的方法,所述方法包括:

在衬底的整个表面上形成包含氧化钛的层;

通过在所述包含氧化钛的层上释放含有氧化镓锌(GZO)的复合材料而形成门电极层;

在所述门电极层上形成门极绝缘膜;和

在所述门极绝缘膜上形成半导体膜。

19.根据权利要求18所述的制造半导体元件的方法,所述方法还包括:

在所述半导体膜上形成源极区和漏极区;

形成作为沟道保护膜的绝缘膜,以覆盖作为沟道区的部分;和

在不提供光刻胶掩模的情况下形成岛形半导体膜。

20.根据权利要求18所述的制造半导体元件的方法,其中所述半导体元件被包括在选自电视接收装置、电子书和手机的至少一种中。

21.根据权利要求18所述的制造半导体元件的方法,其中所述复合材料具有0.5至10μm的粒径。

22.根据权利要求18所述的制造半导体元件的方法,所述方法还包括:

将所述衬底浸在电镀溶液中。

23.根据权利要求18所述的制造半导体元件的方法,所述方法还包括:

在释放所述复合材料之前,对至少将提供门电极层的部分进行等离子处理。

24.一种制造半导体元件的方法,所述方法包括:

形成包括作为沟道区的部分的半导体膜;

在所述半导体膜上形成源电极和漏电极;

在形成源电极和漏电极之后,通过液滴释放形成作为沟道保护膜的绝缘膜,以覆盖所述作为沟道区的部分;和

使用所述源电极、所述漏电极和所述绝缘膜的掩模形成岛形半导体膜。

25.根据权利要求24所述的制造半导体元件的方法,其中所述半导体元件被包括在选自电视接收装置、电子书和手机的至少一种中。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003-386021 | 2003-11-14 | ||

| JP2003386021 | 2003-11-14 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN200480040428.3A Division CN1914737B (zh) | 2003-11-14 | 2004-11-05 | 半导体元件及其制造方法和液晶显示器及其制造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN101853809A CN101853809A (zh) | 2010-10-06 |

| CN101853809B true CN101853809B (zh) | 2013-01-02 |

Family

ID=34587388

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201010167923.8A Expired - Fee Related CN101853809B (zh) | 2003-11-14 | 2004-11-05 | 半导体元件及其制造方法和液晶显示器及其制造方法 |

| CN200480040428.3A Expired - Fee Related CN1914737B (zh) | 2003-11-14 | 2004-11-05 | 半导体元件及其制造方法和液晶显示器及其制造方法 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN200480040428.3A Expired - Fee Related CN1914737B (zh) | 2003-11-14 | 2004-11-05 | 半导体元件及其制造方法和液晶显示器及其制造方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US8053780B2 (zh) |

| JP (1) | JP4667012B2 (zh) |

| KR (2) | KR101135063B1 (zh) |

| CN (2) | CN101853809B (zh) |

| TW (1) | TWI356496B (zh) |

| WO (1) | WO2005048354A1 (zh) |

Families Citing this family (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8884845B2 (en) * | 2003-10-28 | 2014-11-11 | Semiconductor Energy Laboratory Co., Ltd. | Display device and telecommunication system |

| WO2005048222A1 (en) * | 2003-11-14 | 2005-05-26 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting display device, method for manufacturing the same, and tv set |

| US7598129B2 (en) * | 2003-11-14 | 2009-10-06 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device and method for manufacturing the same |

| CN101853809B (zh) * | 2003-11-14 | 2013-01-02 | 株式会社半导体能源研究所 | 半导体元件及其制造方法和液晶显示器及其制造方法 |

| KR20060064264A (ko) * | 2004-12-08 | 2006-06-13 | 삼성전자주식회사 | 박막 트랜지스터 표시판 및 그 제조 방법 |

| JP4438685B2 (ja) * | 2005-05-23 | 2010-03-24 | セイコーエプソン株式会社 | 透明導電膜とその形成方法、電気光学装置、及び電子機器 |

| JP2006330418A (ja) | 2005-05-27 | 2006-12-07 | Seiko Epson Corp | 画素電極とその形成方法、電気光学装置、及び電子機器 |

| US7745989B2 (en) | 2005-06-30 | 2010-06-29 | Semiconductor Energy Laboratory Co., Ltd | Light emitting element, light emitting device, and electronic apparatus |