CN1065090C - 自适应时钟恢复的方法和装置 - Google Patents

自适应时钟恢复的方法和装置 Download PDFInfo

- Publication number

- CN1065090C CN1065090C CN94104632XA CN94104632A CN1065090C CN 1065090 C CN1065090 C CN 1065090C CN 94104632X A CN94104632X A CN 94104632XA CN 94104632 A CN94104632 A CN 94104632A CN 1065090 C CN1065090 C CN 1065090C

- Authority

- CN

- China

- Prior art keywords

- clock frequency

- line clock

- deviation

- frequency

- clock

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/02—Speed or phase control by the received code signals, the signals containing no special synchronisation information

- H04L7/033—Speed or phase control by the received code signals, the signals containing no special synchronisation information using the transitions of the received signal to control the phase of the synchronising-signal-generating means, e.g. using a phase-locked loop

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N21/00—Selective content distribution, e.g. interactive television or video on demand [VOD]

- H04N21/40—Client devices specifically adapted for the reception of or interaction with content, e.g. set-top-box [STB]; Operations thereof

- H04N21/43—Processing of content or additional data, e.g. demultiplexing additional data from a digital video stream; Elementary client operations, e.g. monitoring of home network or synchronising decoder's clock; Client middleware

- H04N21/4302—Content synchronisation processes, e.g. decoder synchronisation

- H04N21/4305—Synchronising client clock from received content stream, e.g. locking decoder clock with encoder clock, extraction of the PCR packets

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K5/13—Arrangements having a single output and transforming input signals into pulses delivered at desired time intervals

- H03K5/135—Arrangements having a single output and transforming input signals into pulses delivered at desired time intervals by the use of time reference signals, e.g. clock signals

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04J—MULTIPLEX COMMUNICATION

- H04J3/00—Time-division multiplex systems

- H04J3/02—Details

- H04J3/06—Synchronising arrangements

- H04J3/062—Synchronisation of signals having the same nominal but fluctuating bit rates, e.g. using buffers

- H04J3/0632—Synchronisation of packets and cells, e.g. transmission of voice via a packet network, circuit emulation service [CES]

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/54—Store-and-forward switching systems

- H04L12/56—Packet switching systems

- H04L12/5601—Transfer mode dependent, e.g. ATM

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N21/00—Selective content distribution, e.g. interactive television or video on demand [VOD]

- H04N21/60—Network structure or processes for video distribution between server and client or between remote clients; Control signalling between clients, server and network components; Transmission of management data between server and client, e.g. sending from server to client commands for recording incoming content stream; Communication details between server and client

- H04N21/63—Control signaling related to video distribution between client, server and network components; Network processes for video distribution between server and clients or between remote clients, e.g. transmitting basic layer and enhancement layers over different transmission paths, setting up a peer-to-peer communication via Internet between remote STB's; Communication protocols; Addressing

- H04N21/643—Communication protocols

- H04N21/64307—ATM

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04Q—SELECTING

- H04Q11/00—Selecting arrangements for multiplex systems

- H04Q11/04—Selecting arrangements for multiplex systems for time-division multiplexing

- H04Q11/0428—Integrated services digital network, i.e. systems for transmission of different types of digitised signals, e.g. speech, data, telecentral, television signals

- H04Q11/0478—Provisions for broadband connections

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/54—Store-and-forward switching systems

- H04L12/56—Packet switching systems

- H04L12/5601—Transfer mode dependent, e.g. ATM

- H04L2012/5672—Multiplexing, e.g. coding, scrambling

- H04L2012/5674—Synchronisation, timing recovery or alignment

Abstract

自适应时钟恢复电路从诸如异步传递方式(ATM)单元流之类一个异步的数据包流中导出同步时钟。连续监测存储在FIFO存储器中的信息量值的偏差,在微处理器的控制下以多种方式调整称为自适应线路时钟频率的同步时钟频率。调整是根据监测到的偏差增加状态作出的。调整是开环式的,且不需根据监测到的偏差来连续调整自适应线路时钟频率。与常规的锁相环路相比,阻尼效应好,可达到正确的频率后无频率摆动现象。

Description

本发明涉及通信系统。

近年来,业已研制出许多电话、图像和数据通信系统,将数字数据流编码成短的包或单元(cell)来取代采用同步传输。对于这种包式传输和交换技术派生出的世界性标准。称为“异步传递方式(ATM)”。虽然网络正在向ATM传输发展,但对于现今的同步交换和传输系统以及对于端点终端设备来说,都需要有接口。话音和图像信道总是需要恒定比特率的、同步的接口。从ATM或别的包式传输转换到恒定比特率同步系统的处理基本上需要两个步骤。第一步是提取出携载同步比特流的单元有效负载数据,将它存入一个先进先出(FIFO)存储器,该FIFO起缓冲存储器的作用,对突发单元的到达予以平滑。第二步是根据平均的数据到达比特率来恢复或导出一个时钟,并利用导出的时钟来对FIFO的数据输出确定节拍,再按节拍进入一个传输接口电路进行传输。从到达的单元/包流的数据速率中导出一个精确时钟速率的过程,称之为自适应时钟恢复。

ATM单元流在其单元速率方面经常具有短期变动突发性,对于某些ATM系统来说,变动期的时间量级为1毫秒。所导出的(自适应的)时钟速率必须稳定,典型的稳定值必须是百万分之几(ppm)秒;而就长时期来说,必须精确地跟踪(数据)源速率。对于不同的系统和不同的应用场合,在要求上有较大的差异。在确定平均进钟速率方面,基础性的技术是在一段时期内对到达的ATM单元数目进行积分。长的积分时间可用于产生低抖动、窄频带的时钟输出。然而,如果在这种场合下采用“通常的”锁相环路(PLL),例如这里所描述的电路配置210(图10),则比较长的积分时间将导致许多稳定性问题。积分时间与PLL控制环路中的反馈延时直接有关系,该反馈延时会使闭环控制系统有不稳定的趋势。此外,自适应时钟的转换速率(slew rate)会导致更多的反馈延时,对它必须加以限制。阻尼因数将显著地造成慢响应和不稳定运行。在“通常的”PLL环路中应用相位超前或多极点电路来控制阻尼是不实际的,因为对于在短时间上导出所需的相位超前信息来说,单元流有着太多的抖动。另有一条途径来说明这一点,即输入信号相位/频率信息的信噪比使得“通常的”PLL中不便于应用双极点滤波器。在这种场合下,一个(极其)窄带的PLL中若不采用多极点滤波器,便不能够将阻尼因数有效地调整到能提供稳定的工作。已经发现,具有足够增益和窄带特性的“通常的”PLL会振荡。

除了要解决上面所述的阻尼响应问题之外,自适应时钟恢复电路还应当:(1)从突发的ATM输入流中得出一个低抖动(窄带)的时钟;(2)具有良好的或近乎理想的阻尼稳定性;(3)具有快速响应,它仅受防抖动所必需的积分的限制;(4)具有足够增益(FIFO电平控制)来满足时钟跟踪和漂移规范;(5)具有受控的时钟转换率;(6)保持一个精确的抖动补偿延时(缓冲FIFO存储器排队电平);(7)可调整参数以适合于某种应用范围和需求范围。

鉴于上面的情况,本技术领域内需求一种改进的电路结构,用于从异步数据包流中恢复出同步时钟,它不象“通常的”锁相环路(PLL)结构中那样,并不依赖于用闭环调整来恢复出同步时钟频率。

为了实现以上目的,本发明提供了一种在一个电路配置中使用的方法,该电路配置包括:接收装置,用以接收异步的、数据包化的信息;存储装置,用以存储上述接收的信息;发送装置,响应一个自适应线路时钟频率,在一个同步的电路上发送上述存储的信息;该方法,其特征在于包括以下步骤:连续监测存储在所述存储装置中的信息的量值与一个标称值的偏差;检测所述监测到的偏差增加的状态;根据所述检测到的增加状态,调整所述自适应线路时钟频率,使所述自适应线路时钟频率过校正,直至所述监测到的偏差开始减小。

本发明还提供了一种在一个电路配置中使用的方法,该电路配置包括:接收装置,用以接收异步的、数据包化的信息;存储装置,用以存储所述接收的信息;发送装置,响应一个自适应线路时钟频率,在一个同步的电路上发送所述存储的信息;

该方法其特征在于包括以下步骤:连续监测存储在所述存储装置中的信息的量值与一个标称值的偏差;对所述监测到的偏差增加状态进行检测;根据所述检测到的增加状态,调整所述自适应线路时钟频率,但并不依据所述监测到的偏差连续地调整所述自适应线路时钟频率。

本发明还提供了一种在一个电路配置中使用的方法,该电路配置包括:接收装置,用以接收异步的、数据包化的信息;存储装置,用以存储所述接收的信息;发送装置,响应一个自适应线路时钟频率,在一个同步的电路上发送所述存储的信息;该方法其特征在于包括以下步骤:连续监测存储在所述存储装置中的信息的量值与一个标称值的偏差;连续地确定视在源频率;对所述监测到的偏差增加状态进行检测;响应所述检测到的增加状态,部分地根据所述连续地确定的视在源频率来调整所述自适应线路时钟频率。

本发明还提供了一种在一个电路配置中使用的方法,该电路配置包括:接收装置,用以接收异步的、数据包化的信息;存储装置,用以存储所述接收的信息;发送装置,响应一个自适应线路时钟频率,在一个同步的电路上发送所述存储的信息;该方法其特征在于,包括以下步骤:连续监测存储在所述存储装置中的信息的量值与一个标称值的偏差;根据所述监测到的偏差和所述自适应线路时钟频率,连续地确定视在源频率以用于调整所述自适应线路时钟频率。

本发明还提供了一种在一个电路配置中使用的方法,该电路配置包括:接收装置,用以接收异步的、数据包化的信息;存储装置,用以存储所述接收的信息;发送装置,响应一个自适应线路时钟频率,在一个同步的电路上发送所述存储的信息;该方法其特征在于,包括以下步骤:连续监测存储在所述存储装置中的信息的量值与一个标称值的偏差;对所述监测得的偏差增加状态进行检测;响应所述检测到的增加状态,对所述自适应线路时钟频率实行开环调整。

本发明还提供了一种自适应时钟恢复装置,其特征在于包括:接收装置,用以接收异步的、数据包化的信息;存储装置,用以存储所述接收的信息;发送装置,响应一个适应线路时钟频率,在一个同步的电路上发送所述存储的信息;微处理器装置,用于(a)对所述存储装置中存储的信息的量值与一个标称值的偏差连续地进行监测;(b)对所述监测到的偏差增加状态进行检测;(c)响应所述检测到的增加状态,以多种模式调整所述自适应线路时钟频率。

按照本发明的一个典型实施例,这种需求得以满足,并达到技术先进;这里,存储在先进先出存储器例如是FIFO(图1)中的信息量值的偏离被连续地监测,并且这里的同步时钟频率(在此称作自适应线路时钟频率)受到调整,在一个处理器例如微处理器29(图1)的控制下可用多种模式作方便的调整。该调整是根据所监测的偏离中检测到的偏离增加状态作出的。重要点在于,所作的调整都是开环调整,不必以所监测的偏离为基础来连续地调整自适应时钟频率。与“通常的”PLL结构相比较,阻尼实质上是增加了,这是因为,开环调整可得到具有完善的或近乎完善的非周期性阻尼也即无振荡状态的快速频率校正;而在闭环结构中,频率校正之后会跟随有阻尼振荡。

本发明的方法被应用在一种包括如下设备的一种电路安排一个:一个异步的、数据包式信息接收器,一个诸如FIFO之类的存储器来存储接收到的数据包式信息,以及一个发送器,用以根据自适应线路时钟频率在一个同步电路上发送出存储的信息。该方法包括连续地监测存储器中存储的信息量值相对于一个标称值的偏离。当检测到所监测的偏离处于增加状态时,电路结构按多种模式来调整自适应线路时钟频率。

示例性地说明,在第一模式(斜坡-模式1)中,自适应线路时钟频率被过校正,直至所监测到的偏离开始减小。在第二模式(斜坡-模式2或4)中,自适应线路时钟频率保持恒定,直至所监测到的偏离减小到一个预定的阈值。该示例性的方法还包括连续地确定一个视在源频率。在第三模式(斜坡-模式3或5)中,使自适应线路时钟频率改变,直至自适应线路时钟频率等于视在源频率。该视在源频率是根据所监测到的偏离和自适应线路时钟频率确定的。在斜坡-模式1到斜坡-模式5中所作的调整,都是开环调整,也即并不是基于所监测到的偏离来连续地调整自适应线路时钟频率而实现调整的。将监测到的偏离进行积分以平滑掉数据抖动。为使处理时间最小,在算法中不采用乘法。大部分的除法是以2的幂作除数,它们被汇编为左移操作。

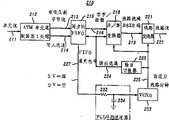

图1示出本发明的一个示例性自适应时钟恢复电路图;

图2和图3示出图1电路配置的响应曲线图;

图4至图6示出图1电路配置中所包括的微处理器执行程序的软件流程图;

图7至图9示出图1电路配置的附加响应曲线图;

图10示出现有技术中“常规的”锁相环电路图。

图1是一个示例的自适应时钟恢复电路10的电路图,该电路在一个接口上使用,它从线路11上的155Mb/s(兆比特/秒)的异步传递模式(ATM)单元流接口到线路22上同步的DS1、1.544Mb/s的恒定比特率电路中。(其它实例的同步数据率包括DS3=44.736Mb/s、CEPT1=2.048Mb/s、CEPT3=34.368Mb/s。)如图1所示,电路10包括有用于将信息从ATM单元流传送到同步电路的硬件。在另一方向上-从同步电路去往ATM单元流-传送信息所需的硬件在当前的叙述中并不重要,所以图1中未示出。由于线路11上输入(incoming)单元流的突发和异步性质,故而在线路22上同步地传送信息所需的时钟想要应用线路11单元流中的边沿信息或过渡信息来导出是做不到的。线路11上的每个ATM单元是53字节的数据包,包括5字节的首标、1字节的适配层和47字节的可用信息有效负载。每个ATM单元代表155Mb/s上的一个53字节字符组;各单元异步地到达,一般有比较长的开区间例如8至243毫秒间隔着。电路12执行CCITT适配层1处理,包括去除5字节的单元首标和1字节的适配层,并应用线路14上的写入选通径由字节母线13来控制47字节有效负载去写入一个先进先出(FIFO)存储器15。FIFO15例如是集成器件技术公司(IDT)的存储量达4096个8比特字节的72241,该存储量完全足以存储在线路22上积累着等候传输的全部字节数目。FIFO15与一个例如Fairchild公司的F579增/减计数器25协同工作,该增/减计数器25在任一时刻计数FIFO15中存储的字节数目。从电路12上每次给FIFO15写入一个字节时,线路14上的写入选通使计数器25增加1。从FIFO15中每次读出一个字节时,线路24上的读出选通使计数器25减少1。

在上述作了说明的、从线路35上导出的自适应线路时钟,用来控制从FIFO15向DS1也即线路22上的同步电路传输字节。在本实施例中,线路35上的时钟频率可在1.544×106b/s-130ppm到1.544×106b/s+130ppm之间变化。对于同步电路DS1来说,这个变动范围是容许的。线路35上的这一自适应线路时钟频率用来操作一个例如仙童公司的F323并/串变换器18和一个线路发送器21。该线路时钟频率由一个例如Fairchild公司的F161A计数器23除以8,在线路24上得到的字节时钟用作读出选通,以便经由字节母线16、并/串变换器18和线路19从FIFO15实现有效负载信息的字节读出,以便由线路发送器21在线路22上作为一个DS1电路进行传输。发送器21将一个B8ZS码插入线路流中,以防止有7个以上接连的0比特在线路22上传送出。如前面所说明,线路24上的读出选通还用于使计数器25递减计数。

微处理器29例如是Motorola公司的68070,对于在线路35上导出自适应线路时钟来说,它是电路结构10中一个重要的部分。根据线路28上接收到的1KHz积分时间定时,微处理器29每毫秒一次地执行一个程序(图4至图6的流程图)。程序的执行要用250毫秒左右的时间。程序输入数据是经由16比特数据母线27从计数器25上读出的FIFO填充电平。该FIFO填充电平是在0与4095之间的一个12比特数目,它代表在FIFO15中存储的字节数目。程序输出数据是一个“积分器(integrator)变量,它经由母线27传送到一个数/模(D/A)转换器30,例如模拟器件公司的8412,该D/A转换器30通过线路31连接5V基准电压;线路32上的D/A转换器输出电压在0V至5V间变化。D/A转换器30通过线路32向一个压挖晶体振荡器(VCXO)33提供控制用输入信号,该VCXO33例如是AT&T公司的S型VCXO。如果D/A转换器30在线路32上产生出5V电压作为对VCXO33的控制输入,则VCXO33会在线路35上传送出一个频率为1.544Mb/s+200ppm的自适应线路时钟。当D/A转换器30在线路32上产生出2.5V电压时,VCXO33传送出1.544Mb/s的频率。而若D/A转换器在线路32上给出OV电压时,VCXO33将传送出1.544Mb/s-200ppm的频率。在本实施例中,线路32上的控制用输入信号并非在0V与5V之间变化;其电压的变化是使线路35上的自适应时钟频率被控制在1.544Mb/s-130ppm与1.544Mb/s+130ppm之间。线路32包括一个防混叠滤波器(图1中未示出),用来除去线路32上小的阶梯函数效应。由于不需在线路35上以高速率转换时钟频率,所以防混叠滤波器具有较大的RC时间常数,例如R=2.2KΩ,C=33μF。

时基抖动通常是模拟通信线路失真的一种类型,它是由信号相对于基准定时位置有变动造成的,将会导致数据传输误差,尤其是在高速传输时。这种变动可以是幅度上的、时间上的、频率上的或相位上的。在当前的应用中,抖动更具体地指的是期望的(定期的)单元流到达时间与实际的单元流到达时间之间的差别。电路结构10是按线路11上的入局单元流有最坏情况的抖动设计的,即从DS3速率时的0.3毫秒到DS1速率时的3毫秒。在DS3之类高速率上的限制因素,是FIFO的规模。抖动产生的原因有:1)在不同的等时ATM源之间由速率差拍造成的群聚效应;和/或2)在一个ATM交换系统中由多径造成的统计排队延时,它们被其它业务暂时地中断。一般,群聚效应比统计排队引起的延时量小;群聚延时是有规律地发生的。

图2和图3是用来帮助理解电路配置10的工作的响应曲线图。图2和图3中,在90秒时间段上画出了三个程序变量“fill-level-err”(填充-电平-误差)“integrator”(积分器)和“integrator-float”(积分器-浮动)。变量“填充-电平-误差”代表FIFO中存储的信息量值对一个标称值的偏离。图2是对初始源时钟误差的响应(FIFO过填充状态),初始状态是自适应时钟频率(“积分器”)比源时钟慢60ppm。所以,FIFO15中存储的字节数目在标称值之上增加到最大值30字节(FIFO过填充状态)。当FIFO15中的字节数目开始增加时,电路10被置于斜坡-模式1,自适应时钟频率(“积分器”)增加(过校正)到超过源时钟50ppm的一个点上。当FIFO填充电平误差(“fill-level-err”)增加到30字节时,便减少一个规定的量值(“DEF-pole(极点)-2D”=5字节),电路10被置于ramp-mode(斜坡-模式)4,自适应时钟频率(“积分器”)恒定地保持于源时钟之上50ppm,以对FIFO15给出时间来清除些+30字节。当FIFO填充电平误差减少到一个预定的阈值(“DEF-ramp-db”=10字节)时,电路配置、10被置于斜坡-模式5,自适应时钟频率(“积分器”)线性地下降(其速率比例于前面所需的过校正量值)到一个值,它等于视在源频率(“integrator-float”(“积分器-浮动”)),然后电路配置10被置于ramp-mode(斜坡-模式)0。快速的线性下降产生出减小了长度的校正周期。自适应时钟频率(“积分器”)的下降到0是在离坐标源点正好不到8秒时发生的。(程序还包括防护性校验,如果视在源频率(“积分器-浮动”)并非可靠地估值,则程序将停止自适应时钟频率(“积分器”)的下降。)需要指出,这里不存在进一步的振荡-这可称为完善的非周期性阻尼。“填充-电平-误差”和“积分器-浮动”两条曲线均随时间逐渐下降(图2中示出90秒的总时间)。在斜坡-模式0中,程序包括了很慢的校正,它能在1.0-1.5分钟内将FIFO填充电平误差校正为几个字节,使得自适应时种频率(“积分器”)能准确地等于源频率。

图3示出对初始源时钟误差的响应(FIFO欠填充状态),初始状态是自适应时钟频率(“积分器”)比源时钟快60ppm。所以,FIFO15中存储的字节数目减少到比标称值低达30字节处(FIFO欠填充状态)。当FIFO15中的字节数目开始减少时,电路配置10被置于斜坡-模式1,自适应时钟频率(“积分器”)下降到低于源时钟50ppm的一个点上。当FIFO填充电平误差(“填充-电平-误差”)下降到-30字节时,便增加一个规定的量值(“DEF-pole(极点)-2D”=5字节),电路配置10被置于斜坡-模式2,自适应时钟频率保持恒定,保持在源时钟之下50ppm,以对FIFO15给出时间来存储附加的字节。当FIFO填充电平误差改变到标称值之下一个预定的阈值(“DEF-斜坡-db”=10字节)时,电路配置10被置于斜坡-模式3,自适应时钟频率(“积分器”)线性地增加(其速率比例于前面所需的过校正量值)到一个值,它等于视在源频率(“积分器-浮动”),然后电路配置10置于斜坡-模式0。快速的线性增加产生出减小了长度的校正周期。自适应时钟频率(“积分器”)的增加到0是在离坐标原点正好不到8秒时发生的。(程序还包括防护性校验,如果视在源频率(“积分器-浮动”)并非可靠地估值,则程序停止自适应时钟频率(“积分器”)的增加。)需要指出,这里不存在进一步的振荡,即具有完善的非周期性阻尼。“填充-电平-误差”和“积分器-浮动”两条曲线随时间逐渐上升(图3中示出90秒的总时间)。在斜坡-模式0中,程序包括了很慢地校正,它能在1.0-1.5分钟内将FIFO填充电平误差校正为几个字节,使得自适应时钟频率(“积分器”)能准确地等于源频率。

FIFO15的标称填充电平为7个ATM单元,或即7×47=329字节。FIFO15中存储的ATM单元最大数目是60单元或即60×47=2820字节。标称填充电平是在对付抖动上和对付起动所致偏差(初始时钟捕捉)上所需的最小值,因而有着最小延时。对视在源频率(“积分器-浮动”)的估值应用了自适应时钟频率(“积分器”)和FIFO填充电平误差(“填充-电平-误差”)两者的加权组合。实现这估值主要是去控制自适应时钟频率(“积分器”)的阻尼。需要指出,视在源频率(“积分器-浮动”)比之自适应时钟频率(“积分器”)变动得更慢。这部分地是基于如此的假定,即源时钟频率的变动恰是十分平缓的。自适应时钟频率(“积分器”)用来校正FIFO偏差,此类偏差起因于:1)与源频率的失配;2)在ATM网络中数据的得益或损失。FIFO填充电平误差(“填充-电平-误差”)与自适应时钟频率(“积分器”)协同地起响应。

自适应时钟恢复方法是在微处理器29(图1)中执行的一个数字信号处理程序,去控制可变的晶体振荡器(VCXO)33。该程序以1KHz的取样频率执行。自适应时钟提供“通常的”PLL功能,但具有不能由“通常的”PLL精确跟踪的输入信号条件。在自适应时钟恢复电路配置10中,FIFO15的填充电平对程序提供输入。如果对突发的数据流能施加以充分的积分(截止频率为1Hz左右的低通滤波器),则能从突发的数据流中确定出准确的源时钟速率。采用数字积分法,容易做出这低通滤波器。滤波器/积分时间由输入抖动、锁定时间、时钟抖动和漂移要求等来确定。

实现自适应时钟恢复时的困难点在于,以良好的阻尼和稳定性来作出窄带滤波器。“通常的”PLL在时钟校正与检测得的响应之间有很大的相位/时间滞后。FIFO在电路中的作用象一个弹簧,对校正用反馈管加以延时。FIFO中的抖动使电路不能识别出小的校正。长时间常数的积分滤波器缓解了这种环路延时问题。另外,不象“通常的”PLL,电路结构10中的FIFO15能记忆过去的时钟误差和丢失的数据。这些过去的状态必须由时钟摆动的过校正来予以校正,以使FIFO正常化。在这种类型的应用中,“通常的”PLL超前/滞后阻尼滤波器是无效的。

本示例性实施例的算法,开发出来用于自适应时钟恢复和解决上面说明的环路阻尼与稳定性问题。首先,确定出三个输入信号,它们是视在源频率、FIFO填充电平误差和误差方向(增加/减少)。然后,对当前的时钟频率误差和FIFO电平状态计算校正量。这种校正是按照一个开环的、按比例地斜坡升和斜坡降的VCXO33控制信号来执行。对校正的速率(斜坡斜率)、幅度和时间作出计算以便校正误差,而不需要自FIFO电平误差来的连续的反馈;这称作开环调整。(斜坡-模式1、2、3、4、5对应于开环调整。)在校正周期的终端,FIFO的电平和时钟一般处在它们的静态零点上,即使时钟在校正周期中坡斜得过陡也是这样。当精确地确定出误差时,总的阻尼响应是非周期性的(无下冲或上冲)。

对FIFO电平误差信号进行积分,以提供出对数据抖动附加的滤波。这一积分时间是个重要的参数,决定了自适应时钟的部分阻尼响应。由于自适应时钟斜坡升/降的控制判决是在FIFO电平误差数据的模糊逻辑上作出的,所以在自适应时钟恢复电路配置10变到失锁之前,应用若干个探索性检验和校正来检测和防止错误的时钟斜坡变动。

在模拟运行中,对于1.5至45MHz的时钟速率已经达到了优良的时钟稳定性、阻尼响应和FIFO电平控制。在时钟输出中完全不存在抖动。

对于有着大的抖动的输入数据流,要想从其中直接导出具有极小抖动的精确时钟时,示例的自适应时钟恢复方法对那样的系统是很有用的。对于输入信号中伴随着噪声,在控制响应上有大的滞后的其它一些系统,该方法也很有用。对此方法可加以比例化和协调化,以在宽广的范围内应用。

图4至图6示出由微处理器29执行的自适应时钟程序所用的软件流程图,程序的作用和算法将在这里说明。请注意,图4至图6中的程序框参考在后面列出的程序文本中的具体代码行号。

自适应时钟程序在1毫秒时间间隔上执行。这一速率选择得能提供出匀滑的、4096步控制的VCXO,因而接近于模拟控制电路。程序可以用0.9至1.1毫秒范围内的平均执行间隔来运行,在这样的速率上对抖动变化并不敏感。重要的是应该知道,图4至图6的流程图及这里相应的叙述是说明在一段时间上程序的运行;它们示明了单个程序以上的程序执行。

可变的“clk-tic”(图4,框101)是个32比特计数器,在每个执行时间间隔计数值加1,在整个程序中它用作一个定时器。由定时时标的一个二-十进制变换来触发事件和过程算法,而定时时标是按一种协调参数作出规范的。例如,一个1秒事件的定时以二-十进制时标参数1024-1来实施,它给出1024个1ms“clk-tic”的时间。

程序只有一个输入量(框102),它是外部缓冲存储器FIFO15中的字节数目。从外部硬件增/减计数器25来的含有FIFO填充电平的一个读出值装入可变的“FIFO”。FIFO15必须容量足够大,能缓冲吸收最坏情况的单元延时,并加上时钟捕获时间期间供排队用的宽裕量。

由程序流程中的第一算法在变量“积分器-浮动”中产生一个值,依据积分器计数,该变量“积分器-浮动”总包括含有一个估值的原始频率,或者视在源频率。这一算法也可以在程序的终端放置和执行。

理想上,原始频率应当等于FIFO数据到达比特率,它即是视在源频率。在程序的静态或锁定状态(斜坡-模式0)中,“积分器-浮动”的值等于变量“积分器”。“积分器”变量提供出主(极点1)积分累加器功能,并直接控制VCXO33的频率。“积分器-浮动”的值被显现为“积分器”和“填充-电平-误差”中两值的加权和比例组合。参见程序文本中确切的逻辑。变量“积分器-浮动”是另一个积分累加器,它的积分时间常数大约是极点1变量“积分器”的两倍。在一个开环校正周期的终端,它达到其最终值,从而应等于“积分器”中的值。变量“积分器-浮动”不对“积分器”的较快的变化起响应。变量“积分器”较快地响应于源频率变化的超前校正,并且就这一个或者就数据损失使FIFO电平正常化。由“积分器”控制的VCXO33时钟也被过校正一小段时间,以在频率变化之后使FIFO15正常化。变量“积分器-浮动”不被过校正,但就在校正周期结束时,它达到其新的基线电平。主FIFO和时钟校正环路用“积分器-浮动”来确定在FIFO电平校正作出之后它返回到(或者向下坡斜到)何处。当时钟发生变化而仅使FIFO电平正常化之后,这个算法又使“积分器-浮动”返回到原来的原始源频率上。从图8中可以看到这一点。(其它传输电路中的误差状态会使得有数据加上或丢失,而源时钟频率方面没有变化。)

对产生出变量“积分器-浮动”的诸参数,是由画出“积分器”、“积分器-浮动”和“填充-电平-误差”的响应曲线,并将它们调整到得出填充-电平-误差和积分器(VCXO33频率)变量的最大阻尼(下冲/上冲最小或没有)来确定的。“积分器-浮动”达到其新的原始值,与“填充-电平-误差”的达到零相一致。示出这种交点的曲线示于图2和图3。

框103的算法连续地对视在源频率估值,以便在作出任一个开环时钟或FIFO电平调整之后,能使电路返回到正确的频率上。该算法用作整个电路方面阻尼因数的主要控制。

流程图中的下一个算法(框104)实现一种预积分或抖动平滑操作。它滤除掉出现在变量“FIFO”之内大部分的数据到达(FIFO填充电平)抖动。该算法的输出是一个称为“FIFO-浮动”的新变量。在每一个由参数“DEF-浮动-惯性(inertia)-时标(mask)”规定的周期内,“FIFO-浮动”跟踪“FIFO”1字节的数目。对于DS1速率的时钟实现,该参数适定于八进制37,每32毫秒它给出一个事件。“FIFO-浮动”中每32毫秒内1个数据字节的最大移动等同于DS1时钟的变化为162ppm/s。在这一处理中,超过162ppm的所有抖动变动都被平滑掉或弃置不顾。此种操作对实际的FIFO电平没有影响,而只影响由程序的其余部分处理的视在电平。该参数必须设定到这样的值,它能使视在的FIFO速率变化大于VCXO33的最大转换率,例如是该转换率的两倍。

框104的方法可预滤掉数据到达的抖动,并跟踪FIFO数据电平变动于额定的速率变化之下,单位为ppm/s。这方法免除了用前端FIFO来匀滑数据到达的抖动的需求。

下一个重要的程序语句(框105)使变量“填充-电平-误差”初始化,这是从“FIFO-浮动”中减去参数“DEF-正常(normal)-填充-电平”。变量“填充-电平-误差”是一个带符号的值,表明FIFO电平对预定标称值的偏离。在程序的其余部分中它用作开环误差信号。正的值指明FIFO电平在增加,VCXO33必须变化到一个较高的频率上来使之正常化。

下面的算法(框106和框107)通过计算出的时钟校正来产生主要控制状态以供该开环应用。

由框106的算法判定,将视行的“填充-电平-误差”与“旧(old)-填充-误差”中先前的误差状态相比较时,填充电平误差是否在减小。依靠仅对FIFO填充电平中的变化起响应以在这一检测中将滞迟作用组合进来,而这类变化是指超过参数“DEF-极点-2D”中额定字节的数目。这种滞迟作用减小了由余留在变量“填充-电平-误差”中的数据到达的抖动造成的错误检测之数目。然后,由填充电平误差是否在减小的检验(框106)判定自适应时钟变化的方向。对于FIFO欠填充状态,自适应时钟将处在比源时钟低的频率上(积分器值在中心频率点之下);对于过填充(正)状态,自适应时钟将处在比源时钟高的频率上(积分器值在中心频率点之上)。如果在前面的执行期间填充电平误差在减小,则除了将“旧-填充-误差”更新为“填充-电平-误差”中的当前误差之外,不发生其它作用。然而,如果“斜坡-模式”中先前的状态等于1(增加模式),则这一事件变为增加-减少的变化。

“增加-减少”事件有重要意义,因为它判定,自适应时钟VCXO33已超过“视在”源时钟频率。这一事件用来启动斜坡-模式2或4,它将会停止进一步(增加)的时钟校正,并保持住“积分器”中的视行频率。对于欠填充的FIFO15,变量“斜坡-模式”设定于状态2;对于过填充的FIFO15,变量“斜坡-模式”设定于状态4。变量“斜坡(ramp)-斜率(slope)”被初始化以控制这样的速率,即在此速率下时钟返回(斜坡降)到原始频率。(要回想到,时钟已过校正得使FIFO15正常化。)对存储于变量“斜坡-斜率”和“填充-误差-dx”中的斜坡斜率速率进行计算,成为由参数“DEF-div(除法)-X”确定的“填充-电平-误差”的一个分数率。斜坡降的斜率是与这一事件起始处FIFO电平误差成比例的。

框106的方法指出,VCXO时钟校正在何时等于视在源频率(数据所达速率)。框106的方法还计算出这样的速率,在此速率上时钟返回或即斜坡降(斜坡-斜率)到原始频率,并当达到原始频率的时候,FIFO填充误差也将达到零。

当填充误差减小的检验完成之后,程序进入填充误差增加的检验(框107)。增加的方向决定于旧-填充-误差与视行填充误差的比较。这个工作与减小的检验是一样的,只是旧的与新的倒换。对于增加的检验,旧的与新的填充-电平-误差之间的差别必须超过参数DEF-极点-2I。在对一个增加的事件作出响应之前,先要进行进一步的检验。如果斜坡-模式表明时钟斜坡-下降(状态3或5),或是填充误差处在空(null)误差(停滞带段(deadband))区域,则对增加的事件置之不顾。让这些检验通过,将斜坡-模式置于1,并将斜坡-斜率置于值“填充-误差-dx”。

参数“DEF-极点-2D”除了为增加-减少的检验提供滞迟作用外,还控制自适应时钟过冲的量值。过冲(过校正)的受控量用来在源时钟速率满足之后使FIFO15填充电平正常化。数值的确定依靠画出响应曲线,并调整到约75%的时钟过冲(源时钟频率与自适应时钟频率之间初始差别的75%过校正)。由过冲量确定使FIFO15正常化的时间。

框106和框107的方法能可靠地判定,在存在高的数据到达抖动的情况下,FIFO15电平误差是增加的或是减小的。框106的方法还控制使FIFO填充电平正常化所需的时钟过校正量值。

一旦处于增加的填充误差模式(斜坡-模式1),将每一时间段内斜坡-斜率中的校正量叠加到“积分器”的当前值上。需要指出,由于所需的时钟校正会是趋向较高的频率或是较低的频率(图6的框114),所以斜坡-斜率可能包含正的值或是负的值。这个代数和使积分器值斜升,将VCXO33频率驱动到这样的值,它满足并随后超过源频率。当超过视在源频率时,FIFO填充电平误差开始减小。它不象大多数连续反馈的闭环系统中那样,当误差减小时斜坡-斜率的速率并不逐渐减小。这种方法使误差收敛时间最小。过冲受斜坡-模式2至5的运行的控制。

框114(图6)的方法实现主要(极点1)积分作用。

框108(图5)是转移(斜坡-模式)语句,行号代码#208。时钟斜坡模式提供出保持、过校正和斜坡降等几种功能。模式2(转移语句中的事例2)保持于负的填充电平误差,它引出模式3以使斜坡降。模式4保持于正的填充电平误差,相应的斜坡降是模式5。斜坡-模式2和4由减小的填充误差检验算法调用(框106)。在减小的事件的开始(增加的误差转到减小的误差),自适应时钟VCXO33满足源时钟速率,然后超过源时钟速率一个受控的量值。初始时,FIFO15填充电平将脱离开其标称值,这是因为,当时钟速率正收敛时,在增加的误差模式时段内FIFO15填充电平获得或丢失数据。斜坡模式2和4(图5中的框109和框111)可使时钟过冲状态保持恒定,直至FIFO15填充电平向标称值收敛,满足参数“DEF-斜坡-db”中规定的阈值。这一参数设定于一个FIFO电平校正点,它给出时间供自适应时钟积分器值得以斜坡下降,并恰好当“填充-电平-误差”达到零时下降到原始(源)频率。各参数均设定正确后,所得结果是个非周期性响应(时钟过冲或下冲很小或者不存在),而“通常的”PLL其情况一般不是这样的。对于在源时钟与自适应时钟VCXO33之间有大范围初始频率差的情况,一般也能达到上面的结果。

如图5中所示,斜坡下降的“斜坡-模式”是斜坡-模式3(框110)和斜坡-模式5(框112)。当斜坡-模式3和5完成了斜坡-下降而到达“积分器-浮动”中的原始积分器值时,它们将斜坡-模式设定于0,并脱离开转移语句。斜坡-模式0是开环控制算法(斜坡-模式1-5)的静止状态。如果有完善的非周期性阻尼,自适应频率将与源频率协配,且FIFO将在标称电平上。如果余留的空(null)误差大于参数“DEF-停滞(dead)-带段(band)”,则由增加的误差检测算法启动一个新序列(框107)。当时钟不相同且FIFO填充电平脱离开标称值时,在电路启动期间内需要有一个以上的周期。这一点,可从图9中40秒上的二次校正周期看出。

框109和框111的方法是在FIFO电平调整好之前保持住过校正的自适应时钟状态。框110和框112的方法是使自适应时钟频率坡斜地下降,当FIFO填充误差趋近零时达到源频率。

斜坡-模式0是静止状态,当“填充-电平-误差”处于一个小的停滞带段范围内时,进入该斜坡-模式0。参数“DEF-停滞-带段”规定了斜坡-模式1-5的停滞带段。在DS1速率的场合下设定于8,它允许+/-8字节的空误差范围。斜坡-模式0(框113)对积分器值加上一个直接(闭环)反馈校正值,它在由参数“DEF-事例0-速率”规定的速率上加1或减1。校正速率非常低,该环路的自然频率约为1/60Hz。环路在自然环路频率上振荡,在短时期内“填充-电平-误差”的偏离通常不超过+/-2字节,而在60秒内平均为0字节。应当指出,自适应时钟频率的跟踪/漂移误差是与空误差上的FIFO填充电平误差有关联的。

框103(图4)的方法中在空误差点上加入一个量十分小的闭环反馈,以在其环路频率的一个周期内使FIFO填充一电平空误差减小到零。

自适应时钟程序的最后作用是将变量“积分器”的内容写入D/A转换器30,它控制VCXO33的频率(图6中框115)。这一作用将16比特的变量“积分器”标度给参数“DEF-VCXO-范围-因数”中规定的控制范围,然后将所标度的值偏称到VCXO33的中心频率点,它在参数“DS1-VCXO-DAC-中心”内规定出。这个被标度的和定中心的值写入到D/A转换器30的地址中,并且自适应程序返回到呼叫程序或中断电平。

对于有着大的抖动的输入数据流,要想从其中直接导出具有极小抖动的精确时钟时,该自适应时钟技术和算法对那样的系统是很有用的。对于输入信号中伴随着噪声,在控制响应上有大的滞后的系统,该方法也很有用。对此方法可加以比例化和协调化,以在宽广的范围内应用。

本实施例中所叙述的程序对于小规模式处理器中的执行速度来说是最佳的。一个约1MIP容量的16比特处理器可以并行地处理4个自适应时钟电路。它不使用乘法操作,许多算法产生出近似值来代替精确的计算。不过,可以加上一些计算来使协调的建立减至最小,并在宽广的运用状态下改善阻尼效应来达到非周期性响应。该程序表如下:

图7示出对瞬态误差的响应曲线FIFO15丢失数据1个单元有效负载或47字节),表明自适应时钟频率(“积分器”)相对于源时钟的时间曲线如FIFO填充电平误差(“填充-电平-误差”)的时间曲线。曲线表明电路配置10(图1)对一个瞬态误差的响应,该瞬态误差是FIFO丢失一个单元有效负载(47字节或47个8比特组)。填充电平误差曲线表明暂时的单元丢失及自适应时钟对此的响应-比源时钟低下60ppm。需要指出,这里有半个周期的过冲时间或阻尼稳定时间。电路配置10已作出最佳设计,使它对于跟踪源时钟变化比之对于瞬态数据误差提供出更好的阻尼特性。

图8示出初始FIFO误差(1单元有效负载或47字节)对初始源时钟无误差的响应曲线,表明自适应时钟频率(“积分器”)相对于源时钟的时间曲线、FIFO填充电平误差(“填充-电平-误差”)的时间曲线和视在源频率(“积分器-浮动”)的时间曲线。图8的情况与图7的类同,与图7的差别仅在于单元丢失在这里发生于起始的填充电平误差。此外,这里也画出了变量“积分器-浮动”的曲线。起始期或即时钟捕捉期得以大为减短,其方法是在自适应时钟算法启动之前,在起始时将FIFO电平初始化于“DEF-正常-填充-电平”值。这个工作也由微处理器29按下面的程序来完成。当电路不起作用时,读出选通24阻塞,线路发送器21传送出全1的置闲码(DS1的AIS信号)。当单元流的到达被检测到并稳定后,FIFO复位26,在一个紧密环路中立即监测填充-电平值(查询)。当填充电平等于“DEF-正常-填充-电平”减去超前偏置时,读出选通24启动,AIS信号被阻塞。超前偏置使微处理器29对读出选通24的启动提供出时间。可以调整到使该启动与填充电平达到“DEF-正常-填充-电平”相一致。

图9示出初始FIFO误差(1单元有效负载或47字节)对初始源时钟误差的响应曲线,表明自适应时钟频率(“积分器”)相对于源时钟的时间曲线、FIFO填充电平误差(“填充-电平-误差”)的时间曲线和视在源频率(“积分器-浮动”)的时间曲线。曲线表明了电路结构10对初始FIFO151单元有效负载(47字节)误差的响应以及对初始源时钟-70ppm误差的响应。图9中还示出在40秒上的一个二次校正周期。初始校正周期使时钟坡斜地下降到比实际源频率低几个ppm。这使得“填充-电平-误差”慢慢地向上滑移,并在40秒上有一个校正周期。斜坡-模式0也可以在空误差区内进行慢漂移校正,这可以从大约35秒处自适应时钟积分器收敛于近乎0来看出。在这种情况下,斜坡-模式0的校正显得太小和太迟。

在“通常的”PLL中,目的时钟速率由平均的单元流到达速率单独确定。相位/频率信息来自FIFO填充电平,如图1中所示,这是1988年10月10日理查德(Richard c.Lau)对T1S1.1提出的Bellcore论文“供ATM电路模拟用的一种时钟恢复方案”中提出的。由于这一技术不需要源电路中来的网络基准时钟和编码的时钟信息,所以一般公认是很有希望的。然而,正常也公认,当尝试进行实际设计时,就时钟收敛时间、抖动和漂移而言其性能并不良好或是不能接受的。

除了上面所说的性能问题之外,电路分析和实验表明,在这种应用场合下,当相位/环路增益足以控制时钟漂移时,“通常的”PLL在阻尼和稳定性的控制上存在着固有的问题。

10示出“常规的”PLL电路的一个具体例子图电路210。电路210用作一个接口,从线路211上155Mb/s的导步传递模式(ATM)单元流接口到线路222上同步的DS1的1.544Mb/s恒定比特率电路。由于线路211上入局单元流的突发和导步性质,线路222上同步地传送信息所需的时钟并不能利用线路211中的边沿信息或过渡信息来导出,而要依靠线路211上长时期的平均单元流速率来得到。线路211上的每个ATM单元为53字节的数据包,包括5字节的首标、1字节的适配层和47字节的可用信息有效负载。电路212实行CCITT适配层1处理,包括去除单元首标和适配层,并应用线路214上的写入选通经由字节母线213来控制47字节有效负载的写入一个同步的先进先出(FIFO)存储器215。FIFO215可存储到4096个8比特字节,它足以充分地存储在线路222上积累着等候传输的全部字节数目。FIFO215还在线路227上传送模拟的FIFO填充电平信号,它在空的FIFO时为0V,满的FIFO时变化到5V。

线路235上的自适应线路时钟用来控制从FIFO215向DS1也即线路222上同步的电路传输字节。这个线路235上的自适应线路时钟频率用来运行并/串变换器218和线路发送器221。该线路时钟频率由一个计数器223除以8,在线路224上得到的字节时钟用作读出选通,以便经由字节母线216、并/串变换器218和线路219从FIFO15中实现有效负载信息的字节读出,用于由线路221在线路222上作为一个DS1电路进行传输。线路发送器221将一个B8ZS码插入线路流中,以防止有7个以上接连的0比特在线路222上传送出。

线路227上的模拟电压通过一个由电阻232和电容234组成的PLL环路滤波器传输。滤波得到的电压对一个压控晶体振荡器(VCXO233)提供控制用输入信号,线路235上的VCXO233自适应线路时钟频率是在闭环状态下调整的。

CCITT研究组XVIII已规定了标准化的SRTS(先有技术的同步残余时间标记)结构,以在ATM网络中重建时钟速率。在这种结构中,将时钟速率信息以时间标记(time-stamp)形式编码在源电路中。该时间标记基本上是源电路时钟与网络基准时钟之间的差值。这个编码的时间标记以ATM单元首标的倒置比特形式传送到目的时钟电路。在目的时钟电路上,时间标记和网络基准时钟根本上用来重建原来的源频率。这方面的图解示于1992年3月9日CCITT的注释图5中。

本方法提供出性能优良的目的时钟电路,它满足全部传输要求。然而,只当有网络基准可供应用时,才可能应用。其它的缺点是需要从源时钟中得到编码的信息,以及在目的时钟电路上缺乏对调节或维持FIFO填充电平的控制。(FIFO填充电平影响电路中总的传输延时。)

Claims (17)

1.一种在一个电路配置中使用的方法,该电路配置包括:

接收装置,用以接收异步的、数据包化的信息;

存储装置,用以存储上述接收的信息;

发送装置,响应一个自适应线路时钟频率,在一个同步的电路上发送上述存储的信息;

该方法,其特征在于包括以下步骤:

连续监测存储在所述存储装置中的信息的量值与一个标称值的偏差;

检测所述监测到的偏差增加的状态;

根据所述检测到的增加状态,调整所述自适应线路时钟频率,使所述自适应线路时钟频率过校正,直至所述监测到的偏差开始减小。

2.根据权利要求1所述的方法,其特征在于,所述过校正包括:

使所述自适应线路时钟频率线性变化,但并不在所述监测到的偏差基础上连续地调整所述自适应线路时钟频率。

3.根据权利要求1所述的方法,其特征在于,所述调整还包括:

在所述过校正之后,使所述自适应线路时钟频率保持恒定,直至所述监测到的偏差减小到一个预定的阈值。

4.根据权利要求3所述的方法,其特征在于,所述保持恒定包括:

使所述自适应线路时钟频率保持恒定,而并不在所述监测到的偏差基础上连续地调整所述自适应线路时钟频率。

5.根据权利要求3所述的方法,其特征在于,还包括以下步骤:

连续地确定视在源频率,其中所述的调整还包括:

按所述多种模式的第三种方式,改变所述自适应线路时钟频率,直至所述自适应线路时钟频率等于所述视在源频率。

6.根据权利要求5所述的方法,其特征在于,使所述自适应线路时钟频率线性变化,但并不在所述监测到的偏差基础上连续地调整所述自适应线路时钟频率。

7.根据权利要求1所述的方法,其特征在于,还包括以下步骤:

对所述监测到的偏差进行积分,以滤除掉数据抖动。

8.一种在一个电路配置中使用的方法,该电路配置包括:

接收装置,用以接收异步的、数据包化的信息;

存储装置,用以存储所述接收的信息;

发送装置,响应一个自适应线路时钟频率,在一个同步的电路上发送所述存储的信息;

该方法其特征在于包括以下步骤:

连续监测存储在所述存储装置中的信息的量值与一个标称值的偏差;

对所述监测到的偏差增加状态进行检测;

根据所述检测到的增加状态,调整所述自适应线路时钟频率,但并不依据所述监测到的偏差连续地调整所述自适应线路时钟频率。

9.一种在一个电路配置中使用的方法,该电路配置包括:

接收装置,用以接收异步的、数据包化的信息;

存储装置,用以存储所述接收的信息;

发送装置,响应一个自适应线路时钟频率,在一个同步的电路上发送所述存储的信息;

该方法其特征在于包括以下步骤:

连续监测存储在所述存储装置中的信息的量值与一个标称值的偏差;

连续地确定视在源频率;

对所述监测到的偏差增加状态进行检测;

响应所述检测到的增加状态,部分地根据所述连续地确定的视在源频率来调整所述自适应线路时钟频率。

10.根据权利要求9所述的方法,其特征在于,所述连续地确定视在源频率包括:

在所述监测到的偏差和所述自适应线路时钟频率的基础上,连续地确定所述视在源频率。

11.一种在一个电路配置中使用的方法,该电路配置包括:

接收装置,用以接收异步的、数据包化的信息;

存储装置,用以存储所述接收的信息;

发送装置,响应一个自适应线路时钟频率,在一个同步的电路上发送所述存储的信息;

该方法其特征在于,包括以下步骤:

连续监测存储在所述存储装置中的信息的量值与一个标称值的偏差;

根据所述监测到的偏差和所述自适应线路时钟频率,连续地确定视在源频率以用于调整所述自适应线路时钟频率。

12.一种在一个电路配置中使用的方法,该电路配置包括:

接收装置,用以接收异步的、数据包化的信息;

存储装置,用以存储所述接收的信息;

发送装置,响应一个自适应线路时钟频率,在一个同步的电路上发送所述存储的信息;

该方法其特征在于,包括以下步骤:

连续监测存储在所述存储装置中的信息的量值与一个标称值的偏差;

对所述监测得的偏差增加状态进行检测;

响应所述检测到的增加状态,对所述自适应线路时钟频率实行开环调整。

13.根据权利要求12所述的方法,其特征在于,所述实行的调整包括:

对所述自适应线路时钟频率进行过校正,直至所述监测到的偏差开始减小。

14.根据权利要求15所述的方法,其特征在于,所述实行的调整还包括:

使所述自适应线路时钟频率保持恒定,直至所述监测到的偏差减小到一个预定的阈值。

15.根据权利要求14所述的方法,其特征在于,还包括:

连续地确定视在源频率,并且,其中所述实行的调整还包括:

改变所述自适应线路时钟频率,直至所述自适应线路时钟频率等于所述视在源频率。

16.根据权利要求15所述的方法,其特征在于,还包括:

在所述改变时钟频率之后,对所述自适应线路时钟频率实行闭环校正。

17.一种自适应时钟恢复装置,其特征在于包括:

接收装置,用以接收异步的、数据包化的信息;

存储装置,用以存储所述接收的信息;

发送装置,响应一个适应线路时钟频率,在一个同步的电路上发送所述存储的信息;

微处理器装置,用于(a)对所述存储装置中存储的信息的量值与一个标称值的偏差连续地进行监测;(b)对所述监测到的偏差增加状态进行检测;(c)响应所述检测到的增加状态,以多种模式调整所述自适应线路时钟频率。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US08/054,332 US5396492A (en) | 1993-04-28 | 1993-04-28 | Method and apparatus for adaptive clock recovery |

| US054,332 | 1993-04-28 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1101472A CN1101472A (zh) | 1995-04-12 |

| CN1065090C true CN1065090C (zh) | 2001-04-25 |

Family

ID=21990332

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN94104632XA Expired - Lifetime CN1065090C (zh) | 1993-04-28 | 1994-04-25 | 自适应时钟恢复的方法和装置 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US5396492A (zh) |

| EP (1) | EP0622918A3 (zh) |

| JP (1) | JP2981114B2 (zh) |

| KR (1) | KR100300255B1 (zh) |

| CN (1) | CN1065090C (zh) |

| AU (1) | AU662673B2 (zh) |

| CA (1) | CA2122111C (zh) |

| TW (1) | TW253090B (zh) |

Families Citing this family (85)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| GB2285201B (en) * | 1993-12-22 | 1997-12-10 | Roke Manor Research | Timing recovery apparatus |

| US5570345A (en) * | 1994-03-31 | 1996-10-29 | Telco Systems, Inc. | Protection switching system with single line control |

| US5787344A (en) | 1994-06-28 | 1998-07-28 | Scheinert; Stefan | Arrangements of base transceiver stations of an area-covering network |

| US5901149A (en) * | 1994-11-09 | 1999-05-04 | Sony Corporation | Decode and encode system |

| DE19509484A1 (de) * | 1995-03-16 | 1996-09-19 | Deutsche Telekom Ag | Verfahren zur empfangsseitigen Taktrückgewinnung für Digitalsignale |

| US5608731A (en) * | 1995-03-31 | 1997-03-04 | Transwitch Corporation | Closed loop clock recovery for synchronous residual time stamp |

| US5920572A (en) * | 1995-06-30 | 1999-07-06 | Divicom Inc. | Transport stream decoder/demultiplexer for hierarchically organized audio-video streams |

| US5822383A (en) * | 1995-12-15 | 1998-10-13 | Cisco Technology, Inc. | System and method for maintaining network synchronization utilizing digital phase comparison techniques with synchronous residual time stamps |

| GB9525923D0 (en) * | 1995-12-19 | 1996-02-21 | Newbridge Networks Corp | Delay minimization for circuit emulation over packet switched (atm) networks |

| US5835493A (en) * | 1996-01-02 | 1998-11-10 | Divicom, Inc. | MPEG transport stream remultiplexer |

| DE19644238C2 (de) * | 1996-10-24 | 1998-12-24 | Krone Ag | Verfahren zur Synchronisation von Übertragungen mit konstanter Bitrate in ATM-Netzen und Schaltungsanordnung zur Durchführung des Verfahrens |

| US6128301A (en) * | 1996-11-07 | 2000-10-03 | Nortel Networks Limited | Architecture for distribution of voice over ATM networks |

| US5912880A (en) * | 1996-11-07 | 1999-06-15 | Northern Telecom, Limited | System and method for ATM CBR timing recovery |

| US6829240B1 (en) * | 1996-11-27 | 2004-12-07 | Mindspeed Technologies, Inc. | System for, and method of, ATM segmentation and re-assembly of cells providing streaming data |

| US5949795A (en) * | 1997-02-14 | 1999-09-07 | General Instrument Corporation | Processing asynchronous data within a set-top decoder |

| US6108390A (en) * | 1997-03-07 | 2000-08-22 | Advanced Micro Devices, Inc. | Method of and apparatus for encoding of output symbol size |

| US5872823A (en) * | 1997-04-02 | 1999-02-16 | Sutton; Todd R. | Reliable switching between data sources in a synchronous communication system |

| US6282196B1 (en) * | 1997-04-14 | 2001-08-28 | Lucent Technologies Inc. | Dynamic build-out approach for use in packet voice systems |

| EP0876016B1 (en) * | 1997-05-02 | 2006-03-22 | Lsi Logic Corporation | Adaptive digital clock recovery |

| DE19723760B4 (de) * | 1997-06-06 | 2006-07-13 | Deutsche Telekom Ag | Einrichtung und Verfahren zum Empfang von Daten |

| US6044092A (en) * | 1997-06-11 | 2000-03-28 | At&T Corp. | Method and apparatus for performing automatic synchronization failure detection in an ATM network |

| GB9722500D0 (en) * | 1997-10-27 | 1997-12-24 | Nds Ltd | Method and apparatus for re-timing a digital signal |

| US6118836A (en) * | 1997-12-18 | 2000-09-12 | Alcatel Usa Sourcing L.P. | Frequency and phase locking apparatus |

| US6088414A (en) * | 1997-12-18 | 2000-07-11 | Alcatel Usa Sourcing, L.P. | Method of frequency and phase locking in a plurality of temporal frames |

| US6351471B1 (en) | 1998-01-14 | 2002-02-26 | Skystream Networks Inc. | Brandwidth optimization of video program bearing transport streams |

| US6195368B1 (en) | 1998-01-14 | 2001-02-27 | Skystream Corporation | Re-timing of video program bearing streams transmitted by an asynchronous communication link |

| US6351474B1 (en) * | 1998-01-14 | 2002-02-26 | Skystream Networks Inc. | Network distributed remultiplexer for video program bearing transport streams |

| US6246701B1 (en) | 1998-01-14 | 2001-06-12 | Skystream Corporation | Reference time clock locking in a remultiplexer for video program bearing transport streams |

| US6292490B1 (en) | 1998-01-14 | 2001-09-18 | Skystream Corporation | Receipts and dispatch timing of transport packets in a video program bearing stream remultiplexer |

| US6256308B1 (en) * | 1998-01-20 | 2001-07-03 | Telefonaktiebolaget Lm Ericsson | Multi-service circuit for telecommunications |

| US6157646A (en) * | 1998-01-26 | 2000-12-05 | Adc Telecommunications, Inc. | Circuit and method for service clock recovery |

| US6125109A (en) * | 1998-02-24 | 2000-09-26 | Repeater Technologies | Delay combiner system for CDMA repeaters and low noise amplifiers |

| ITMI981508A1 (it) * | 1998-07-01 | 2000-01-01 | Alcatel Alstrom Compagnie Gene | Metodo e dispositivo per il controllo numerico del buffer e di un anello ad aggancio di fase per reti asincrone |

| ES2145721B1 (es) * | 1998-10-28 | 2001-03-01 | Telefonica Sa | Recuperador de reloj basado en sintesis digital directa para el metodo adaptativo. |

| FR2786964B1 (fr) * | 1998-12-03 | 2001-01-05 | Cit Alcatel | Procede et systeme pour asservir une frequence via un reseau de transmission asynchrone et reseau radiotelephonique incluant ce systeme |

| US6804229B2 (en) | 1998-12-30 | 2004-10-12 | Nortel Networks Limited | Multiple node network architecture |

| US6885661B1 (en) | 1998-12-30 | 2005-04-26 | Nortel Networks Limited | Private branch exchange built using an ATM Network |

| US6778538B2 (en) | 1998-12-30 | 2004-08-17 | Nortel Networks Limited | Virtual junctors |

| US6788703B2 (en) | 1998-12-30 | 2004-09-07 | Nortel Networks Limited | DS0 on ATM, mapping and handling |

| US6768736B1 (en) | 1998-12-30 | 2004-07-27 | Nortel Networks Limited | Using an ATM switch to grow the capacity of a switching stage |

| JP3660517B2 (ja) * | 1999-03-01 | 2005-06-15 | 三菱電機株式会社 | データ受信装置、これに用いられるソースクロック再生方法およびその方法をコンピュータに実行させるプログラムを記録したコンピュータ読み取り可能な記録媒体 |

| US6522671B1 (en) * | 1999-05-10 | 2003-02-18 | Nortel Networks Limited | Protocol independent sub-rate device |

| IT1308746B1 (it) * | 1999-06-22 | 2002-01-10 | Cselt Centro Studi Lab Telecom | Dispositivo per la ricostruzione della temporizzazione di un canaledati trasportato su rete a pacchetto e relativo procedimento. |

| US6721328B1 (en) * | 1999-11-19 | 2004-04-13 | Adc Telecommunications, Inc. | Adaptive clock recovery for circuit emulation service |

| GB2357382B (en) * | 1999-12-17 | 2004-03-31 | Mitel Corp | Clock recovery PLL |

| US7027424B1 (en) | 2000-05-24 | 2006-04-11 | Vtech Communications, Ltd. | Method for avoiding interference in a digital communication system |

| US6731649B1 (en) * | 2000-07-26 | 2004-05-04 | Rad Data Communication Ltd. | TDM over IP (IP circuit emulation service) |

| US6975363B1 (en) * | 2000-08-31 | 2005-12-13 | Microsoft Corporation | Methods and systems for independently controlling the presentation speed of digital video frames and digital audio samples |

| JP4628620B2 (ja) * | 2000-10-10 | 2011-02-09 | パナソニック株式会社 | デジタルav信号処理装置 |

| US6307411B1 (en) | 2000-10-13 | 2001-10-23 | Brookhaven Science Associates | Wide tracking range, auto ranging, low jitter phase lock loop for swept and fixed frequency systems |

| GB0100094D0 (en) | 2001-01-03 | 2001-02-14 | Vtech Communications Ltd | System clock synchronisation using phased-lock loop |

| US7006510B2 (en) * | 2001-01-17 | 2006-02-28 | Optibase Ltd. | Method of clock mismatch and drift compensation for packet networks |

| CN100409636C (zh) * | 2001-04-12 | 2008-08-06 | 中兴通讯股份有限公司 | 一种高速串行数据通讯自适应时钟配置的方法 |

| JP2002354027A (ja) * | 2001-05-25 | 2002-12-06 | Nec Commun Syst Ltd | リアセンブリ手段、サーキットエミュレーションサービス装置及びatm同期制御方法 |

| JP3555883B2 (ja) * | 2001-06-08 | 2004-08-18 | 日本電気株式会社 | クロック再生方法及び受信クロック生成装置 |

| US7106758B2 (en) * | 2001-08-03 | 2006-09-12 | Adc Telecommunications, Inc. | Circuit and method for service clock recovery |

| US8880709B2 (en) * | 2001-09-12 | 2014-11-04 | Ericsson Television Inc. | Method and system for scheduled streaming of best effort data |

| GB0205350D0 (en) * | 2002-03-07 | 2002-04-24 | Zarlink Semiconductor Inc | Clock synchronisation over a packet network using SRTS without a common network clock |

| KR100437454B1 (ko) * | 2002-07-30 | 2004-06-23 | 삼성전자주식회사 | 소오스 싱크로너스 전송 방식을 이용한 비동기 메모리 및그것을 포함한 시스템 |

| EP1394974A3 (en) * | 2002-08-30 | 2005-08-03 | Zarlink Semiconductor Limited | Adaptive clock recovery in packet networks |

| AU2003279930A1 (en) * | 2002-10-09 | 2004-05-04 | Acorn Packet Solutions, Llc | System and method for rate agile adaptive clocking in a packet-based network |

| CN100395970C (zh) * | 2003-04-09 | 2008-06-18 | 华为技术有限公司 | 数据通信系统中数字式时钟恢复装置 |

| JP2004364293A (ja) * | 2003-05-29 | 2004-12-24 | Lycium Networks (Bvi) Ltd | 適応型速度管理、適応型ポインタ管理及び周波数ロックされた適応型ポインタ管理のための方法及びシステム |

| US7693222B2 (en) * | 2003-08-13 | 2010-04-06 | Ericsson Television Inc. | Method and system for re-multiplexing of content-modified MPEG-2 transport streams using PCR interpolation |

| EP1724960A4 (en) | 2004-03-10 | 2008-03-05 | Mitsubishi Electric Corp | DATA RECEIVING DEVICE AND DATA RECEIVING METHOD |

| US7693488B2 (en) | 2004-09-30 | 2010-04-06 | Vtech Telecommunications Limited | System and method for asymmetric enhanced mode operation in a digital communication system |

| CN100480960C (zh) * | 2004-10-14 | 2009-04-22 | 上海环达计算机科技有限公司 | 调整微处理器工作频率的控制方法和系统 |

| US7646836B1 (en) * | 2005-03-01 | 2010-01-12 | Network Equipment Technologies, Inc. | Dynamic clock rate matching across an asynchronous network |

| US7382780B1 (en) * | 2005-04-04 | 2008-06-03 | The United States Of America Represented By The Secretary Of The Navy. | Method for time coding of asynchronous data transmissions |

| US7984209B1 (en) * | 2006-12-12 | 2011-07-19 | Altera Corporation | Data interface methods and circuitry with reduced latency |

| JP5047743B2 (ja) * | 2007-09-14 | 2012-10-10 | 日本電信電話株式会社 | クロック再生方法および該方法を実行するデータ受信装置 |

| JP5105072B2 (ja) * | 2008-02-19 | 2012-12-19 | Necエンジニアリング株式会社 | タイミング情報採取装置 |

| US8068430B2 (en) | 2008-11-03 | 2011-11-29 | Rad Data Communications Ltd. | High quality timing distribution over DSL without NTR support |

| US8081639B2 (en) * | 2009-01-27 | 2011-12-20 | Tellabs Operations, Inc. | Method and apparatus for supporting client data transport with timing transparency |

| US8411705B2 (en) | 2010-01-06 | 2013-04-02 | Lsi Corporation | Three-stage architecture for adaptive clock recovery |

| US8462819B2 (en) * | 2010-01-06 | 2013-06-11 | Lsi Corporation | Adaptive clock recovery with step-delay pre-compensation |

| US8401025B2 (en) | 2010-04-28 | 2013-03-19 | Lsi Corporation | Windowing technique for adaptive clock recovery and other signal-processing applications |

| DE102010044208A1 (de) * | 2010-11-22 | 2012-05-24 | Robert Bosch Gmbh | Netzknoten, insbesondere für ein Sensornetzwerk, und Betriebsverfahren für einen Netzknoten |

| US8476945B2 (en) | 2011-03-23 | 2013-07-02 | International Business Machines Corporation | Phase profile generator |

| CN103152103A (zh) * | 2013-02-19 | 2013-06-12 | 青岛海信宽带多媒体技术有限公司 | 光模块及其cdr芯片的速率模式自适应调整方法 |

| GB2514572B (en) * | 2013-05-29 | 2020-05-27 | Grass Valley Ltd | Re-timing sampled data |

| WO2015156729A1 (en) | 2014-04-09 | 2015-10-15 | Transmode Systems Ab | Methods and nodes for transmission of a synchronous data over packet data network |

| CN105356995B (zh) * | 2015-11-24 | 2018-06-26 | 山东胜开电子科技有限公司 | 一种同步码双向恢复方法及电路 |

| FR3045251B1 (fr) * | 2015-12-11 | 2018-01-26 | Thales | Procedes et dispositifs de transmission de train binaire continu dans un reseau numerique non synchrone du train binaire |

| CN111198594B (zh) * | 2019-12-29 | 2023-05-23 | 西安中星测控有限公司 | 一种stm32内部hsi时钟自适应串口通讯系统 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3754098A (en) * | 1971-10-08 | 1973-08-21 | Adaptive Tech | Asynchronous sampling and reconstruction for asynchronous sample data communication system |

| US4759041A (en) * | 1987-02-19 | 1988-07-19 | Unisys Corporation | Local area network control system synchronization with phase-lock loop |

| US5142529A (en) * | 1988-12-09 | 1992-08-25 | Transwitch Corporation | Method and means for transferring a data payload from a first SONET signal to a SONET signal of different frequency |

Family Cites Families (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR2682244B1 (fr) * | 1991-10-04 | 1995-01-13 | Cit Alcatel | Dispositif de synchronisation pour equipement d'extremite d'un reseau de telecommunications numerique a transfert en mode asynchrone. |

-

1993

- 1993-04-28 US US08/054,332 patent/US5396492A/en not_active Expired - Lifetime

-

1994

- 1994-02-16 AU AU55201/94A patent/AU662673B2/en not_active Expired

- 1994-02-18 TW TW083101376A patent/TW253090B/zh not_active IP Right Cessation

- 1994-03-22 KR KR1019940005684A patent/KR100300255B1/ko not_active IP Right Cessation

- 1994-04-13 EP EP94302590A patent/EP0622918A3/en active Pending

- 1994-04-25 CN CN94104632XA patent/CN1065090C/zh not_active Expired - Lifetime

- 1994-04-25 CA CA002122111A patent/CA2122111C/en not_active Expired - Fee Related

- 1994-04-27 JP JP6110193A patent/JP2981114B2/ja not_active Expired - Lifetime

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3754098A (en) * | 1971-10-08 | 1973-08-21 | Adaptive Tech | Asynchronous sampling and reconstruction for asynchronous sample data communication system |

| US4759041A (en) * | 1987-02-19 | 1988-07-19 | Unisys Corporation | Local area network control system synchronization with phase-lock loop |

| US5142529A (en) * | 1988-12-09 | 1992-08-25 | Transwitch Corporation | Method and means for transferring a data payload from a first SONET signal to a SONET signal of different frequency |

Also Published As

| Publication number | Publication date |

|---|---|

| EP0622918A3 (en) | 1996-04-17 |

| CA2122111C (en) | 1999-06-29 |

| EP0622918A2 (en) | 1994-11-02 |

| CN1101472A (zh) | 1995-04-12 |

| CA2122111A1 (en) | 1994-10-29 |

| TW253090B (zh) | 1995-08-01 |

| KR100300255B1 (ko) | 2001-11-22 |

| JPH0746257A (ja) | 1995-02-14 |

| AU5520194A (en) | 1994-11-03 |

| JP2981114B2 (ja) | 1999-11-22 |

| KR940025223A (ko) | 1994-11-19 |

| AU662673B2 (en) | 1995-09-07 |

| US5396492A (en) | 1995-03-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1065090C (zh) | 自适应时钟恢复的方法和装置 | |

| CA2254591C (en) | Method of and apparatus for multiplexing and demultiplexing digital signal streams | |

| AU745230B2 (en) | Apparatus for reducing jitter in a digital desynchronizer | |

| CN101895403A (zh) | 一种数据传送方法、装置和通信系统 | |

| US9847945B2 (en) | Adaptive multi-service data framing | |

| CN101707506A (zh) | 一种光传送网中业务时钟透传的方法及系统 | |

| CN101043309A (zh) | 主备倒换的控制方法以及装置 | |

| US7457390B2 (en) | Timeshared jitter attenuator in multi-channel mapping applications | |

| CN1484888A (zh) | 锁相环 | |

| US6721825B1 (en) | Method to control data reception buffers for packetized voice channels | |

| KR102328071B1 (ko) | 광전송망의 트래픽을 처리하는 방법 및 장치 | |

| CN100495952C (zh) | 一种帧协议传输信道不同步原因的确定方法 | |

| CN109450585B (zh) | 基于状态机自适应控制的低时延gmp映射方法及系统 | |

| CN114257700B (zh) | 一种基于时间戳方式平台内同步的pcr校正方法和系统 | |

| EP0886405B1 (en) | Correction of calendar based ATM cell scheduling for downstream cell insertion | |

| US9112625B2 (en) | Method and apparatus for emulating stream clock signal in asynchronous data transmission | |

| CN1330152C (zh) | 对时分复接业务进行时钟恢复的装置及其方法 | |

| CN103795521B (zh) | 一种基于以太网传送e1信号的时钟恢复方法及装置 | |

| US6665298B1 (en) | Reassembly unit and a method thereof | |

| CN204244257U (zh) | 一种用于时钟恢复的离散补偿调整系统 | |

| JP3090710B2 (ja) | Atm伝送システム | |

| CN204244253U (zh) | 一种基于tdm的网络时钟恢复系统 | |

| US5923669A (en) | Adaptive boundary buffers | |

| EP1624601A2 (en) | Digital delay buffers and related methods | |

| CN112968754B (zh) | 一种基于n+1路e1信道实现数据可靠性传输方法、网络设备及计算机可读存储介质 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C17 | Cessation of patent right | ||

| CX01 | Expiry of patent term |

Expiration termination date: 20140425 Granted publication date: 20010425 |