CN1153295C - 半导体器件及其制造方法 - Google Patents

半导体器件及其制造方法 Download PDFInfo

- Publication number

- CN1153295C CN1153295C CNB971186790A CN97118679A CN1153295C CN 1153295 C CN1153295 C CN 1153295C CN B971186790 A CNB971186790 A CN B971186790A CN 97118679 A CN97118679 A CN 97118679A CN 1153295 C CN1153295 C CN 1153295C

- Authority

- CN

- China

- Prior art keywords

- convention

- trap

- impurity layer

- semiconductor device

- concentration

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body

- H01L27/10—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including a plurality of individual components in a repetitive configuration

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/8238—Complementary field-effect transistors, e.g. CMOS

- H01L21/823892—Complementary field-effect transistors, e.g. CMOS with a particular manufacturing method of the wells or tubs, e.g. twin tubs, high energy well implants, buried implanted layers for lateral isolation [BILLI]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B99/00—Subject matter not provided for in other groups of this subclass

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Semiconductor Memories (AREA)

- Element Separation (AREA)

- Junction Field-Effect Transistors (AREA)

Abstract

提供即使微细化也不改变抗软错误性、同时保持抗软错误性和耐闭锁性、具有防止电路误动作的基片结构的半导体器件及其制造方法。在半导体表面形成的反常规P阱3的底部,形成低浓度杂质层2。该低浓度杂质层2在半导体基片和反常规P阱3之间形成势垒,在抑制因电子产生的软错误的同时,由于在电气上与半导体基片1和反常规P阱3导通,所以限制了用于电位固定的端子数,对半导体集成电路的微细化作出了贡献。

Description

本发明涉及具有反常规阱结构的半导体器件及其制造方法。

在以存储保存为目的的DRAM等集成电路中,存在着信息偶尔丢失、即所谓的软错误的问题。引起这种软错误的代表性原因是α线的增强。

例如,P基片上形成由NMOSFET组成的存储元件的情况中,如果向基片内入射α线,α线通过与基片内原子的相互作用丢失能量而减速。在此过程中,产生多个电子空穴对,在这样产生的电子空穴对中,由于为使少数载流子的电子到达NMOSFET的N型扩散层,就会颠倒保持的信息(电位)。

还有,在CMOS结构中,通过由PMOS的源/漏和N阱及P阱构成的寄生PNP双极晶体管、由NMOS的源/漏和P阱及N阱构成的寄生NPN双极晶体管变为导通状态,形成闸流管,容易引起在CMOS电路的电源端子等之间产生大电流的闭锁现象。具体地说,如果阱的杂质浓度低,那么在阱区中电流流动时的阻抗就高,因为电压降变大,所以容易引起闭锁现象。如果引起这种闭锁,不仅损害了电路动作,在有些情况下,还会发生所谓的破坏集成电路自身的不良。

在作为解决这些问题的器件中,采用提高阱底部的杂质浓度、即所谓的反常规阱结构。这种反常规阱一般是在半导体基片内利用高能量的离子注入形成的。

例如,在K.Tsukamoto等的“用于ULSI的高能量离子注入”Nucl.Instr.and Meth.pp584-591 1991中披露了利用高能量的离子注入杂质形成的反常规阱的结构及其方法。

图77是表示形成了反常规阱的CMOS结构的半导体器件的剖面图。下面参照图,101是P型半导体基片,103是反常规P阱,104是反常规N阱,124是元件隔离氧化膜,125是源/漏,126是栅氧化膜,127是栅电极。图78是表示图77所示的半导体器件的X-X’剖面的基片部分中深度方向的杂质浓度分布图,图79是表示X-X’剖面中的内部势垒图。

由这些图可知,由于反常规P阱是用高能量离子注入注入杂质,所以在基片内期望的深度中可形成杂质浓度的峰值。因此,在反常规P阱上形成CMOS晶体管结构的情况下,在反常规P阱底部的高浓度部分,抑制了阻抗,电压降变小。因此,寄生双极晶体管的电流增幅率变小,使闭锁的产生变得不容易起来。

还有,不仅在CMOS结构中,而且在形成反常规P阱的情况下,利用由反常规阱底部的杂质浓度的峰值与基片杂质区的密耳能级差产生的势垒,妨碍为少数载流子的电子到达基片表面的源/漏125,提高抗软错误性。

再有,例如日本特许公开平4-212453中所披露的,为提高抗软错误性,用反常规N阱杂质层围绕反常规P阱的半导体基片结构及其制造方法。

图80是表示围绕反常规P阱的N型杂质层所形成的半导体器件基片部分的剖面图。图中,105是N型杂质层。在反常规P阱上可形成NMOS,作为存储区。图81是表示图80中Y-Y’剖面的深度方向的杂质浓度的分布图。

按照这种结构,由于α线等在基片中产生的少数载流子、即电子被这个N型杂质层吸收,妨碍了其到达反常规P阱区的表面上形成的源/漏层(图中未示),所以提高了抗软错误性。

例如,在F.S.Lai等的“用1MeV离子注入和自对准TiSi2加工无高闭锁的1μmCMOS技术”IEDM Tech.Dig.pp513-516 1985中披露,为提高抗软错误性,在非常高杂质浓度的基片上形成低浓度的阱的结构。

图82是表示在具有非常高P型杂质浓度的基片表面上设置杂质层的半导体器件基片部分的剖面图。图中,106是高浓度P型基片,113是P阱,104是反常规N阱。在反常规N阱104上形成PMOS、在P阱113上形成NMOS,构成CMOS电路。图83是表示图82中Z-Z’剖面的深度方向的杂质浓度的分布图。

这种结构中,由于采用高浓度的P型基片106,减小了基片阻抗、基片内的电流使电压降变小,所以可抑制CMOS电路的闭锁。

但是,随着集成电路的微细化,现有的反常规阱的结构中,抗软错误性和耐闭锁性均很低。

再有,在用N型杂质层围住反常规P阱的杂质结构的情况下,由于确定作为中间层的电位的端子是必要的,所以对微细化增加了结构上的复杂性。

此外,由于集成电路设计和处理技术上的进步,在同一芯片中装载高浓度的存储元件和高浓度的运算电路的集成电路的制造成为可能,但在这样的集成电路中,同时也需要高抗软错误性和高耐闭锁性。

因此,如果采用在高杂质浓度基片上形成低浓度杂质层的结构,由于显示高耐闭锁性,对CMOS结构是有效的,但在抗软错误的提高上却没有效果,后面的两层的费米(Fermi)能级差形成势垒后,妨碍向少数载流子基片的扩散,相反却因向元件形成区扩散而使抗软错误性劣化。

鉴于上述各点,本发明的目的在于提供即使微细化也不改变抗软错误性、同时保持抗软错误性和耐闭锁性、具有防止电路误动作的基片结构的半导体器件及其制造方法。

本发明的半导体器件包括:第1导电型的半导体基片,它具有第1杂质浓度;具有第1导电型的第1杂质层,它形成在所述半导体基片的主表面上,并具有带杂质浓度峰值的第2杂质浓度;与第1杂质层的下侧接触的第2杂质层,它具有小于第1杂质浓度和所述第2杂质浓度的浓度峰值的第3杂质浓度;和形成在所述第1杂质层上的元件。

再有,半导体器件具有第2杂质浓度的杂质浓度峰值和第3杂质浓度小于第1杂质浓度的特征。

还有,本发明的半导体器件包括:有第1杂质浓度的第1导电型的半导体基片;形成在半导体基片的主表面上、并有小于第1杂质浓度的杂质浓度峰值的第2杂质浓度的第1导电型的第1杂质层;与第1杂质层的下侧接触的有小于第1杂质浓度的杂质浓度峰值的第3杂质浓度的第2导电型的第2杂质层;和形成在第1杂质层上的元件。

此外,本发明的半导体器件包括:有第1杂质浓度的第2导电型的半导体基片;形成在半导体基片的主表面上、并有杂质浓度峰值的第2杂质浓度的第1导电型的第1杂质层;与第1杂质层的下侧接触的、有小于第1和第2杂质浓度的第3杂质浓度的第2杂质层;和形成在第1杂质层上的元件。

其中,半导体器件具有第1杂质层为反常规P阱、在第1杂质层上形成的元件为MOS型晶体管的特征。

因此,本发明的半导体器件的特征包括:第1杂质层为反常规P阱;在第1杂质层上形成的元件为MOS晶体管;而且在半导体基片的其它主表面上有互相邻近地形成的有第4杂质浓度的第2导电型的第3杂质层和有第5杂质浓度的第1导电型的第4杂质层;至少在第3和第4杂质层的表面上形成的、控制MOS型晶体管的CMOS晶体管。

并且,本发明的半导体器件的特征包括:第1杂质层为反常规P阱;在第1杂质层上形成的元件为MOS晶体管;而且在半导体基片的其它主表面上有互相邻近地形成的有第4杂质浓度的第2导电型的第3杂质层和有第5杂质浓度的第1导电型的第4杂质层;至少形成与第3和第4杂质层的下侧接触的、有大于第1至第5杂质浓度的第6杂质浓度的第1导电型的第5杂质层;至少在第3和第4杂质层形成的、控制MOS型晶体管的CMOS晶体管。

并且,本发明的半导体器件的特征包括:第1杂质层为反常规P阱;在第1杂质层上形成的元件为MOS晶体管;而且在半导体基片的其它主表面上有互相邻近地形成的有第4杂质浓度的第2导电型的第3杂质层和有第5杂质浓度的第1导电型的第4杂质层;至少在第3和第4杂质层的表面形成的、控制MOS型晶体管的CMOS晶体管。

本发明的半导体器件的制造方法包括下列步骤:在具有第1杂质浓度的第1导电型的半导体基片主表面上形成有小于第1杂质浓度的第2杂质浓度的第1杂质层;在第1杂质层的表面上,形成有大于第2杂质浓度的有杂质浓度峰值的第3杂质浓度的第2杂质层;和在第2杂质层表面上形成元件。

此外,本发明的半导体器件的制造方法的步骤包括:在具有第1杂质浓度的第1导电型的半导体基片主表面上形成小于第1杂质浓度的有杂质峰值的第2杂质浓度的第2导电型的第1杂质层;在第1杂质层的表面上,形成有小于第1杂质浓度的有杂质浓度峰值的第3杂质浓度的第2杂质层;和在第2杂质层表面上形成元件。

并且,本发明的半导体器件的制造方法的步骤还包括:在具有第1杂质浓度的第2导电型的半导体基片的主表面上形成小于第1杂质浓度的有第2杂质浓度的第11杂质层;在第1杂质层的表面上,形成有小于第1杂质浓度的有杂质浓度峰值的第3杂质浓度的第1导电型的第2杂质层;和在第2杂质层表面上形成元件。

还有,该制造方法的特征在于,具有利用外延生长形成第1杂质层的工艺、利用离子注入形成第2杂质层的工艺的特征。

而且,本发明的半导体器件的制造方法还包括下列步骤:在半导体基片的其它主表面上有互相邻近地形成的有第4杂质浓度的第2导电型的第3杂质层和有第5杂质浓度的第1导电型的第4杂质层;和至少在第3和第4杂质层的表面上形成控制MOS晶体管的CMOS晶体管。

再有,本发明的半导体器件的制造工艺步骤还包括:在与第1杂质层邻近的半导体基片上有大于第1至第5杂质浓度的第6杂质浓度的第1导电型的第5杂质层的形成工艺。

此外,本发明的半导体器件的制造方法还包括:有第1杂质浓度的第1导电型的半导体基片的主表面上形成有小于第1杂质浓度的第2杂质浓度的第1杂质层的工艺;在第1杂质层的第1部分形成小于第1杂质浓度的有第3杂质浓度的第2导电型的第2杂质层;在第1杂质层的第1部分的表面上,形成有大于第2和第3杂质浓度的杂质峰值的第4杂质浓度的第1导电型的第3杂质层;形成与第1杂质层的第2部分的表面相互邻接,有第5杂质浓度的第2导电型的第4杂质层和有第6杂质浓度的第1导电型的第5杂质层;在第3杂质层的表面上形成MOS型晶体管;和至少在第4和第5杂质层的表面上,形成控制MOS晶体管的CMOS晶体管。

并且,本发明的半导体器件的制造方法的特征还在于,第1杂质层浓度大于第2至第4杂质浓度、第2杂质浓度有杂质浓度峰值。

再有,本发明的半导体器件的制造方法的特征还在于,在第1杂质层的第2部分的底部形成有大于第2至第3杂质浓度的第7杂质浓度的第1导电型的第6杂质层。

而且,本发明的半导体器件的制造方法的特征还在于,利用外延生长形成第1杂质层、利用离子注入形成第3至第5杂质层。

图1是表示本发明实施例1的半导体器件剖面图。

图2是表示本发明实施例1的半导体器件基片剖面图。

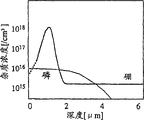

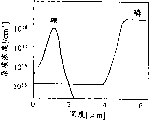

图3是表示示于图2的半导体器件基片的A-A’剖面中杂质浓度的分布图。

图4是表示示于图2的半导体器件基片的A-A’剖面中基片的内部势垒图。

图5是表示本发明实施例1的半导体器件制造方法的剖面图。

图6是表示本发明实施例1的半导体器件制造方法的剖面图。

图7是表示本发明实施例1的半导体器件制造方法的剖面图。

图8是表示示于图5的半导体器件基片的A-A’剖面中杂质浓度的分布图。

图9是表示本发明实施例2的半导体器件基片的剖面图。

图10是表示示于图9的半导体器件基片的A-A’剖面中杂质浓度的分布图。

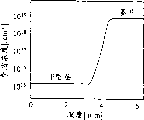

图11是表示示于图9的半导体器件基片的A-A’剖面中基片的内部势垒图。

图12是表示本发明实施例2的半导体器件制造方法的剖面图。

图13是表示本发明实施例2的半导体器件制造方法的剖面图。

图14是表示本发明实施例2的半导体器件制造方法的剖面图。

图15是表示本发明实施例2的半导体器件制造方法的剖面图。

图16是表示示于图14的半导体器件基片的A-A’剖面中硼和磷的杂质浓度分布图。

图17是表示示于图15的半导体器件基片的A-A’剖面中硼和磷的杂质浓度分布图。

图18是表示本发明实施例2的半导体器件制造方法的剖面图。

图19是表示本发明实施例2的半导体器件制造方法的剖面图。

图20是表示本发明实施例2的半导体器件制造方法的剖面图。

图21是表示示于图19的半导体器件基片的A-A’剖面中硼和磷的杂质浓度分布图。

图22是表示示于图20的半导体器件基片的深度方向上硼和磷的杂质浓度分布图。

图23是表示本发明实施例2的半导体器件制造方法的剖面图。

图24是表示本发明实施例2的半导体器件制造方法的剖面图。

图25是表示示于图23的半导体器件基片的A-A’剖面中硼和磷的杂质浓度分布图。

图26是表示示于图24的半导体器件基片的深度方向中硼和磷的杂质浓度分布图。

图27是表示本发明实施例3的半导体器件基片的剖面图。

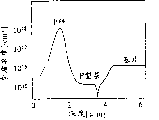

图28是表示示于图27的半导体器件基片的A-A’剖面中杂质浓度的分布图。

图29是表示本发明实施例3的半导体器件制造方法的剖面图。

图30是表示本发明实施例3的半导体器件制造方法的剖面图。

图31是表示示于图29的半导体器件基片的A-A’剖面中杂质浓度的分布图。

图32是表示本发明实施例4的半导体器件基片的剖面图。

图33是表示示于图32的半导体器件基片的A-A’剖面中杂质浓度的分布图。

图34是表示本发明实施例4的半导体器件制造方法的剖面图。

图35是表示本发明实施例4的半导体器件制造方法的剖面图。

图36是表示示于图34的半导体器件基片的A-A’剖面中杂质浓度的分布图。

图37是表示示于图35的半导体器件基片的深度方向上硼和磷的杂质浓度的分布图。

图38是表示本发明实施例5的半导体器件基片的剖面图。

图39是表示示于图38的半导体器件基片的A-A’剖面中杂质浓度的分布图。

图40是表示本发明实施例5的半导体器件制造方法的剖面图。

图41是表示本发明实施例5的半导体器件制造方法的剖面图。

图42是表示示于图40的半导体器件基片的深度方向上硼和磷的杂质浓度的分布图。

图43是表示示于图41的半导体器件基片的深度方向上硼和磷的杂质浓度的分布图。

图44是表示本发明实施例6的半导体器件基片的剖面图。

图45是表示示于图44的半导体器件基片的A-A’剖面中杂质浓度的分布图。

图46是表示示于图44的半导体器件基片的A-A’剖面中硼和磷的杂质浓度的分布图。

图47是表示本发明实施例6的半导体器件制造方法的一过程中硼和磷的杂质浓度的分布图。

图48是表示本发明实施例7的半导体器件基片的剖面图。

图49是表示示于图48的半导体器件基片的A-A’剖面中杂质浓度的分布图。

图50是表示示于图48的半导体器件基片的A-A’剖面中硼和磷在深度方向上的杂质浓度的分布图。

图51是表示示于图48的半导体器件基片的A-A’剖面中杂质浓度的分布图。

图52是表示示于图48的半导体器件基片的A-A’剖面中硼和磷的杂质浓度的分布图。

图53是表示本发明实施例8的半导体器件的剖面图。

图54是表示本发明实施例8的半导体器件基片的剖面图。

图55是表示示于图54的半导体器件基片的B-B’剖面中杂质浓度的分布图。

图56是表示本发明实施例8的半导体器件基片的剖面图。

图57是表示本发明实施例8的半导体器件制造方法的剖面图。

图58是表示本发明实施例8的半导体器件制造方法的剖面图。

图59是表示本发明实施例8的半导体器件制造方法的剖面图。

图60是表示本发明实施例8的半导体器件制造方法的剖面图。

图61是表示本发明实施例8的半导体器件制造方法的剖面图。

图62是表示本发明实施例8的半导体器件制造方法的剖面图。

图63是表示本发明实施例8的半导体器件制造方法的剖面图。

图64是表示本发明实施例9的半导体器件基片的剖面图。

图65是表示本发明实施例9的半导体器件基片的剖面图。

图66是表示示于图64的半导体器件基片的C-C’剖面中杂质浓度的分布图。

图67是表示本发明实施例9的半导体器件制造方法的剖面图。

图68是表示本发明实施例10的半导体器件基片的剖面图。

图69是表示本发明实施例10的半导体器件制造方法的剖面图。

图70是表示本发明实施例11的半导体器件基片的剖面图。

图71是表示示于图70的半导体器件基片的C-C’剖面中杂质浓度的分布图。

图72是表示本发明实施例11的半导体器件制造方法的剖面图。

图73是表示本发明实施例12的半导体器件基片的剖面图。

图74是表示本发明实施例12的半导体器件制造方法的剖面图。

图75是表示本发明实施例13的半导体器件基片的剖面图。

图76是表示本发明实施例13的半导体器件制造方法的剖面图。

图77是表示以往的半导体器件基片的剖面图。

图78是表示示于图77的半导体器件基片部分的深度方向上杂质硼和磷的图。

图79是表示示于图77的半导体器件的深度方向上的势垒图。

图80是表示以往的半导体器件基片的剖面图。

图81是表示示于图80的半导体器件深度方向上杂质硼和磷的图。

图82是表示以往的半导体器件基片的剖面图。

图83是表示示于图82的半导体器件深度方向上杂质硼和磷的图。

实施例1

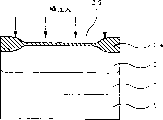

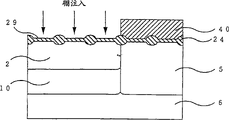

图1是表示本发明实施例1的半导体器件的剖面图。参照图,1是P型半导体基片,2是在P型半导体基片1中形成的P型杂质层,3是P型半导体基片1中形成的反常规P阱,21是单元极板,23是电介质膜,24是单元隔离氧化膜,25是源/漏,26是栅氧化膜,27是栅电极,28是氧化硅膜,30是层间绝缘膜,31是位线。由存储节点22、电介质膜23及单元极板21构成电容。

图2是图1所示的半导体器件的半导体基片的剖面图,图3是图2所示的半导体基片的A-A’剖面中的杂质浓度分布图,图4是图2所示的半导体基片的A-A’剖面中基片的内部势垒的示意图。

该半导体器件的基片由硼浓度为1×1015~1016/cm3的P型半导体基片1、硼浓度1×1015/cm3的P型杂质层2、硼浓度1×1018/cm3的反常规阱3构成。

图1中反常规P阱3表面上形成的晶体管有2个,在实际结构中可形成多个这样的晶体管。并且,在反常规P阱3内距表面0-0.2μm深度处,按需要形成具有防止穿通及阈值控制作用的沟道注入层,和在隔离氧化膜24的下面抑制沟道形成的阻断沟道注入等的杂质层。P型杂质层2靠近反常规P阱3的底部形成,也可以不在相关的反常规阱的侧面形成那一种情况都可以。

由图4可知,按照这种半导体基片的结构,由于P型杂质层2的存在,在半导体基片1中由α线等产生的电子的相对于反常规阱上部的势垒就变大,妨碍了电子到达在反常规P阱表面上已形成的源/漏区25,所以可抑制因电子造成的软错误。

并且,由于半导体基片1、P型杂质层2及反常规P阱3为同一导电型,并电气导通,所以不必分别单独地固定电位。因此,没有因端子数增加在元件配置上受到制约。还可获得半导体集成电路微细化的效果。

图5-7是表示本发明实施例1的半导体器件基片的制造方法的剖面图。参照图,29是下敷氧化膜。

图8是表示图5所示的半导体基片的A-A’剖面中的杂质浓度的分布图。

首先,如图5所示,在硼浓度1×1016/cm3的P型半导体基片1的表面上,利用外延生长,形成2-10μm的硼浓度1×1015/cm3的P型杂质层2。接着,如图6所示,在P型杂质层2的表面隔离区上形成元件隔离氧化膜,在有源区形成作为栅氧化膜的下敷氧化膜29。但是,并不在乎元件隔离层24与下敷氧化层29形成顺序的先后。

然后,如图7所示,若需要,对抗蚀剂构图,形成在反常规P阱3形成区上部开口的掩膜后,按200keV-1.5meV、1×1012~1×1014/cm2的条件,高能量注入P型杂质的离子态硼,形成反常规P阱3。然后,形成晶体管、层间绝缘膜、接触孔、电容等,进行布线(图中未示出)。

如上所述,按照这种半导体器件的制造方法,在半导体基片1中由α线等产生的电子相对于反常规阱3上部的势垒变大,妨碍电子到达已形成在反常规P阱3上的源/漏区25,可获得能抑制因电子产生的软错误的半导体器件。

此外,由于半导体基片1、P型杂质层2及反常规P阱3为同一导电型,是电气导通的,所以不必分别单独地固定电位。因此,没有因端子数增加在元件配置上受到制约。还可获得半导体集成电路微细化的效果。

并且,由于利用外延生长形成P型杂质层2使半导体基片1的浓度升高,所以可获得在构成晶体管的反常规P阱3的表面杂质浓度低的半导体器件。因此,在使半导体基片1和反常规P阱3的导通变得容易的同时,可防止阈值电压等的晶体管特性的劣化,在制造工艺上,也可较宽地设定杂质浓度控制等的工艺范围。

实施例2

图9是表示本发明实施例2的半导体器件的基片的剖面图。下面参照图,1是P型半导体基片,5是N型杂质层,3是反常规P阱,并且N型杂质层5的N型杂质浓度十分低,P型半导体基片1和反常规P阱3在电气上不绝缘。在这种反常规P阱3上,可形成与实施例1一样的元件(图中未示出)。

图10是表示图9所示的半导体基片的A-A’的剖面中的杂质浓度分布图,图11是表示图9所示的半导体基片的A-A’剖面中基片内部势垒的图。

该半导体器件的基片由硼浓度为1×1015~1016/cm3的P型半导体基片1、磷浓度1×1015/cm3的N型杂质层5、硼浓度1×1018/cm3的反常规阱3构成。

在反常规P阱3内距表面0-0.2μm深度处,按需要形成具有防止穿通及阈值控制作用的沟道注入层,在隔离氧化膜24的下面抑制沟道形成的阻断沟道注入等的杂质层。并且,N型杂质层5靠近反常规P阱3的底部形成,也可以不在相关的反常规阱的侧面形成那一种情况都可以。

由图11可知,利用N型杂质层5的存在,在半导体基片1中由α线等产生的电子的相对于反常规阱的上部的势垒就变大,由于妨碍了电子到达在反常规P阱3表面上已形成的源/漏区,所以可抑制因电子造成的软错误。

此外,N型杂质层5与半导体基片1及反常规P阱3为不同的导电型,虽然半导体基片1与反常规P阱3是电气导通的,但由于N型杂质层5有十分低的浓度,所以不必单独地固定各自的层电位。因此,没有因端子数增加在元件配置上受到制约,还可获得半导体集成电路微细化的效果。

图12-15是表示本发明实施例2的半导体器件基片的制造方法的剖面图,图16是表示图14所示的半导体基片A-A’剖面中硼和磷的杂质浓度的分布图,图17是表示图15所示的半导体基片深度方向上硼和磷的杂质浓度的分布图。

首先,如图12所示,在硼浓度1×1015/cm3的P型半导体基片1的主表面上的隔离区形成元件隔离氧化膜24,在有源区形成作为栅氧化膜的下敷氧化膜29。但是,并不在乎元件隔离层24与下敷氧化层29形成顺序的先后。

接着,如图13所示,若有必要,在P型半导体基片的表面上,对抗蚀剂构图,形成在N型杂质层5形成区上部开口构成掩膜后,按50keV-200keV、1×1011~5×1012/cm2的条件,注入N型杂质的离子态磷,形成N型杂质层51。

然后,如图14所示,利用1100℃-1200℃、0.5小时-3小时的热处理进行磷扩散后,形成N型杂质层5。

其中,在注入磷的杂质浓度低的情况下,或热处理温度高的情况下,或热处理时间长的情况下,在形成N型杂质层5的区域就形成像实施例1中那样的P型杂质层2,即使形成了P型杂质层2也不存在特殊的问题。

然后,如图15所示,若有必要,在P型半导体基片1表面上,对抗蚀剂构图,形成在反常规P阱3形成区上部开口构成掩膜后,按200keV-1.5MeV、1×1012~5×1014/cm2的条件,高能量注入P型杂质的离子态硼,形成反常规阱3。然后,在该反常规P阱3上,形成与实施例1相同的元件(图中未示出)。

如上所述,按照这种半导体器件的制造方法,使在半导体基片1和反常规P阱3之间能够保证插入的N型层持续导通的半导体器件的制造成为可能。因此,在半导体基片1中由α线等产生的电子的相对于反常规阱上部的势垒变大,妨碍电子到达已形成在反常规P阱3上的源/漏区,故可获得能抑制因电子产生的软错误的半导体器件的制造方法。

此外,N型杂质层5与半导体基片1及反常规P阱3为不同的导电型,虽然半导体基片1与反常规P阱3是电气导通的,但由于N型杂质层5有十分低的浓度,所以不必单独地固定各自的层电位。因此,没有因端子数增加在元件配置上受到制约,还可获得半导体集成电路微细化的效果。

图18-20是表示本发明实施例2的半导体器件基片的其它制造方法的剖面图,图21是表示图19所示的半导体基片A-A’剖面中硼和磷的杂质浓度的分布图,图22是表示图20所示的半导体基片深度方向上硼和磷的杂质浓度的分布图。

首先,与实施例1相同,在硼浓度1×1016/cm3的P型半导体基片1的表面上,利用外延生长,形成2-10μm的硼浓度为1×1015/cm3的P型杂质层2之后,在P型杂质层2的表面隔离区上形成元件隔离氧化膜24,在有源区形成作为栅氧化膜的下敷氧化膜29。但是,并不在乎元件隔离氧化膜24与下敷氧化膜29形成顺序的先后。

然后,如图18所示,若有必要,对抗蚀剂构图,形成对N型杂质层5形成区上部开口构成掩膜后,按50keV-200keV、1×1011~1×1013/cm2的条件,注入N型杂质的离子态磷,形成N型杂质层51。

然后,如图19所示,利用1100℃-1200℃、0.5小时-3小时的热处理进行磷扩散后,形成N型杂质层5。

其中,在注入磷的杂质浓度低的情况下、热处理温度高的情况下、或热处理时间长的情况下,在形成N型杂质层5的区域就形成像实施例1中那样的P型杂质层2,即使形成了P型杂质层2也不存在特殊的问题。

然后,如图20所示,若有必要,对抗蚀剂构图,形成对反常规P阱形成区上部开口的掩膜后,按200keV-1.5MeV、1×1012~1×1014/cm2的条件,高能量注入P型杂质的离子态硼,形成反常规P阱3。然后在该反常规P阱3上形成与实施例1相同的元件(图中未示出)。

如上所述,按照这种半导体器件的制造方法,在半导体基片1中由α线等产生的电子的相对于反常规阱3上部的势垒变大,妨碍电子到达已形成在反常规P阱3上的源/漏区,可获得能抑制因电子产生的软错误的半导体器件的制造方法。

并且,由于外延生长后形成N型杂质层5,使半导体基片1的浓度升高,所以可获得构成晶体管的反常规P阱3的表面杂质浓度低的半导体器件。因此,在使半导体基片1和反常规P阱3的导通变得容易的同时,可防止阈值电压等的晶体管特性的劣化,在制造工艺上,也可较宽地设定杂质浓度控制等的工艺范围。

此外,N型杂质层5与半导体基片1及反常规P阱3为不同的导电型,虽然半导体基片1与反常规P阱3是电气导通的,但由于N型杂质层5有十分低的浓度,所以不必单独地固定各自的层电位。因此,没有因端子数增加在元件配置上受到制约,还使微细化的半导体集成电路的制造成为可能。

图23-24是表示本发明实施例2的半导体器件基片的其它制造方法的剖面图,图25是表示图2 3所示的半导体器件基片A-A’剖面中硼和磷的杂质定点测定的结果图,图26是表示图24所示的半导体器件基片深度方向上硼和磷的杂质浓度的分布图。

首先,如图23所示,在硼浓度1×1016/cm3的P型硅基片1上,生长2-5μm的磷浓度为1×1015/cm3的N型外延层5之后,在P型杂质层2表面的隔离区上形成元件隔离氧化膜24,在有源区形成作为栅氧化膜的下敷氧化膜29。但是,并不在乎元件隔离氧化膜24与下敷氧化膜29形成顺序的先后。

然后,如图24所示,若有必要,对抗蚀剂构图,形成对反常规P阱3形成区上部开口的掩膜后,按200keV-1.5MeV、1×1012~1×1014/cm2的条件,高能量注入P型杂质的离子态硼,形成反常规P阱3。然后形成与实施例1相同的元件(图中未示出)。

如上所述,按照这种半导体器件的制造方法,在半导体基片1中由α线等产生的电子的相对于反常规阱3上部的势垒变大,妨碍电子到达已形成在反常规P阱3上的源/漏区,可获得能抑制因电子产生的软错误的半导体器件。

并且,由于利用外延生长形成N型杂质层5,使半导体基片1的浓度升高,所以可获得构成晶体管的反常规P阱3的表面杂质浓度低的半导体器件。因此,在使半导体基片1和反常规P阱3的导通变得容易的同时,可防止阈值电压等的晶体管特性的劣化,在制造工艺上,也可实现工艺的简化,还可较宽地设定杂质浓度控制等的工艺范围。

此外,N型杂质层5与半导体基片1及反常规P阱3为不同的导电型,虽然半导体基片1与反常规P阱3是电气导通的,但由于N型杂质层5有十分低的浓度,所以不必单独地固定各自的层电位。因此,没有因端子数增加在元件配置上受到制约,还使微细化的半导体集成电路的制造成为可能。

实施例3

图27是表示本发明实施例3的半导体器件的基片的剖面图。下面参照图,6是P型半导体基片,2是P型半导体基片中形成的P型杂质层,3是P型半导体基片6中形成的反常规P阱。

图28是表示图27所示的半导体基片A-A’剖面中杂质浓度的分布图。

如图28所示,该半导体器件的基片由硼浓度为1×1019/cm3的高浓度P型半导体基片6、硼浓度为1×1015/cm3的P型杂质层2、硼浓度为1×1018/cm3的反常规P阱3构成。

此外,在反常规P阱3上形成多个或单个晶体管(图中未示出)。然后,在反常规P阱3内距表面0-0.2μm深度处,也有形成具有防止穿通及阈值控制作用的沟道注入层、和在隔离氧化膜24下面抑制沟道形成的阻断沟道注入等的杂质层的情况。P型杂质层2在靠近反常规P阱3的底部形成,也可以不在相关的反常规阱的侧面形成,那一种情况都可以。

在这种基片结构上形成存储元件的情况下(图中未示出),由图28所示的杂质浓度分布可知,在P型半导体基片6中由α线等产生的电子的相对于反常规阱上部中的势垒,因P型杂质层2的存在而未变大,在P型半导体基片6中,由于电子的寿命时间变短,所以防止了电子到达反常规P阱3表面上形成的源/漏区,具有更能抑制软错误的效果。

此外,在这个基片结构上形成作为控制电路的CMOS晶体管的情况下,利用P型半导体基片使基片阻抗变低,同时,由于形成了反常规P阱3,所以具有提高耐闭锁的效果。

并且,由于P型半导体基片6、P型杂质层2及反常规P阱3为同一导电型,是电导通的,所以不必分别单独地固定电位。因此,即使在形成存储元件CMOS的那一种情况下,都没有因端子数增加在元件配置上受到制约,也具有半导体集成电路微细化的效果。

再有,由于P型半导体基片6的浓度较高,形成晶体管的反常规P阱3的表面杂质浓度较低,所以,在使P型半导体基片6和反常规P阱3的导通变得容易的同时,还具有所谓的抑制阈值电压等的晶体管特性劣化的效果。

图29-30是表示本发明实施例3的半导体器件基片的制造方法的剖面图,图31是表示图29所示的半导体器件基片A-A’剖面中杂质浓度的分布图。

首先,如图29所示,在硼浓度为1×1019/cm3的高浓度P型半导体基片6的表面上,形成2-10μm的硼浓度为1×1015/cm3的P型外延层2。

然后,在P型杂层2表面的隔离区上形成元件隔离氧化膜24,在有源区形成作为栅氧化膜的下敷氧化膜29。但是,并不在乎元件隔离氧化膜24与下敷氧化膜29形成顺序的先后。

然后,如图20所示,若有必要,对抗蚀剂构图,形成对反常规P阱3形成区上部开口的掩膜后,按200keV-1.5MeV、1×1012~1×1014/cm2的条件,高能量注入P型杂质的离子态硼,形成硼浓度为1×1018/cm2反常规P阱3。然后根据需要形成单个或多个晶体管、层间绝缘膜、接触孔、电容等,进行布线(图中未示出)。

在反常规P阱3内距表面0-0.2μm深度处,也有形成具有防止穿通及阈值控制作用的沟道注入层、和在隔离氧化膜24下面抑制沟道形成的阻断沟道注入等的杂质层的情况。

P型杂质层2在靠近反常规P阱3的底部形成,也可以不在相关的反常规阱的侧面形成,那一种情况都可以

如上所述,按照这种半导体器件的制造方法,在P型半导体基片6中由α线等产生的电子的相对于反常规阱上部中的势垒,因P型杂质层2的存在而未变大,由于在P型半导体基片6中电子的寿命时间变短,所以防止了电子到达反常规P阱3表面上形成的源/漏区,并还可获得提高抗软错误性的半导体存储器件的制造方法。

此外,在这种基片结构上形成CMOS晶体管的情况下,由于半导体基片6的浓度较高,所以,在使基片阻抗变低的同时,因形成反常规P阱3而具有进一步提高耐闭锁性的效果。

并且,由于P型半导体基片6、P型杂质层2及反常规P阱3为同一导电型,是电导通的,所以不必分别单独地固定电位。因此,即使在形成存储元件CMOS的那种情况下,没有因端子数增加在元件配置上受到制约,使微细化的半导体集成电路的制造成为可能。

再有,由于利用外延生长形成P型杂质层2,所以P型半导体基片6的浓度较高,形成晶体管的反常规P阱3的表面杂质浓度变得较低,在使P型半导体基片6和反常规P阱3的导通变得容易的同时,还具有所谓的抑制阈值电压等的晶体管特性劣化的效果。

实施例4

图32是表示本发明实施例4的半导体器件的基片的剖面图。下面参照图,6是P型半导体基片,5是P型半导体基片中形成的N型杂质层,3是P型半导体基片6中形成的反常规P阱。

图33是表示图32所示的半导体基片A-A’剖面中杂质浓度的分布图。

如图33所示,该半导体器件的基片由硼浓度为1×1019/cm3的高浓度P型半导体基片6、磷浓度为1×1015/cm3的N型杂质层5、硼浓度为1×1018/cm3的反常规P阱3构成。

此外,在反常规P阱3上形成多个或单个晶体管(图中未示出)。然后,在反常规P阱3内距表面0-0.2μm深度处,也有形成具有防止穿通及阈值控制作用的沟道注入层、和在隔离氧化膜24下面抑制沟道形成的阻断沟道注入等的杂质层的情况。N型杂质层5在靠近反常规P阱3的底部形成,也可以不在相关的反常规阱的侧面形成,那一种情况都可以。

在这种基片结构上形成存储元件的情况下,由图33所示的杂质浓度分布可卸,在P型半导体基片6中由α线等产生的电子的相对于反常规阱上部中的势垒,因N型杂质层5的存在而未变大,在P型半导体基片6中,由于电子的寿命时间变短,所以防止了电子到达反常规P阱3表面上形成的源/漏区,具有更能抑制软错误的效果。

此外,在这个基片结构上形成作为控制电路的CMOS晶体管的情况下,利用P型半导体基片6使基片阻抗变低,同时,由于形成了反常规P阱3,所以具有提高耐闭锁性的效果。

此外,虽然N型杂质层5与半导体基片6及反常规P阱3为不同的导电型,半导体基片6与反常规P阱3是电气导通的,但由于N型杂质层5有十分低的浓度,所以不必单独地固定各自的层电位。因此,没有因端子数增加在元件配置上受到制约,在半导体集成电路的微细化方面有效果。

再有,由于形成P型半导体基片6的浓度较高、晶体管的反常规P阱3的表面杂质浓度较低,所以在使P型半导体基片6和反常规P阱3的导通变得容易的同时,还具有所谓的抑制阈值电压等的晶体管特性劣化的效果。

图34-35是表示本发明实施例4的半导体器件基片的制造方法的剖面图,图36是表示图34所示的半导体器件基片A-A’剖面中杂质浓度的分布图。图37是表示图35所示的半导体器件基片深度方向上的硼和磷的杂质浓度的分布图。

首先,如图34所示,在硼浓度为1×1018-1×1019/cm3的P型半导体基片6上,形成2-10μm的外延生长的磷浓度为1×1015/cm3的N型杂质层5。

然后,在N型杂质层5表面的隔离区上形成元件隔离氧化膜24,在有源区形成作为栅氧化膜的下敷氧化膜29。但是,并不在乎元件隔离氧化膜24与下敷氧化膜29形成顺序的先后。

然后,如图35所示,若有必要,对抗蚀剂构图,形成对反常规P阱3形成区上部开口的掩膜后,按200keV-1.5MeV、1×1012~1×1014/cm2的条件,高能量注入P型杂质的离子态硼,形成硼浓度为1×1018/cm2反常规P阱3。然后根据需要形成单个或多个晶体管、层间绝缘膜、接触孔、电容等,进行布线。

在反常规P阱3内距表面0-0.2μm深度处,也有形成具有防止穿通及阈值控制作用的沟道注入层、和在隔离氧化膜24下面抑制沟道形成的阻断沟道注入等的杂质层的情况。

N型杂质层5在靠近反常规P阱3的底部形成,也可以不在相关的反常规阱的侧面形成,那一种情况都可以。

如上所述,按照这种半导体器件的制造方法,在P型半导体基片6中由α线等产生的电子的相对于反常规阱上部中的势垒,因N型杂质层5的存在而未变大,由于在P型半导体基片6中电子的寿命时间变短,所以防止了电子到达反常规P阱3表面上形成的源/漏区,并还可获得提高抗软错误性的半导体存储器件的制造方法。

此外,在这种基片结构上形成CMOS晶体管的情况下,由于半导体基片6的浓度较高,所以,在使基片阻抗变低、半导体基片与反常规P阱3的导通变得容易的同时,还可获得进一步提高耐闭锁性的半导体器件的制造方法。

此外,N型杂质层5与半导体基片6及反常规P阱3为不同的导电型,虽然半导体基片1与反常规P阱3是电气导通的,但由于N型杂质层5有十分低的浓度,所以不必单独地固定各自的层电位。因此,没有因端子数增加在元件配置上受到制约,还使微细化的半导体集成电路的制造成为可能。

再有,由于利用外延生长形成N型杂质层5,所以在可获得P型半导体基片6的浓度较高、形成晶体管的反常规P阱3的表面杂质浓度较低的半导体器件,在使P型半导体基片6和反常规P阱3的导通变得容易的同时,还具有所谓的抑制阈值电压等的晶体管特性劣化的效果。

实施例5

图38是表示本发明实施例4的半导体器件的基片的剖面图。下面参照图,6是P型半导体基片,7是P型半导体基片中形成的N型杂质层,3是P型半导体基片6中形成的反常规P阱。

图39是表示图38所示的半导体基片A-A’剖面中杂质浓度的分布图。

如图39所示,该半导体器件的基片由硼浓度为1×1019/cm3的高浓度P型半导体基片6、磷浓度为1×1018/cm3的N型杂质层7、硼浓度为1×1018/cm3的反常规P阱3构成。

此外,在反常规P阱3上形成多个或单个晶体管(图中未示出)。然后,在反常规P阱3内距表面0-0.2μm深度处,也有形成具有防止穿通及阈值控制作用的沟道注入层、和在隔离氧化膜24下面抑制沟道形成的阻断沟道注入等的杂质层的情况。N型杂质层7是围绕在反常规P阱3的周围形成的。

在这种基片结构上形成存储元件的情况下,由图39所示的杂质浓度分布可知,在P型半导体基片6中,电子的寿命时间并未变短,由α线等产生的电子的相对于反常规阱上部中的势垒因N型杂质层7的存在而变大,所以防止了电子到达在反常规P阱3表面上形成的源/漏区,具有抑制软错误的效果。

此外,在这个基片结构上形成作为控制电路的CMOS晶体管的情况下,利用P型半导体基片6使基片阻抗变低,同时,由于形成了围绕反常规P阱3周围的N型杂质层7,使P型基板6与反常规P阱3隔离,所以具有提高耐闭锁性的效果。

图40-41是表示本发明实施例5的半导体器件基片的制造方法的剖面图,图42是表示图40所示的半导体器件基片深度方向上硼和磷的杂质浓度的分布图。图43是表示图42所示的半导体器件基片深度方向上的硼和磷的杂质浓度的分布图。

首先,与实施例3一样,在硼浓度为1×1018/cm3的P型半导体基片6上,形成利用2-10μm的外延生长的磷浓度为1×1015/cm3的P型杂质层2。

然后,在P型杂质层2表面的隔离区上形成元件隔离氧化膜24,在有源区形成作为栅氧化膜的下敷氧化膜29。但是,并不在乎元件隔离氧化膜24与下敷氧化膜29形成顺序的先后。

然后,如图40所示,若有必要,对抗蚀剂构图,形成对反常规P阱3形成区上部开口构成掩膜后,按500keV-10MeV、1×1012~1×1014/cm2的条件,高能量注入N型杂质的离子态磷,形成N型杂质层7。

然后,如图41所示,若有必要,对抗蚀剂构图,形成,对反常规P阱3形成区上部开口的掩膜后,按200keV-1.5MeV、1×1012~1×1014/cm2的条件,高能量注入P型杂质的离子态硼,形成反常规P阱3。

然后根据需要,形成单个或多个晶体管、层间绝缘膜、接触孔、电容等,进行布线。

再有,在形成N型杂质层7和形成反常规P阱3中,如果形成围绕反常规P阱3的N型杂质层7,那么无论先形成哪一个都行。

在反常规P阱3内距表面0-0.2μm深度处,也有形成具有防止穿通及阈值控制作用的沟道注入层、和在隔离氧化膜24下面抑制沟道形成的阻断沟道注入等的杂质层的情况。

如上所述,按照这种半导体器件的制造方法,在P型半导体基片6中由α线等产生的电子的相对于反常规阱上部中的势垒,因N型杂质层7的存在而未变大,由于在P型半导体基片6中电子的寿命时间变短,所以防止了电子到达反常规P阱3表面上形成的源/漏区,并还可获得提高抗软错误性的半导体存储器件的制造方法。

此外,在此基片的结构上形成CMOS晶体管的情况下,在P型半基片6上,由于利用外延生长形成P型杂质层2后形成N型杂质层7及反常规P阱3,所以半导体基片6的浓度较高,可获得形成晶体管的P阱3的表面杂质浓度较低的半导体器件。因此,在抑制阈值电压等的晶体管特性劣化的同时,利用较低的基片阻抗和反常规P阱3,可获得提高耐闭锁性的半导体器件。

实施例6

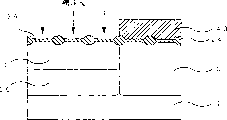

图44是表示本发明实施例6的半导体器件的基片的剖面图。下面参照图,11是N型半导体基片,2是N型半导体基片中形成的P型杂质层,3是N型半导体基片11中形成的反常规P阱。图45是表示图44所示的半导体基片A-A’剖面中杂质浓度的分布图。图46是表示图44所示的半导体基片A-A,剖面中硼和磷的杂质浓度的分布图。

如图45所示,该半导体器件的基片由磷浓度为1×1016/cm3的高浓度N型半导体基片11、硼浓度为1×1015/cm3的P型杂质层2、硼浓度为1×1018/cm3的反常规P阱3构成。

此外,在反常规P阱3上形成多个或单个晶体管(图中未示出)。然后,在反常规P阱3内距表面0-0.2μm深度处,也有形成具有防止穿通及阈值控制作用的沟道注入层、和在隔离氧化膜24下面抑制沟道形成的阻断沟道注入等的杂质层的情况。P型杂质层2在靠近反常规P阱3的底部形成,也可以不在相关的反常规阱的侧面形成,那一种情况都可以。

根据这种基片结构,由于缓和了反常规P阱3和半导体基片11的电场,所以有提高耐压的效果。

再有,由于半导体基片11的浓度较高、形成晶体管的反常规P阱3的表面杂质浓度较低,所以可防止阈值电压等的晶体管特性劣化。

下面,说明本发明实施例6的半导体器件的基片的制造方法。

首先,与实施例1一样在磷浓度为1×1016/cm3的N型半导体基片11上,利用生长2-10μm的外延形成硼浓度为1×1015/cm3的P型杂质层2后,形成元件氧化膜24、下敷氧化膜29。图47是表示此时的硼和磷的深度方向上的杂质浓度图。

然后,与实施例1一样,根据需要,形成单个或多个反常规P阱3、晶体管、层间绝缘膜、接触孔、电容等,进行布线。

在反常规P阱3内距表面0-0.2μm深度处,也有形成具有防止穿通及阈值控制作用的沟道注入层、和在隔离氧化膜24下面抑制沟道形成的阻断沟道注入等的杂质层的情况。

如上所述,按照这种半导体器件的制造方法,因为缓和了反常规P阱3和半导体基片11的电场,所以可获得具有提高耐压效果的半导体器件的制造方法。

并且,由于半导体基片11的浓度高、形成晶体管的反常规P阱3的表面杂质浓度低,所以可防止阈值电压等的晶体管特性的劣化,在制造工艺上,也可较宽地设定杂质浓度控制等的工艺条件的范围。

实施例7

图48是表示本发明实施例7的半导体器件的基片的剖面图。下面参照图,11是N型半导体基片,5是N型半导体基片11中形成的N型杂质层,3是N型半导体基片11中形成的反常规P阱。图49是表示图48所示的半导体器件基片A-A’剖面中杂质浓度的分布图。图50是表示图48所示的半导体器件基片A-A’剖面中硼和磷在深度方向上的杂质浓度的分布图。

该半导体器件具有由磷浓度为1×1016/cm3的N型半导体基片11、磷浓度为1×1015/cm3的N型杂质层5、硼浓度为1×1018/cm3的反常规阱层3构成的基片结构。

N型半导体基片11最好采用磷浓度为1×1018/cm3的基片。这时,图51是表示图48所示的半导体器件基片A-A’剖面中的杂质浓度的分布图,图52是表示图48所示的半导体器件基片A-A’剖面中硼和磷的杂质浓度的分布图。

此外,在反常规P阱3上形成多个或单个晶体管(图中未示出)。然后,在反常规P阱3内距表面0-0.2μm深度处,也有形成具有防止穿通及阈值控制作用的沟道注入层、和在隔离氧化膜24下面抑制沟道形成的阻断沟道注入等的杂质层的情况。N型杂质层5在靠近反常规P阱3的底部形成,也可以不在相关的反常规阱的侧面形成,那一种情况都可以。

根据这种基片结构,利用N型杂质层5,由于缓和了反常规P阱3和半导体基片11的电场,所以有提高耐压的效果。

再有,由于半导体基片11的浓度较高、晶体管的反常规P阱3的表面杂质浓度较低,所以可防止阈值电压等的晶体管特性劣化。

此外,在N型半导体基片11的磷深度为1×1018/cm3的情况下,由于基片阻抗变低、同时形成了反常规P阱,在形成CMOS晶体管的情况下,具有使耐闭锁性进一步提高的效果。

下面,说明本发明实施例7的半导体器件基片的制造方法。

首先,与实施例2一样,在磷浓度为1×1016/cm3的N型半导体基片11上,利用2-10μm的外延生长形成磷浓度为1×1015/cm3的N型杂质层5之后,形成元件隔离氧化膜24、下敷氧化膜29。

然后,与实施例2相同,根据需要,形成单个或多个反常规P阱3、晶体管、层间绝缘膜、接触孔、电容等,进行布线。

在反常规P阱3内距表面0-0.2μm深度处,也有形成具有防止穿通及阈值控制作用的沟道注入层、和在隔离氧化膜24下面抑制沟道形成的阻断沟道注入等的杂质层的情况。

如上所述,按照这种半导体器件的制造方法,因为缓和了反常规P阱3和半导体基片11的电场,所以可获得具有提高耐压效果的半导体器件的制造方法。

并且,由于半导体基片11的浓度高、形成晶体管的反常规P阱3的表面杂质浓度低,所以可防止阈值电压等的晶体管特性的劣化,在制造工艺上,也可较宽地设定杂质浓度控制等的工艺条件的范围。

此外,如果利用磷浓度为1×1018/cm3的N型半导体基片11,由于基片阻抗变低、同时形成了反常规P阱、所以在形成了CMOS晶体管的情况下,可获得具有进一步提高耐闭锁性的半导体器件的制造方法。

实施例8

图53是表示本发明实施例8的半导体器件的剖面图。下面参照图,1是P型半导体基片,5是P型半导体基片中形成的N型杂质层,3和8是P型半导体基片中形成的反常规P阱,4和9是反常规N阱,24是元隔离氧化膜,25是源/漏,26是栅氧化膜,27是栅电极。

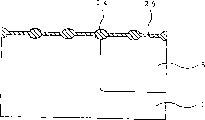

此外,图54是表示本发明实施例8的半导体器件基片的剖面图。

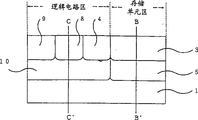

这种半导体器件大体区分为以存储主要容量的信息为目的的元件区(存储单元区)和以一边获取存储单元区的大量信息一边进行逻辑运算为目的的元件区(逻辑电路区)。

存储单元区主要由NMOSFET构成,逻辑电路区主要由CMOSFET构成。

图55是表示图54所示的半导体基片C-C’剖面中杂质浓度的分布图。此外,图54所示的半导体基片B-B’剖面中杂质浓度的分布就像图10所示的那样。由图54可知,存储单元区具有与实施例2相同的基片结构。

在反常规P阱3上形成多个或单个晶体管(图中未示出)。然后,在反常规P阱3内距表面0-0.2μm深度处,也有形成具有防止穿通及阈值控制作用的沟道注入层、和在隔离氧化膜24下面抑制沟道形成的阻断沟道注入等的杂质层的情况。N型杂质层5在靠近反常规P阱3的底部形成,也可以不在相关的反常规阱的侧面形成那一种情况都可以。

在反常规P阱8、反常规N阱4及反常规N阱9上形成多个或单个晶体管(图中未示出)、形成逻辑电路区的CMOS。这种情况下,也在反常规阱内距表面0-0.2μm深度处,有形成具有防止穿通及阈值控制作用的沟道注入层、和在隔离氧化膜24下面抑制沟道形成的阻断沟道注入等的杂质层的情况。

此外,通过在反常规N阱4和反常规P阱3上分别形成晶体管,也可以形成作为逻辑电路的CMOS。这时,在反常规P阱上也形成了作为存储单元的晶体管。此时,在图56所示的N型杂质层5未形成的区中也可以形成经扩散反常规P阱,通过它可维持逻辑电路区的耐闭锁性。

用于逻辑电路区CMOS的阱可以仅是反常规P阱3的一部分和反常规N阱4,相反地,也可以多于本实施例中所述的阱。

按照存储单元区的基片结构,由图10可知,在P型半导体基片1中由α线等产生的电子的相对于反常规阱上部的势垒,因N型杂质层的存在变大,妨碍电子到达已形成在反常规P阱3表面上的源/漏区,具有抑制软错误的效果。

此外,半导体基片1、N型杂质层5及反常规P阱3是电气导通的,不必分别单独地固定各自的电位。因此,没有因端子数增加在元件配置上受到制约,在半导体集成电路微细化上也有效果。

图57~图63是表示本发明实施例8的半导体器件基片的制造方法的剖面图。

首先,如图57所示,在硼浓度为1×1015/cm3的P型半导体基片1主表面上的隔离区的形成元件隔离氧化膜24,在有源区形成作为栅氧化膜的下敷氧化膜29。但是,并不在乎元件隔离氧化膜24与下敷氧化膜29形成顺序的先后。

然后,如图58所示,对抗蚀剂40构图、对存储单元区开口之后,按50keV-200keV、1×1011~1×1012/cm2的条件,注入N型杂质的离子态磷,在基片表面上形成N型杂质层51。除去抗蚀剂后,如图59所示,利用1100℃-1200℃、0.5小时-3小时的热处理进行磷扩散,形成N型杂质层5。

其中,在注入磷的杂质浓度低的情况下、热处理温度高的情况下、或热处理时间长的情况下,如图60所示,在形成N型杂质层5的区域就形成像实施例1中那样的P型杂质层2,并且即使形成了P型杂质层2也不存在特殊的问题。

然后,如图61所示,在再次对抗蚀剂40构图、并对存储单元区的反常规P阱形成区开口之后,按200keV-1.5MeV、1×1012~1×1014/cm2的条件,高能量注入P型杂质的离子态硼,形成反常规P阱3。

然后,如图62所示,在对抗蚀剂40构图、并对逻辑电路区内的NMOSFET形成部分开口之后,按200keV-1.5MeV、1×1012~1×1014/cm2的条件,高能量注入P型杂质的离子态硼,形成反常规P阱8。

然后,如图63所示,在对抗蚀剂40构图、并对逻辑电路区内的PMOSFET形成部分开口之后,按300keV-2.5MeV、1×1012~1×1014/cm2的条件,高能量注入N型杂质的离子态磷,形成反常规N阱4和9。此后,形成晶体管、层间绝缘膜、接触孔、电容等,进行布线(图中未示出)。

再有,并不在乎分别同时形成或单独形成反常规P阱3、8和反常规N阱4、9。此外,其形成顺序也可适当变更。

如上所述,按照这种半导体器件的制造方法,在半导体基片1中由α线等产生的电子使的相对于反常规阱上部的势垒变大,妨碍电子到达已形成在反常规P阱3上的源/漏区,可获得能抑制因电子而产生的软错误的半导体器件。

此外,通过使半导体基片1、反常规P阱3和P型杂质层2或N型杂质层5电气导通,就不必单独地固定各自的电位。因此,没有因端子数增加在元件配置上受到制约,还使微细化的半导体集成电路的制造成为可能。

实施例9

图64是表示本发明实施例9的半导体器件基片的剖面图,图65是表示本发明实施例9的半导体器件的其它基片的剖面图。下面参照图,1是P型半导体基片,5是P型半导体基片1中形成的N型杂质层,3和8是P型半导体基片1中形成的反常规P阱,4和9是反常规N阱,10是P型杂质层。

图66是表示图64所示的半导体基片C-C’剖面中杂质浓度的分布图。此外,图64所示的半导体基片B-B’剖面中杂质浓度的分布就像图10所示的那样。

与实施例8一样,这种半导体器件大体分为以存储主要容量的信息为目的的元件区(存储单元区)和一边获取存储单元区的大量信息一边以进行逻辑运算为目的的元件区(逻辑电路区)。

存储单元区主要由NMOSFET构成,与实施例8有相同的结构。逻辑电路区主要由CMOSFET构成。

在反常规P阱8、反常规N阱4和反常规N阱9上形成多个或单个晶体管(图中未示出)、形成逻辑电路区的CMOS。这种情况下,也在反常规阱内距表面0-0.2μm深度处,有形成具有防止穿通及阈值控制作用的沟道注入层、和在隔离氧化膜24下面抑制沟道形成的阻断沟道注入等的杂质层的情况。

此外,通过在反常规N阱4和反常规P阱3上分别形成晶体管,也可以形成作为逻辑电路的CMOS。这时,在反常规P阱3上形成作为存储单元的晶体管。此时,在图65所示的P型杂质层10未形成的区中也可以经扩散形成反常规P阱3,通过它可维持逻辑电路区的耐闭锁性。

按照本半导体器件存储单元区的基片结构,由图10可知,在P型半导体基片1中由α线等产生的电子的相对于反常规阱上部的势垒,因N型杂质层5的存在变大,妨碍电子到达已形成在反常规P阱3表面上的源/漏区,具有抑制软错误的效果。

此外,使半导体基片1、反常规P阱3和8、P型杂质层10和N型杂质层5或P型杂质层2电气导通时,不必分别单独地固定各自的电位。因此,没有因端子数增加在元件配置上受到制约,在半导体集成电路微细化上也有效果。

并且,因逻辑电路区中存在P型埋置层10,使基片阻抗减小,对必须有特别高耐闭锁性的逻辑电路区可提高有效的耐闭锁性。这时,从提高耐闭锁性的观点来看,期望P型埋置层的峰值浓度高于P阱的峰值浓度。

图67是表示本发明实施例9的半导体器件基片制造方法的剖面图。

首先,与实施例8一样,在硼浓度为1×1015/cm3的P型半导体基片1的主表面的元件隔离区上形成元件隔离氧化膜24、在有源区形成下敷氧化膜29之后,在存储单元区形成低浓度N型层5。

其中,在注入磷的杂质浓度低的情况下,热处理温度高时,或热处理时间长时,如图60所示,在形成N型杂质层5的区域就形成像实施例1中那样的P型杂质层2,并且即使形成了P型杂质层2也不存在特殊的问题。

然后,如图67所示,对抗蚀剂40构图、对存储单元区开口之后,按500keV-10MeV、5×1012~1×1016/cm2的条件,高能量注入P型杂质的离子态硼,形成P型杂质层10。

然后,与实施例8一样,形成反常规P阱3、反常规P阱8、反常规N阱4和9。

这里,并不在乎分别形成反常规P阱3、4、8和9、P型杂质层10的顺序相反与否。

然后,形成晶体管、层间绝缘膜、接触孔、电容等,进行布线(图中未示出)。

如上所述,按照这种半导体器件的制造方法,在半导体基片1中由α线等产生的电子的相对于反常规阱上部的势垒变大,妨碍电子到达形成在反常规P阱3表面上的源/漏区,可获得能抑制因电子而产生的软错误的半导体器件。

此外,利用半导体基片1、反常规P阱3和8、P型杂质层10和N型杂质层5或P型杂质层2为同一导电型并是电气导通的,所以不必分别单独地固定各自的电位。因此,没有因端子数增加在元件配置上受到制约,使半导体集成电路微细化的制造成为可能。

并且,因逻辑电路区中存在P型埋置层10,使基片阻抗减小,可获得对必须有特别高耐闭锁性的逻辑电路区提高有效的耐闭锁性的半导体器件的制造方法。这时,从提高耐闭锁性的观点来看,期望P型埋置层的峰值浓度高于P阱的峰值浓度。

实施例10

图68是表示本发明实施例10的半导体器件基片的剖面图。下面参照图,6是P型半导体基片,5是P型半导体基片6中形成的N型杂质层,2是P型半导体基片6中形成的P型杂质层,3和8是P型半导体基片6中形成的反常规P阱,4和9是反常规N阱。

这种半导体器件大体区分为以在储主要容量的信息为目的的元件区(存储单元区)和一边获取存储单元区的大量信息一边以进行逻辑运算为目的的元件区(逻辑电路区)。存储单元区主要由NMOSFET构成,逻辑电路区主要由CMOSFET构成。

而且,半导体基片的杂质结构、存储单元区与实施例3一样,逻辑电路与实施例4一样。

在反常规P阱3上形成多个或单个晶体管(图中未示出)。在反常规P阱内距表面0-0.2μm深度处,有形成具有防止穿通及阈值控制作用的沟道注入层、和在隔离氧化膜24下面抑制沟道形成的阻断沟道注入等的杂质层的情况。N型杂质层5在靠近反常规P阱3的底部形成,也可以不在相关的反常规阱的侧面形成,那一种情况部可以。

在反常规P阱8、反常规N阱4和反常规N阱9上形成多个或单个晶体管(图中未示出),并形成逻辑电路区的CMOS。这种情况下,也在反常规阱内距表面0-0.2μm深度处,有形成具有防止穿通及阈值控制作用的沟道注入层、和在隔离氧化膜24下面抑制沟道形成的阻断沟道注入等的杂质层的情况。

此外,通过在反常规N阱4和反常规P阱3上分别形成晶体管,也可以形成作为逻辑电路的CMOS。这时,在反常规P阱3上也形成了作为存储单元的晶体管。此时,如实施例9所示那样的P型杂质层2未形成的区中也可以经扩散形成反常规P阱3,通过它可维持逻辑电路区的CMOSFET的耐闭锁性。

按照本半导体器件存储单元区的基片结构,在P型半导体基片6中由α线等产生的电子的相对于反常规阱上部的势垒,因N型杂质层5的存在而未变大,由于P型半导体基片6中的电子寿命变短,妨碍电子到达已形成在反常规P阱3表面上的源/漏区,具有抑制软错误的效果。

此外,半导体基片6、P型杂质层2、N型杂质层5、反常规P阱3和8是电气导通的,不必分别单独地固定各自的电位。因此,没有因端子数增加在元件配置上受到制约,在半导体集成电路微细化上也有效果。

并且,由于半导体基片6的杂质浓度高,使基片阻抗变低,可提高逻辑电路区的耐闭锁性。

再有,由于利用外延生长形成N型杂质层5,所以可获得P型半导体基片6的浓度较高、形成晶体管的反常规P阱3的表面杂质浓度较低的半导体器件,因此,在使P型半导体基片6和反常规阱的导通变得容易的同时,还可防止抑制阈值电压等的晶体管特性的劣化。

图69是表示本发明实施例10的半导体器件基片制造方法的剖面图。

首先,如图69所示,在硼浓度为1×1018/cm3的P型硅基片6的主表面上形成2-10μm的硼浓度为1×1015/cm3的P型外延层。

接着,形成P型杂质层2的表面隔离区中的元件隔离氧化膜24,在有源区形成作为栅氧化膜的下敷氧化膜29。但是,并不在乎元件隔离氧化膜24与下敷氧化膜29形成顺序的先后。

然后,与实施例8一样形成N型杂质层5、反常规P阱3和8、反常规N阱4和9、晶体管等。

如上所述,按照这种半导体器件的制造方法,在半导体基片6中由α线等产生的电子使反常规阱上部的势垒变大,妨碍电子到达已形成在反常规P阱3上的源/漏区,可获得能抑制因电子而产生的软错误的半导体器件的制造方法。

此外,利用半导体基片6、反常规P阱3和8、P型杂质层2和N型杂质层5为同一导电型并是电气导通的,所以不必分别单独地固定各自的电位。因此,没有因端子数增加在元件配置上受到制约,使微细化的半导体集成电路的制造成为可能。

此外,由于半导体基片6的杂质浓度高使基片阻抗变低,所以可获得能提高逻辑电路中的耐闭锁性的半导体器件的制造方法。

再有,由于利用外延生长形成N型杂质层5,所以可获得P型半导体基片6的浓度较高、形成晶体管的反常规P阱3的表面杂质浓度较低的半导体器件。因此,使P型半导体基片6和反常规阱的导通变得容易的同时,还可防止抑制阈值电压等的晶体管特性的劣化,在制造工艺上,也可较宽地设定杂质浓度控制等的工艺条件的范围。

实施例11

图70是表示本发明实施例11的半导体器件基片的剖面图。下面参照图,6是P型半导体基片,5是P型半导体基片6中形成的N型杂质层,10是P型半导体基片6中形成的P型杂质层,3和8是P型半导体基片6中形成的反常规P阱,4和9是反常规N阱。

这种半导体器件大体区分为以存储主要容量的信息为目的的元件区(存储单元区)和一边获取存储单元区的大量信息一边以进行逻辑运算为目的的元件区(逻辑电路区)。存储单元区主要由NMOSFET构成,逻辑电路区主要由CMOSFET构成。

图71是表示图70所示的半导体基片C-C’剖面中杂质浓度的分布图。此外,图70所示的半导体基片B-B’剖面中杂质浓度的分布与实施例4一样如图33所示。

在反常规P阱3上形成多个或单个晶体管(图中未示出)。然后,在反常规P阱3内距表面0-0.2μm深度处,有形成具有防止穿通及阈值控制作用的沟道注入层、和在隔离氧化膜24下面抑制沟道形成的阻断沟道注入等的杂质层的情况。N型杂质层5在靠近反常规P阱3的底部形成,也可以不在相关的反常规阱的侧面形成,那一种情况都可以。

在反常规P阱8、反常规N阱4和反常规N阱9上形成多个或单个晶体管(图中未示出),并形成逻辑电路区的CMOS。这种情况下,也在反常规阱内距表面0-0.2μm深度处,有形成具有防止穿通及阈值控制作用的沟道注入层、和在隔离氧化膜24下面抑制沟道形成的阻断沟道注入等的杂质层的情况。

此外,通过在反常规N阱4和反常规P阱3上分别形成晶体管,也可以形成作为逻辑电路的CMOS。这时,在反常规P阱3上也形成了作为存储单元的晶体管。此时,如实施例9所示那样的P型杂质层10未形成的区中也可以经扩散形成反常规P阱3,通过它可维持逻辑电路区的CMOSFET的耐闭锁性。

按照这种半导体器件的存储区的基片结构,在半导体基片6中由α线等产生的电子的相对于反常规阱上部的势垒因N型杂质层5的存在变大,妨碍电子到达在反常规P阱3表面上形成的源/漏区,具有抑制软错误的效果。

此外,半导体基片6、反常规P阱3和8、P型杂质层10和N型杂质层5或P型杂质层2是电气导通的,不必分别单独地固定各自的电位。因此,没有因端子数增加在元件配置上受到制约,在半导体集成电路微细化上也有效果。

并且,由于不仅半导体基片6的杂质浓度较高,并且在逻辑电路区中存在P型埋置层10,使基片阻抗减小,所以对必须有特别高耐闭锁性的逻辑电路区可提高有效的耐闭锁性。这时,从提高耐闭锁性的观点来看,期望P型杂质层的峰值浓度高于反常规P阱3的峰值浓度。

图72是表示本发明实施例11的半导体器件基片制造方法的剖面图。

首先,与实施例10一样,在硼浓度为1×1018/cm3的P型硅基片6的主表面上的单元隔离区中形成单元分氧化离膜24、在有源区形成下敷氧化膜29后,在存储单元区形成低浓度N型层。

其中,在注入磷的杂质浓度低的情况下,热处理温度高时,或热处理时间长时,在形成N型杂质层5的区域中形成像实施例1中那样的P型杂质层2,并且即使形成了P型杂质层2也不存在特殊的问题。

然后,如图反常规反常规反常规所示,对抗蚀剂构图、存储单元区开口之后,按500keV-10MeV、5×1012~1×1016/cm2的条件,高能量注入P型杂质的离子态硼,形成P型杂质层10。

然后,与实施例8一样,形成反常规P阱3、反常规P阱8、反常规N阱4和9、晶体管等。

这里,并不在乎反常规P阱3、4、8和9、P型杂质层10的形成顺序相反与否。

此后,形成晶体管、层间绝缘膜、接触孔、电容等,进行布线(图中未示出)。

如上所述,按照这种半导体器件的制造方法,在半导体基片6中由α线等产生的电子的相对于反常规阱上部的势垒变大,妨碍电子到达形成在反常规P阱3表面上的源/漏区,可获得能抑制因电子而产生的软错误的半导体器件。

此外,利用半导体基片1、反常规P阱3和8、P型杂质层10和N型杂质层5或P型杂质层2为同一导电型并是电气导通的,所以不必分别单独地固定各自的电位。因此,没有因端子数增加在元件配置上受到制约,使半导体集成电路微细化的制造成为可能。

并且,由于在逻辑电路区中存在P型埋置层10,使基片阻抗减小,所以可获得对必须有特别高耐闭锁性的逻辑电路区可提高有效的耐闭锁性的半导体器件制造的方法。这时,从提高耐闭锁性的观点来看,期望P型埋置层的峰值浓度高于反常规P阱的峰值浓度。

实施例12

图73是表示本发明实施例12的半导体器件基片的剖面图。下面参照图,6是P型半导体基片,7是P型半导体基片6中形成的N型杂质层,2是P型半导体基片6中形成的P型杂质层,3和8是P型半导体基片6中形成的反常规P阱,4和9是反常规N阱。

这种半导体器件大体区分为以存储主要容量的信息为目的的元件区(存储单元区)和一边获取存储单元区的大量信息一边以进行逻辑运算为目的的元件区(逻辑电路区)。存储单元区主要由NMOSFET构成,逻辑电路区主要由CMOSFET构成。

而且,半导体基片的杂质结构、存储单元区与实施例5一样,逻辑电路区与实施例3相同。

在反常规P阱3上形成多个或单个晶体管(图中未示出)。然后,在反常规P阱内距表面0-0.2μm深度处,有形成具有防止穿通及阈值控制作用的沟道注入层、和在隔离氧化膜24下面抑制沟道形成的阻断沟道注入等的杂质层的情况。

N型杂质层7在靠近反常规P阱3的底部形成,也可以不在相关的反常规阱的侧面形成,那一种情况都可以。但是,利用N型杂质层7和反常规N阱4,分隔反常规P阱3和P型杂质层。

在反常规P阱8、反常规N阱4和反常规N阱9上形成多个或单个晶体管(图中未示出),并形成逻辑电路区的CMOS。这种情况下,也在反常规阱内距表面0-0.2μm深度处,有形成具有防止穿通及阈值控制作用的沟道注入层、和在隔离氧化膜24下面抑制沟道形成的阻断沟道注入等的杂质层的情况。

按照这种半导体器件的基片结构,利用高浓度的P型半导体基片6,不仅使存储单元区的P型半导体基片6中的电子的寿命变短,而且由于利用反常规N阱4、N型杂质层7电气隔离反常规P阱3,妨碍P型半导体基片6中由α线产生的电子到达在反常规P阱3表面上形成的源/漏区,具有抑制软错误的效果。

此外,由于隔离了存储单元区的反常规P阱3和逻辑电路区的反常规P阱8、反常规N阱4和9,所以可有不同的电位,并能用不同的基片偏压进行动作。

此外,半导体基片6、P型杂质层2和反常规P阱8是电气导通的,不必分别单独地固定各自的电位。因此,没有因端子数增加在元件配置上受到制约,在半导体集成电路微细化上也有效果。

而且,由于半导体基片6的浓度高,使基片阻抗变低,具有提高逻辑电路区的耐闭锁性的效果。

图74是表示本发明实施例12的半导体器件基片制造方法的剖面图。

首先,如图74所示,在硼浓度为1×1018/cm3的P型硅基片6的主表面上形成P型杂质层2,在其表面的元件分隔区形成元件分隔氧化膜24、在有源区形成下敷氧化膜29。

然后,如图74所示,对抗蚀剂构图、存储单元区开口之后,按500keV-10MeV、1×1012~5×1014/cm2的条件,高能量注入N型杂质的离子态磷,形成N型杂质层7。

然后,与实施例8一样,形成反常规P阱3、反常规P阱8、反常规N阱4和9。

这里,并不在乎分别形成反常规P阱3、4、8和9、N型杂质层7的顺序相反与否。

此后,形成晶体管、层间绝缘膜、接触孔、电容等,进行布线(图中未示出)。

按照这种半导体器件的制造方法,由于通过分隔存储区的反常规P阱3和逻辑电路区的反常规P阱8、反常规N阱4和9,可获得有不同电位、可用不同的基片偏压进行动作的半导体器件。

按照这种半导体器件的基片结构,利用高浓度的P型半导体基片6,不仅使存储单元区的P型半导体基片6中的电子的寿命变短,而且由于利用反常规N阱4、N型杂质层7电气隔离反常规P阱3,妨碍P型半导体基片6中由α线产生的电子到达在反常规P阱3表面上形成的源/漏区,可获得能进一步抑制软错误的半导体器件的制造方法。

而且,由于半导体基片6的浓度高,使基片阻抗变低,具有提高逻辑电路区的耐闭锁性的效果。

再有,由于利用外延生长形成P型杂质层2,所以在逻辑电路中,可获得P型半导体基片6的浓度较高、形成晶体管的反常规P阱3的表面杂质浓度较低的半导体器件。因此,使P型半导体基片6、P型杂质层2和反常规P阱8的导通变得容易的同时,还可防止抑制阈值电压等的晶体管特性的劣化,在制造工艺上,也可较宽地设定杂质浓度控制等的工艺条件的范围。

而且,在逻辑电路中,由于不必固定各自单独的电位,所以没有因端子数增加在元件配置上受到制约,使微细化的半导体集成电路的制造成为可能。

实施例13

图75是表示本发明实施例13的半导体器件基片的剖面图。下面参照图,6是P型半导体基片,7是P型半导体基片6中形成的N型杂质层,10是P型半导体基片6中形成的P型杂质层,3和8是P型半导体基片6中形成的反常规P阱,4和9是反常规N阱。

这种半导体器件大体区分为以存储主要容量的信息为目的的元件区(存储单元区)和以一边获取存储单元区的大量信息一边进行逻辑运算为目的的元件区(逻辑电路区)。存储单元区主要由NMOSFET构成,逻辑电路区主要由CMOSFET构成。

而且,半导体基片的杂质结构、存储单元区与实施例5一样,逻辑电路区与实施例11相同。

在反常规P阱3上形成多个或单个晶体管(图中未示出)。然后,在反常规P阱内距表面0-0.2μm深度处,有形成具有防止穿通及阈值控制作用的沟道注入层、和在隔离氧化膜24下面抑制沟道形成的阻断沟道注入等的杂质层的情况。

N型杂质层7在靠近反常规P阱3的底部形成,也可以不在相关的反常规阱的侧面形成,那一种情况都可以。但是,利用N型杂质层7和反常规N阱4,分隔反常规P阱3和P型杂质层2。

在反常规P阱8、反常规N阱4和反常规N阱9上形成多个或单个晶体管(图中未示出),并形成逻辑电路区的CMOS。这种情况下,也在反常规阱内距表面0-0.2μm深度处,有形成具有防止穿通及阈值控制作用的沟道注入层、和在隔离氧化膜24下面抑制沟道形成的阻断沟道注入等的杂质层的情况。

按照这种半导体器件的基片结构,利用高浓度的P型半导体基片6,不仅使存储单元区的P型半导体基片6中的电子的寿命变短,而且由于利用反常规N阱4、N型杂质层7电气隔离反常规P阱3,妨碍P型半导体基片6中由α线产生的电子到达在反常规P阱3表面上形成的源/漏区,具有抑制软错误的效果。

此外,由于通过分隔存储区的反常规P阱3和逻辑电路区的反常规P阱8、反常规N阱4和9,所以可获得不同的电位,能用不同的基片偏压进行动作。

逻辑电路中,半导体基片6、、P型杂质层10和反常规P阱8是电气导通的,不必分别单独地固定各自的电位。因此,没有因端子数增加在元件配置上受到制约,在半导体集成电路微细化上也有效果。

而且,由于半导体基片6的浓度高,使基片阻抗变低,具有提高逻辑电路区的耐闭锁性的效果。

图76是表示本发明实施例13的半导体器件基片制造方法的剖面图。

首先,与实施例12一样,在硼浓度为1×1018/cm3的P型半导体基片6的主表面上形成P型杂质层2。然后,在其表面的元件分隔区形成元件分隔氧化膜24、在有源区形成下敷氧化膜29。

然后,如图76所示,对抗蚀剂构图、存储单元区开口之后,按500keV-10MeV、5×1012~1×1016/cm2的条件,高能量注入P型杂质的离子态硼,形成P型杂质层10。

然后,与实施例8一样,形成反常规P阱3、反常规P阱8、反常规N阱4和9。

这里,并不在乎分别形成反常规P阱3、4、8和9、N型杂质层7的顺序相反与否。

此后,形成晶体管、层间绝缘膜、接触孔、电容等,进行布线(图中未示出)。

按照这种半导体器件的制造方法,由于通过分隔存储单元区的反常规P阱3和逻辑电路区的反常规P阱8、反常规N阱4和9,可获得有不同电位、可用不同的基片偏压进行动作的半导体器件。

再有,利用高浓度的P型半导体基片6,不仅使存储单元区的P型半导体基片6中的电子的寿命变短,还由于利用反常规N阱4、N型杂质层7电气分隔反常规P阱3,所以妨碍P型半导体基片6中由α线产生的电子到达在反常规P阱3表面上形成的源/漏区,可获得进一步抑制软错误的半导体器件的制造方法。

由于在逻辑电路区中存在着高浓度的P型半导体基片6和混合的P型埋置层10,使基片阻抗减小,所以可获得对必须有特别高耐闭锁性的逻辑电路区可提高有效的耐闭锁性的半导体器件制造的方法。这时,从提高耐闭锁性的观点来看,期望P型埋置层的峰值浓度高于反常规P阱的峰值浓度。

再有,由于利用外延生长形成P型杂质层2,所以在逻辑电路中,可获得P型半导体基片6的浓度较高、形成晶体管的反常规阱的表面杂质浓度较低的半导体器件。因此,使P型半导体基片6、P型杂质层10和反常规P阱8的电导通变得容易的同时,还可防止抑制阈值电压等的晶体管特性的劣化,在制造工艺上,也可较宽地设定杂质浓度控制等的工艺条件的范围。

而且,由于不必固定各自单独的电位,所以没有因端子数增加在元件配置上受到制约,使微细化的半导体集成电路的制造成为可能。

由于有如上所述的结构,所以本发明具有以下效果。

本发明是利用比半导体基片浓度低的第2杂质层的存在,使半导体基片中由α线产生的电子的相对于元件形成区中的势垒变大,由于妨碍了电子到达元件,所以可抑制因电子产生的软错误。

再有,由于半导体基片与第1杂质层为同一导电型、第2杂质层的浓度低,所以电导通时,不必固定各自单独的电位。因此,没有因端子数增加在元件配置上受到制约,在半导体集成电路微细化上也有效果。

并且,由于半导体基片的浓度高,使半导体基片中电子的寿命时间变短,防止了电子到达源/漏区,所以具有抑制软错误的效果。

再有,由于第2导电型的第2杂质层的存在,在半导体基片中由α线等产生的电子的元件形成区中的势垒变大,由于妨碍了电子到达元件,所以可进一步抑制因电子产生的软错误。

此外,由于利用第2杂质层缓合了第1杂质层和半导体基片的电场,所以实现了提高半导体器件的耐压的效果。

再有,由于在半导体基片中产生电子的、相对于晶体管形成区的势垒变大,在形成晶体管的第1杂质层表面的杂质浓度低,因而可防止阈值电压等晶体管特性的劣化。

此外,由于利用第2杂质层,使导体基片中产生的电子的相对于反常规阱上部的势垒变大,抑制了电子到达在存储单元区形成的MOS晶体管的源/漏区,所以取得了提高抗软错误性的效果。

再有,半导体基片、第1、第2和第4的杂质层是电气导通的,没有必要固定各自单独的电位。因此,没有因端子数增加在元件配置上受到制约,在半导体集成电路微细化上也有效果。

并且,由于第5杂质层的浓度高,所以,实现了抑制逻辑电路区中形成的CMOS闭锁的效果。

此外,由于利用第2导电型的第2杂质层,不仅使半导体基片中产生的电子的相对于反常规阱上部的势垒变大,并由于隔离了存储单元区,因而进一步抑制了电子到达存储单元区中所形成的MOS晶体管的源/漏区,所以实现了提高耐软错误性的效果。

再有,半导体基片、第4和第5的杂质层是电气导通的,没有必要固定各自单独的电位。因此,没有因端子数增加在元件配置上受到制约,在半导体集成电路微细化上也有效果。

此外,利用形成比半导体基片浓度低的第2杂质层,由于使半导体基片中由α等产生的电子的相对于元件形成区的势垒变大,妨碍了电子到达元件,所以可抑制因电子产生的软错误。

再有,由于半导体基片和第1杂质层为同一导电层、第2杂质层浓度低,电气导通时没有必要分别单独固定各自的电位,所以,没有因端子数增加在元件配置上受到制约,还使微细化的半导体集成电路的制造变为可能。

还有,利用形成具有杂质浓度峰值的第2导电型的第2杂质层,不仅使半导体基片中由α线等产生的电子的相对于元件形成区的势垒变大,还由于半导体基片的杂质浓度还比第2和第3杂质浓度大、半导体基片中的寿命时间变短,所以妨碍了电子到达元件,可获得进一步抑制软错误的半导体器件的制造方法。

并且,由于利用第1杂质层缓和了半导体基片和第2杂质层的电场,所以可获得具有提高耐压效果的半导体器件的制造方法。

再有,由于利用外延生长形成第1杂质层,所以可获得半导体基片浓度较高、形成元件表面的杂质浓度较低的半导体器件。因此,在使半导体基片和第2杂质层的导通变得容易的同时,还可防止阈值电压等晶体管特性的劣化,在制造工艺上,也可较宽地设定杂质浓度控制等的工艺条件的范围。

并且,利用第1杂质层,在半导体基片中由α线等产生的电子的、相对于第2杂质层上部的势垒变大,妨碍了电子到达MOS晶体管的源/漏,可获得抑制因电子产生的软错误的半导体器件的制造方法。

再有,利用第1、第2和第4杂质层和半导体基片是电气导通的,没有必要分别固定各自单独的电位,没有因端子数增加在元件配置上受到制约,使微细化的半导体集成电路的制造成为可能。

由于形成了杂质浓度高的第5杂质层,所以实现了抑制CMOS晶体管闭锁的效果。

并且,利用第2杂质层,在半导体基片中由α线等产生的电子的、相对于第3杂质层上部的势垒变大,妨碍了电子到达MOS晶体管的源/漏,可获得抑制因电子而产生的软错误的半导体器件的制造方法。

再有,利用第1、第5杂质层和半导体基片的电气导通,没有必要分别固定各自单独的电位,没有因端子数增加在元件配置上受到制约,使微细化的半导体集成电路的制造成为可能。

此外,由于第2杂质层的浓度高,所以不仅使半导体基片中由α线等产生的电子的、相对于第3杂质层上部的势垒变得更大,还因隔离了MOS晶体管,妨碍了电子到达MOS晶体管的源/漏,可获得进一步抑制因电子而产生的软错误的半导体器件制造方法。

还有,由于形成了杂质浓度高的第6杂质层,所以实现了抑制CMOS晶体管闭锁的效果。

再有,由于利用外延生长形成第1杂质层,所以可获得半导体基片浓度较高、形成晶体管的第3、第4和第5杂质层的表面杂质浓度较低的半导体器件。因此,在使第1或第6杂质层和第5杂质层及半导体基片的导通变得容易的同时,可防止阈值电压等晶体管特性的劣化,在制造工艺上,也可较宽地设定杂质浓度控制等的工艺条件的范围。

Claims (12)

1.一种半导体器件,包括:

一个第一导电型的半导体基片,它具有一个第一杂质浓度;

一个所述第一导电型的反常规阱,它具有一个带有杂质浓度峰值的第二杂质浓度,形成在所述半导体基片的一个主表面上;

一个第一杂质层,它具有一个第三杂质浓度并且与所述反常规阱的下侧接触,该第三杂质在浓度上小于所述第一杂质浓度的一个杂质浓度峰值和所述第二杂质浓度的杂质浓度峰值;和

一个形成在所述反常规阱上的元件,

其中,所述元件是MOS型晶体管,并且

所述半导体器件还包括一个第二导电型的第二杂质层,它具有一个第四杂质浓度,并且和一个所述第一导电型的具有第五杂质浓度的第三杂质层相邻接,所述第二和所述第三杂质层形成在所述半导体基片的另一个主表面上,和

一个CMOS晶体管,它形成在至少所述第二和所述第三杂质层上,用于控制所述MOS型晶体管。

2.根据权利要求1所述的半导体器件,

其特征在于,一个所述第一导电型的第四杂质层形成在至少所述第二和第三杂质层下面。

3.根据权利要求1所述的半导体器件,

其特征在于,所述第一杂质层是所述第二导电型的。

4.根据权利要求1所述的半导体器件,

其特征在于,所述第二杂质浓度的杂质浓度峰值和所述第三杂质浓度的一个杂质浓度峰值在浓度上小于所述第一杂质浓度的杂质浓度峰值。

5.根据权利要求4所述的半导体器件,

其特征在于,一个所述第一导电型的第五杂质层形成在至少所述第二和第三杂质层下面。

6.根据权利要求4所述的半导体器件,

其特征在于,所述第一杂质层是所述第二导电型的。

7.根据权利要求4所述的半导体器件,

其特征在于,所述MOS型晶体管是构成一个存储器单元的晶体管。

8.根据权利要求4所述的半导体器件,

其特征在于,所述第一杂质层较形成在所述半导体基片的主表面上的一个隔离绝缘膜形成得更深。

9.根据权利要求1所述的半导体器件,

其特征在于,所述MOS型晶体管是构成一个存储器单元的晶体管。

10.根据权利要求1所述的半导体器件,

其特征在于,所述第一杂质层较形成在所述半导体基片的主表面上的一个隔离绝缘膜形成得更深。

11.根据权利要求1所述的半导体器件,

其特征在于,所述第五杂质浓度具有一个杂质浓度峰值,并且所述第二杂质浓度的杂质浓度峰值和所述第五杂质浓度形成在距离所述半导体基片的表面的大致相同的深度,并且具有接近相同的浓度。

12.根据权利要求11所述的半导体器件,

其特征在于,所述第二杂质浓度的杂质浓度峰值和所述第三杂质浓度在浓度上小于所述第一杂质浓度的杂质浓度峰值。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP223939/1996 | 1996-08-26 | ||

| JP223939/96 | 1996-08-26 | ||

| JP22393996A JP3958388B2 (ja) | 1996-08-26 | 1996-08-26 | 半導体装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB2003101163756A Division CN1306615C (zh) | 1996-08-26 | 1997-08-22 | 半导体器件及其制造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1185658A CN1185658A (zh) | 1998-06-24 |

| CN1153295C true CN1153295C (zh) | 2004-06-09 |

Family

ID=16806078

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB971186790A Expired - Fee Related CN1153295C (zh) | 1996-08-26 | 1997-08-22 | 半导体器件及其制造方法 |

| CNB2003101163756A Expired - Fee Related CN1306615C (zh) | 1996-08-26 | 1997-08-22 | 半导体器件及其制造方法 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB2003101163756A Expired - Fee Related CN1306615C (zh) | 1996-08-26 | 1997-08-22 | 半导体器件及其制造方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US6420763B1 (zh) |

| JP (1) | JP3958388B2 (zh) |

| KR (1) | KR19980018840A (zh) |

| CN (2) | CN1153295C (zh) |

| DE (1) | DE19734512A1 (zh) |

| TW (1) | TW356597B (zh) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6423615B1 (en) * | 1999-09-22 | 2002-07-23 | Intel Corporation | Silicon wafers for CMOS and other integrated circuits |

| US6440805B1 (en) * | 2000-02-29 | 2002-08-27 | Mototrola, Inc. | Method of forming a semiconductor device with isolation and well regions |

| US7145191B1 (en) | 2000-03-31 | 2006-12-05 | National Semiconductor Corporation | P-channel field-effect transistor with reduced junction capacitance |

| JP2003078032A (ja) | 2001-09-05 | 2003-03-14 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| JP2003158204A (ja) * | 2001-11-22 | 2003-05-30 | Mitsubishi Electric Corp | 半導体記憶装置およびその製造方法 |

| JP4232477B2 (ja) * | 2003-02-13 | 2009-03-04 | パナソニック株式会社 | 半導体集積回路の検証方法 |

| EP1683193A1 (en) * | 2003-10-22 | 2006-07-26 | Spinnaker Semiconductor, Inc. | Dynamic schottky barrier mosfet device and method of manufacture |

| JP2005142321A (ja) | 2003-11-06 | 2005-06-02 | Nec Electronics Corp | 半導体集積回路装置およびその製造方法 |

| CN101019236A (zh) * | 2004-07-15 | 2007-08-15 | 斯平内克半导体股份有限公司 | 金属源极功率晶体管及其制造方法 |

| US20060049464A1 (en) * | 2004-09-03 | 2006-03-09 | Rao G R Mohan | Semiconductor devices with graded dopant regions |

| JP2006344735A (ja) * | 2005-06-08 | 2006-12-21 | Seiko Epson Corp | 半導体装置 |

| EP1935019A1 (en) * | 2005-10-12 | 2008-06-25 | Spinnaker Semiconductor, Inc. | A cmos device with zero soft error rate |

| DE102006023876A1 (de) * | 2006-05-19 | 2007-11-22 | Carl Zeiss Smt Ag | Optische Abbildungseinrichtung |

| US7872903B2 (en) * | 2009-03-19 | 2011-01-18 | Altera Corporation | Volatile memory elements with soft error upset immunity |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4442591A (en) * | 1982-02-01 | 1984-04-17 | Texas Instruments Incorporated | High-voltage CMOS process |

| US4470191A (en) * | 1982-12-09 | 1984-09-11 | International Business Machines Corporation | Process for making complementary transistors by sequential implantations using oxidation barrier masking layer |

| US4633289A (en) | 1983-09-12 | 1986-12-30 | Hughes Aircraft Company | Latch-up immune, multiple retrograde well high density CMOS FET |

| US4710477A (en) | 1983-09-12 | 1987-12-01 | Hughes Aircraft Company | Method for forming latch-up immune, multiple retrograde well high density CMOS FET |

| DE3340560A1 (de) * | 1983-11-09 | 1985-05-15 | Siemens AG, 1000 Berlin und 8000 München | Verfahren zum gleichzeitigen herstellen von schnellen kurzkanal- und spannungsfesten mos-transistoren in vlsi-schaltungen |

| US4764482A (en) * | 1986-11-21 | 1988-08-16 | General Electric Company | Method of fabricating an integrated circuit containing bipolar and MOS transistors |

| JPS6410656A (en) * | 1987-07-03 | 1989-01-13 | Hitachi Ltd | Complementary type semiconductor device |

| CN1020028C (zh) * | 1987-08-18 | 1993-03-03 | 联邦德国Itt工业股份有限公司 | 制作cmos集成电路的注入井和岛的方法 |

| JPH0196962A (ja) * | 1987-10-08 | 1989-04-14 | Nissan Motor Co Ltd | 縦型mosトランジスタおよびその製造方法 |

| JP2660056B2 (ja) | 1989-09-12 | 1997-10-08 | 三菱電機株式会社 | 相補型mos半導体装置 |

| JP2523409B2 (ja) | 1990-05-02 | 1996-08-07 | 三菱電機株式会社 | 半導体記憶装置およびその製造方法 |

| KR950009893B1 (ko) * | 1990-06-28 | 1995-09-01 | 미쓰비시 뎅끼 가부시끼가이샤 | 반도체기억장치 |

| JP2978345B2 (ja) | 1992-11-26 | 1999-11-15 | 三菱電機株式会社 | 半導体装置の製造方法 |

| JPH0758212A (ja) * | 1993-08-19 | 1995-03-03 | Sony Corp | Cmos集積回路 |

| JP2682425B2 (ja) | 1993-12-24 | 1997-11-26 | 日本電気株式会社 | 半導体装置の製造方法 |

| US5393679A (en) | 1994-04-05 | 1995-02-28 | United Microelectronics Corporation | Use of double charge implant to improve retrograde process PMOS punch through voltage |

| JPH07312423A (ja) * | 1994-05-17 | 1995-11-28 | Hitachi Ltd | Mis型半導体装置 |

| US5654213A (en) * | 1995-10-03 | 1997-08-05 | Integrated Device Technology, Inc. | Method for fabricating a CMOS device |

| US5767556A (en) * | 1996-02-21 | 1998-06-16 | Nec Corporation | Field effect transistor |

-

1996

- 1996-08-26 JP JP22393996A patent/JP3958388B2/ja not_active Expired - Fee Related

-

1997

- 1997-07-31 TW TW086110966A patent/TW356597B/zh not_active IP Right Cessation

- 1997-08-08 DE DE19734512A patent/DE19734512A1/de not_active Ceased

- 1997-08-21 KR KR1019970039793A patent/KR19980018840A/ko not_active Application Discontinuation

- 1997-08-22 CN CNB971186790A patent/CN1153295C/zh not_active Expired - Fee Related

- 1997-08-22 CN CNB2003101163756A patent/CN1306615C/zh not_active Expired - Fee Related

- 1997-08-26 US US08/917,528 patent/US6420763B1/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| TW356597B (en) | 1999-04-21 |

| JPH1070250A (ja) | 1998-03-10 |

| US6420763B1 (en) | 2002-07-16 |

| CN1185658A (zh) | 1998-06-24 |

| JP3958388B2 (ja) | 2007-08-15 |

| DE19734512A1 (de) | 1998-03-05 |

| CN1306615C (zh) | 2007-03-21 |

| CN1501504A (zh) | 2004-06-02 |

| US20020020888A1 (en) | 2002-02-21 |

| KR19980018840A (ko) | 1998-06-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1199281C (zh) | 半导体装置 | |

| CN1230888C (zh) | 半导体元件及其制造方法 | |

| CN1187839C (zh) | 半导体装置 | |

| CN1135626C (zh) | 半导体器件及其制造方法 | |

| CN1142586C (zh) | 半导体集成电路器件和制造半导体集成电路器件的方法 | |

| CN1230915C (zh) | Mim电容器 | |

| CN1231978C (zh) | 绝缘栅型半导体装置 | |

| CN1153295C (zh) | 半导体器件及其制造方法 | |

| CN1610118A (zh) | 半导体装置组及其制造方法、半导体装置及其制造方法 | |

| CN1162912C (zh) | 半导体装置及其制造方法 | |

| CN1445838A (zh) | 半导体器件及其制造方法 | |

| CN1221220A (zh) | 具备电容器的半导体装置及其制造方法 | |

| CN1992523A (zh) | 开关电路和二极管 | |

| CN1841744A (zh) | 具有稳定静电放电保护能力的半导体器件 | |

| CN1790912A (zh) | 半导体集成电路装置 | |

| CN1666325A (zh) | 纵向结型场效应晶体管及其制造方法 | |

| CN1976229A (zh) | 半导体集成电路及泄漏电流降低方法 | |

| CN1790743A (zh) | 晶体管及其制造方法 | |

| CN1199248A (zh) | 半导体器件及其制造方法 | |

| CN1967850A (zh) | 半导体装置 | |

| CN1153302C (zh) | 薄膜晶体管 | |

| CN1402356A (zh) | 纵向结构的半导体器件 | |

| CN1613153A (zh) | 半导体存储装置及其制造方法 | |

| CN1783499A (zh) | 半导体存储装置 | |

| CN1256775C (zh) | 半导体器件及其制造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C06 | Publication | ||

| PB01 | Publication | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C17 | Cessation of patent right | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20040609 Termination date: 20100822 |