CN1155066C - 利用注入和横向扩散制造碳化硅功率器件的自对准方法 - Google Patents

利用注入和横向扩散制造碳化硅功率器件的自对准方法 Download PDFInfo

- Publication number

- CN1155066C CN1155066C CNB998071021A CN99807102A CN1155066C CN 1155066 C CN1155066 C CN 1155066C CN B998071021 A CNB998071021 A CN B998071021A CN 99807102 A CN99807102 A CN 99807102A CN 1155066 C CN1155066 C CN 1155066C

- Authority

- CN

- China

- Prior art keywords

- type

- silicon carbide

- injecting

- inject

- carbide substrates

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 229910010271 silicon carbide Inorganic materials 0.000 title claims abstract description 229

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 title claims abstract description 196

- 238000009792 diffusion process Methods 0.000 title claims abstract description 46

- 238000000034 method Methods 0.000 title claims description 57

- 238000002513 implantation Methods 0.000 title 1

- 239000000758 substrate Substances 0.000 claims abstract description 191

- 239000002019 doping agent Substances 0.000 claims abstract description 159

- 238000000137 annealing Methods 0.000 claims abstract description 23

- 238000002347 injection Methods 0.000 claims description 137

- 239000007924 injection Substances 0.000 claims description 137

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 claims description 73

- 229910052782 aluminium Inorganic materials 0.000 claims description 61

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 claims description 61

- 239000004411 aluminium Substances 0.000 claims description 55

- 230000015572 biosynthetic process Effects 0.000 claims description 43

- 229910052757 nitrogen Inorganic materials 0.000 claims description 37

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 claims description 33

- 229910052796 boron Inorganic materials 0.000 claims description 33

- 238000009413 insulation Methods 0.000 claims description 32

- 229910052790 beryllium Inorganic materials 0.000 claims description 28

- ATBAMAFKBVZNFJ-UHFFFAOYSA-N beryllium atom Chemical compound [Be] ATBAMAFKBVZNFJ-UHFFFAOYSA-N 0.000 claims description 27

- 238000004519 manufacturing process Methods 0.000 claims description 22

- 230000035755 proliferation Effects 0.000 claims description 19

- 239000004065 semiconductor Substances 0.000 claims description 9

- 230000005611 electricity Effects 0.000 claims description 8

- 230000005669 field effect Effects 0.000 claims description 7

- 229910044991 metal oxide Inorganic materials 0.000 claims description 5

- 150000004706 metal oxides Chemical class 0.000 claims description 5

- 239000007943 implant Substances 0.000 abstract 6

- 238000005468 ion implantation Methods 0.000 abstract 1

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 14

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 12

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 7

- 229910052759 nickel Inorganic materials 0.000 description 7

- 229910052710 silicon Inorganic materials 0.000 description 7

- 239000010703 silicon Substances 0.000 description 7

- 235000012239 silicon dioxide Nutrition 0.000 description 6

- 239000000377 silicon dioxide Substances 0.000 description 6

- 150000002500 ions Chemical class 0.000 description 5

- 239000000463 material Substances 0.000 description 5

- 230000004913 activation Effects 0.000 description 3

- 230000000873 masking effect Effects 0.000 description 3

- 239000000203 mixture Substances 0.000 description 3

- REDXJYDRNCIFBQ-UHFFFAOYSA-N aluminium(3+) Chemical compound [Al+3] REDXJYDRNCIFBQ-UHFFFAOYSA-N 0.000 description 2

- 229910001423 beryllium ion Inorganic materials 0.000 description 2

- PWOSZCQLSAMRQW-UHFFFAOYSA-N beryllium(2+) Chemical compound [Be+2] PWOSZCQLSAMRQW-UHFFFAOYSA-N 0.000 description 2

- 230000002146 bilateral effect Effects 0.000 description 2

- 229910052799 carbon Inorganic materials 0.000 description 2

- 239000002800 charge carrier Substances 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- 229910002601 GaN Inorganic materials 0.000 description 1

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 1

- 238000004458 analytical method Methods 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 238000010276 construction Methods 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 230000009931 harmful effect Effects 0.000 description 1

- -1 nitrogen ion Chemical class 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 238000001020 plasma etching Methods 0.000 description 1

- 230000001737 promoting effect Effects 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 229920006395 saturated elastomer Polymers 0.000 description 1

- 238000003949 trap density measurement Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7816—Lateral DMOS transistors, i.e. LDMOS transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/0445—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising crystalline silicon carbide

- H01L21/0455—Making n or p doped regions or layers, e.g. using diffusion

- H01L21/046—Making n or p doped regions or layers, e.g. using diffusion using ion implantation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66053—Multistep manufacturing processes of devices having a semiconductor body comprising crystalline silicon carbide

- H01L29/66068—Multistep manufacturing processes of devices having a semiconductor body comprising crystalline silicon carbide the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/16—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only elements of Group IV of the Periodic System

- H01L29/1608—Silicon carbide

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S438/00—Semiconductor device manufacturing: process

- Y10S438/931—Silicon carbide semiconductor

Abstract

通过掩模中的开口在碳化硅衬底中注入p型掺杂剂,形成深p型注入,从而制造碳化硅功率器件。N型掺杂剂通过掩模中相同开口注入到碳化硅衬底中,相对于深p型注入形成浅n型注入。以足以使深p型注入横向扩散到包围浅n型注入的碳化硅衬底表面的温度和时间,进行退火,同时不使p型注入通过浅n型注入纵向扩散到碳化硅衬底表面。因此,通过离子注入可以进行自对准浅和深注入,通过促使具有高扩散系数的p型掺杂充分扩散,同时具有低扩散系数的n型掺杂剂保持相对固定的退火,可以形成很好控制的沟道。因此,可以在n型源周围形成p-基区。可以制造横向和纵向功率MOSFETs。

Description

发明的领域

本发明涉及制造功率器件的方法,特别涉及制造碳化硅功率器件的方法。

发明的背景

功率器件已广泛应用于运载大电流和支持高电压。现代功率器件一般由单晶硅半导体材料制造。一种广泛应用的功率器件是功率金属氧化物半导体场效应晶体管(MOSFET)。在功率MOSFET中,控制信号加于通过可以是二氧化硅但并不限于此的中间隔离层与半导体表面隔开的栅极上。电流通过主要载流子的输运发生传导,同时不存在用于双极晶体管工作的主要载流子注入。功率MOSFETs可以提供优异的安全工作区,可以按单元结构并联。

如所属领域技术人员所公知的,功率MOSFETs可以包括横向结构或纵向结构。在横向结构中,漏、栅和源端在衬底的同一表面上。相反,在纵向结构中,源和漏在衬底的相对表面上。

一种广泛应用的硅功率MOSFET是利用双扩散工艺制造的双扩散MOSFET(DMOSFET)。这些器件中,p-基区和n+源区通过掩模中的同一开口扩散。p-基区再扩散得比n+源区深。p-基区和n+源区间横向扩散的不同形成的表面沟道区。在1996年由PWS Publishing Company出版、由B.J.Baliga撰写的、名为“Power Semiconductor Device(功率半导体器件)”的教科书中,具体在第7章,“Power MOSFET”中,可以发现对包括DMOSFET的功率MOSFET的回顾,这里全文引用该文献。

近年来在功率器件方面的研究还包括碳化硅(SiC)器件应用于功率器件的研究。与硅相比,碳化硅具有宽带隙、高熔点、低介电常数、高击穿场强、高热传导性和高饱和电子漂移速度。这些特征允许碳化硅功率器件可以在比常规硅基功率器件高的温度下、高的功率和低的电阻率下工作。在Bhatnagar等人的“Comparison of6H-SiC,3C-SiC and Si for Power Devices(6H-SiC,3C-SiC和Si用于功率器件)”IEEE Transactions on electron Device,vol。40,1993 pp.645-655中,有对碳化硅器件比硅器件优异的理论分析。在授予Palmour、题为“Power MOSFET in Silicon Carbide(碳化硅中的功率MOSFET)”的美国专利5506421中,介绍了用碳化硅制造的功率MOSFET,该专利现已转让给本发明的受让人。

虽然有这些潜在的优点,但仍然很难用碳化硅制造包括功率MOSFET在内的功率器件。例如,如上所述,双扩散MOSFET(DMOSFET)一般利用双扩散工艺制造在硅上,其中p-基区再扩散得比n+源区深。不幸的是,在碳化硅中,常规p和n型掺杂剂的扩散系数比硅小,所以利用可以接受的扩散时间和温度,难以得到需要的p-基区和n+源区的深度。也可以用离子注入注入p-基区和n+源区。例如,参见Shenoy等人的“High-Voltage Double Implanted Power MSOFET’s(高压双注入型功率MOSFET)in 6H-SiC”,IEEE Electron DeviceLetters,Vol.18,No.3,1997年3月,pp.93-95。然而,很难控制离子注入区的深度和横向延伸范围。另外,需要形成包围源区的表面沟道,所以需要用两个不同的注入掩模。因此,很难对准p-基区和源区,因而可能对器件性能有不良影响。

发明的概述

因此本发明的目的是提供制造包括碳化硅功率MOSFETs的碳化硅功率器件的改进方法。

本发明另一目的是提供制造包括碳化硅功率MOSFETs的碳化硅功率器件的方法,不需要源和p-基区的单独掩蔽。

本发明再一目是提供制造碳化硅功率器件的方法,可以形成可与器件的源区对准的沟道区。

根据本发明,通过以下制造硅化硅功率器件的方法可以实施本发明的这些和其它目的,其中p型掺杂剂通过掩模中的开口注入碳化硅衬底,形成深p型注入,n型掺杂剂通过掩模中的相同开口注入碳化硅衬底,相对于p型注入形成浅n型注入。然后,在足以使深p型注入横向扩散到包围浅n型注入的碳化硅衬底的表面的温度和时间下进行退火,同时不使p型注入通过浅n型注入纵向扩散到碳化硅衬底表面。因此,可以通过离子注入提供自对准的浅和深注入,并可以通过促进具有高扩散系数的p型掺杂剂充分扩散、同时使具有低扩散系数的n型掺杂剂保持相对固定的退火,可以形成很好控制的沟道。由此围绕n型源形成p-基区。

已发现,根据本发明,浅n型注入的存在会阻挡深p型注入通过浅n型注入纵向扩散到碳化硅衬底表面,而是仍然使深p型注入横向扩散到包围n型注入的碳化硅衬底的表面。具体说,尽管不希望受工作理论的限制,但理论表明,氮n型注入可以减少n型区中碳空位,从而防止深p型注入在退火期间扩散到n型源区。因此,可以形成高性能自对准碳化硅功率器件。

应理解,注入p型掺杂剂的步骤可以在注入n型掺杂剂的步骤之前进行。或者,首先进行n型掺杂剂的注入,然后例如通过退火电激活。然后注入p型掺杂剂。还应理解,碳化硅的n型掺杂剂一般包括氮,碳化硅的p型掺杂剂可以包括硼或铍。目前铍是本发明优选的深p型注入掺杂剂,是由于铍可以深注入,同时仍可以与碳化硅衬底产生突变结。

根据本发明的另一方面,在碳化硅衬底的表面任意注入铝阱,电接触横向扩散的深p型注入。然后可以用镍接触接触铝阱和浅n型注入,以提供欧姆接触。

根据本发明,可以通过在碳化硅衬底的表面,将铝阱注入漂移区,制造碳化硅横向功率MOSFETs。掩蔽碳化硅衬底表面的漂移区,在漂移区上限定第一对开口,各开口位于铝阱的相对侧上。p型掺杂剂可以以形成深p型注入的注入能量和剂量,通过该第一对开口,注入到碳化硅衬底。n型掺杂剂可以以相对于深p型注入形成浅n型注入的能量和剂量,通过该第一对开口,注入到碳化硅衬底。应理解,可以首先注入p型掺杂剂,然后注入n型掺杂剂。或者,先注入n型掺杂剂,并激活,然后注入p型掺杂剂。

然后,在碳化硅衬底的表面,掩蔽漂移区,在漂移区上限定第二对开口,各开口远离各浅n型注入,与铝阱相对。n型掺杂剂通过该第二对开口注入到碳化硅衬底中,限定一对漏区。在足以使各深p型注入横向扩散到包围各浅N-注入的碳化硅衬底的表面的温度和时间下,进行退火,同时,不使各深p型注入通过各浅n型注入纵向扩散到碳化硅衬底表面。由此在碳化硅衬底的表面,在横向扩散的p型注入中形成一对沟道区,各沟道区在各铝阱的相对侧上。

在碳化硅衬底表面上,在漂移区上形成一对栅绝缘区,各栅绝缘区与各沟道区接触。然后,在浅n型注入上和两浅n型注入之间的铝阱、在漏区上和一对栅绝缘区上,分别形成公共源接触、一对漏接触和一对栅接触。由此可以形成具有公共源的一对碳化硅横向功率MOSFETs,从而可以形成较大器件单元。

应理解,p型掺杂剂和n型掺杂剂每个都可以以一个能量和剂量一次注入。或者,可以采用多注入能量和剂量,形成浅和/或深注入。如上所述,可以采用氮作n型掺杂剂。可以采用硼更好是用铍作p型掺杂剂。

所属领域的技术人员还应理解,在上述工艺中,可以在掩蔽漂移区后并且注入了浅和深注入后注入铝阱,以便在两浅n型注入之间注入铝阱。另外,可以在注入n型掺杂剂的步骤后,进行先注入p型掺杂剂然后注入n型掺杂剂的步骤。换言之,可以在形成源区之前形成漏区。或者,可以同时进行源的浅n型注入和漏的n型注入。

根据本发明,可以通过在碳化硅衬底表面上,向漂移区注入一对隔开的铝阱制造碳化硅纵向功率MOSFETs。在碳化硅衬底表面,掩蔽漂移区,以便在一对铝阱之间的漂移区上限定第一对开口。通过该第一对开口,在碳化硅衬底中注入p型掺杂剂,形成深p型注入。通过该第一对开口,在碳化硅衬底中注入n型掺杂剂,形成浅n型注入。如上所述,可以在n型掺杂剂之前注入p型掺杂剂,或者,可以注入n型掺杂剂并激活,然后注入p型掺杂剂。

然后,在不使各p型注入通过各浅n型注入纵向扩散到碳化硅衬底表面的条件下,在足以使各p型注入横向扩散到包围各浅n型注入的碳化硅衬底表面的温度和时间,进行退火。由此在两浅n型注入之间,在碳化硅衬底的表面,在横向扩散的p型注入中形成一对沟道区。在一对沟道区上和之间延伸的碳化硅衬底的表面上,形成栅绝缘区。在各浅n型注入和与之相邻的铝阱上、在栅绝缘区上和在与漂移区相对的碳化硅衬底的第二面上,分别形成一对源接触、栅接触和漏接触。

如关于横向功率MOSFET的介绍,可以采用一个能量和剂量或多个能量和剂量进行注入。可以用氮作n型掺杂剂,可以用硼较好是用铍作p型掺杂剂。可以在注入p和n型掺杂剂后形成铝阱,以便铝阱注入在第一对开口之外。因此,自对准方法可以制造包括横向和纵向功率MOSFETs等高性能碳化硅器件。

根据本发明的第一方面,提供一种制造碳化硅功率器件的方法,包括以下步骤:

掩蔽碳化硅衬底的表面,在表面限定开口;

以形成埋藏式深p型注入的注入能量和剂量,通过所说开口向碳化硅衬底注入p型掺杂剂;

以相对于埋藏式深p型注入形成浅n型注入的注入能量和剂量,通过所说开口向碳化硅衬底注入n型掺杂剂;

在不使埋藏式深p型注入通过浅n型注入纵向扩散到碳化硅衬底的表面的条件下,以足以使埋藏式深p型注入横向扩散到包围浅n型注入的碳化硅衬底的表面的温度和时间,进行退火。

根据本发明的第二方面,提供一种制造碳化硅功率器件的方法,包括以下步骤:

掩蔽碳化硅衬底的表面,在表面限定开口;

首先,以形成浅n型注入的注入能量和剂量,通过所说开口向碳化硅衬底注入n型掺杂剂;

电激活所说n型掺杂剂;

然后以相对于浅n型注入形成埋藏式深p型注入的注入能量和剂量,通过所说开口向碳化硅衬底注入p型掺杂剂;

在不使埋藏式深p型通过浅n型注入纵向扩散到碳化硅衬底的表面的条件下,以足以使埋藏式深p型注入横向扩散到包围浅n型注入的碳化硅衬底的表面的温度和时间,进行退火。

根据本发明的第三方面,提供一种制造碳化硅横向功率金属氧化物半导体场效应晶体管的方法,包括以下步骤:

在碳化硅衬底的表面上,在漂移区注入铝阱;

掩蔽碳化硅衬底表面上的漂移区,以便在漂移区上限定第一对开口,各个所说开口位于相应铝阱的相对两侧上;

然后以形成深p型注入的注入能量和剂量,通过第一对开口向碳化硅衬底注入p型掺杂剂;

以相对于深p型注入形成浅n型注入的注入能量和剂量,通过第一对开口向碳化硅衬底注入n型掺杂剂;

在碳化硅衬底的表面上掩蔽漂移区,从而在漂移区上限定第二对开口,各开口远离各相应浅n型注入并与铝阱相对;

通过第二对开口向碳化硅衬底注入n型掺杂剂,以限定一对漏区;

在不使各深p型注入通过各相应浅n型注入纵向扩散到碳化硅衬底的表面的条件下,以足以使各深p型注入横向扩散到包围各浅n型注入的碳化硅衬底的表面的温度和时间,进行退火,从而在碳化硅衬底的表面上,在横向扩散的p型注入中形成一对沟道区,各沟道区位于铝阱的各相应相对侧上;

在碳化硅衬底表面,在漂移区上形成一对栅绝缘区,各栅绝缘区与该对沟道区的相应一个接触;及

在浅n型注入和两浅n型注入间的铝阱上、在漏区上、在所说绝缘区上,分别形成公共源接触、一对漏接触和一对栅接触。

根据本发明的第四方面,提供一种制造碳化硅侧向功率金属氧化物半导体场效应晶体管的方法,包括以下步骤:

在碳化硅衬底表面上,在漂移区中注入铝阱;

掩蔽碳化硅衬底表面上的漂移区,以在漂移区上限定第一对开口,各个开口位于各铝阱的相对两侧上;

首先以形成浅n型注入的注入能量和剂量,通过第一对开口向碳化硅衬底注入n型掺杂剂;

电激活n型掺杂剂;

然后以相对于浅n型注入形成深p型注入的注入能量和剂量,通过第一对开口向碳化硅衬底注入p型掺杂剂;

在碳化硅衬底的表面上掩蔽漂移区,从而在漂移区上限定第二对开口,其中各开口远离各相应浅n型注入并与铝阱相对;

通过第二对开口向碳化硅衬底注入n型掺杂剂,以限定一对漏区;

在不使各深p型注入通过各浅n型注入纵向扩散到碳化硅衬底的表面的条件下,以足以使各深p型注入横向扩散到包围各浅n型注入的碳化硅衬底的表面的温度和时间,进行退火,从而在碳化硅衬底的表面上,在横向扩散的p型注入中形成一对沟道区,其中各沟道区位于铝阱的各相应相对侧上;

在碳化硅衬底表面,在漂移区上形成一对栅绝缘区,各栅绝缘区与各个沟道区接触;及

在浅n型注入和两浅n型注入间的铝阱上、在漏区上、在所说一对绝缘区上,分别形成公共源接触、一对漏接触和一对栅接触。

根据本发明的第五方面,提供一种制造碳化硅纵向功率MOSFET的方法,包括以下步骤:

在碳化硅衬底表面上,在漂移区中注入一对隔开的铝阱;

掩蔽碳化硅衬底表面上的漂移区,以在漂移区上所说一对铝阱之间限定第一对开口;

首先以形成深p型注入的注入能量和剂量,通过第一对开口向碳化硅衬底注入p型掺杂剂;

然后以相对于深p型注入形成浅n型注入的注入能量和剂量,通过第一对开口向碳化硅衬底注入n型掺杂剂;

在不使各深p型注入通过各浅n型注入纵向扩散到碳化硅衬底的表面的条件下,以足以使各深p型注入横向扩散到包围各浅n型注入的碳化硅衬底的表面的温度和时间,进行退火,从而在碳化硅衬底的表面上,在两浅n型注入之间,在横向扩散的p型注入中形成一对沟道区;

在所说一对沟道形成区上和之间延伸的碳化硅衬底表面上,形成一对栅绝缘区;

在相应浅n型注入形成一对源接触、栅接触和漏接触,并分别延伸在与浅n型注入相邻的铝阱上、在所说栅绝缘区上和与漂移区相对的碳化硅衬底的第二表面上。

根据本发明的第六方面,提供一种制造碳化硅纵向功率MOSFET的方法,包括以下步骤:

在碳化硅衬底表面上,在漂移区中注入一对隔开的铝阱;

掩蔽碳化硅衬底表面上的漂移区,以在漂移区上所说一对铝阱间限定第一对开口;

首先以形成浅n型注入的注入能量和剂量,通过第一对开口向碳化硅衬底注入n型掺杂剂;

电激活n型掺杂剂;

然后以相对于浅n型注入形成深p型注入的注入能量和剂量,通过第一对开口向碳化硅衬底注入p型掺杂剂;

在不使各深p型注入通过各浅n型注入纵向扩散到碳化硅衬底的表面的条件下,以足以使各深p型注入横向扩散到包围各浅n型注入的碳化硅衬底的表面的温度和时间,进行退火,从而在碳化硅衬底的表面上,在两浅n型注入之间,在横向扩散的p型注入中形成一对沟道区;

在所说一对沟道形成区上和之间延伸的碳化硅衬底表面,形成一对栅绝缘区;

在浅n型注入形成一对源接触、栅接触和漏接触,并分别延伸在与浅n型注入相邻的铝阱上、在所说栅绝缘区上和与漂移区相对的碳化硅衬底的第二表面上。

附图简介

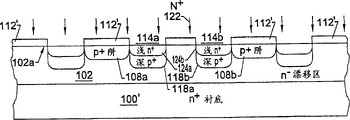

图1A-1G是根据本发明制造碳化硅横向功率MOSFETs的方法的剖面图。

图2是图1G的俯视图。

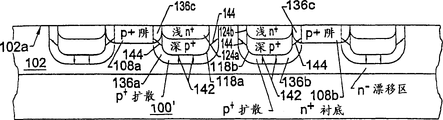

图3A-3G是根据本发明制造碳化硅纵向功率MOSFETs的方法的剖面图。

图4是图3G的俯视图。

图5是展示退火期间硼扩散的示意图。

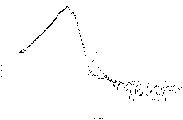

图6和7是展示退火期间铍扩散的曲线图。

图8是展示退火期间氮和硼扩散的曲线图。

优选实施例的详细介绍

下面结合示出了本发明的优选实施例的附图更充分地介绍本发明。然而,本发明可以按许多不同形式实施,不应认为本发明限于这里所记载的实施例;提供这些实施例目的在于完全彻底公开本发明,向所属领域技术人员充分传达本发明的范围。附图中,为清楚起见放大了各层和区的厚度。整个说明书中类似的数字表示类似的部分。应理解,在例如层、区或衬底等部分称作“on”另一部分,可以是直接位于另一部分上或可以存在中间部分、相反,在某一部分称作“directly on”另一部分,是指不存在中间部分。

参见图1A-1G,下面介绍根据本发明制造一对横向功率MOSFET的方法。由于横向功率MOSFETs采用自对准注入和扩散,所以碳化硅横向功率MOSFETs也称作横向注入扩散MOSFETs或LIDMOSFETs。

参见图1A,提供例如半绝缘衬底等衬底100,其上有n-漂移区102。所属领域的技术人员应理解,衬底100可以包括掺杂或未掺杂的碳化硅或晶格与碳化硅匹配的任何其它材料,包括但不限于氮化镓。衬底100优选是半绝缘的,防止相邻器件间通过衬底100纵向导电。

N-型漂移区102可利用外延淀积、注入或其它常规技术形成。应理解,衬底100和n-漂移区102也可以统称作衬底。N-漂移区102的载流子浓度可以为约1012cm-3至1017cm-3,厚度可以为约3微米至约500微米。衬底100的厚度可以为100微米至500微米。衬底100和n-漂移区102的制造对于所属领域的技术人员来说都是公知的,这里无需赘述。

参见图1B,在n-漂移区102的表面102a上构图第一掩模104。第一掩模104可由二氧化硅或其它常规掩蔽材料构成。如图1B所示,第一掩模104限定暴露n-漂移区102的表面102a的一部分的开口。如图1B所示,通过表面102a,任意地向漂移区102注入p型离子,较好是铝离子106,从而在漂移区102中形成任意的p+阱108。如以后将介绍的,p+阱108可以改善与p型扩散区的欧姆接触。然后,去掉第一掩模104。

参见图1C,在n-漂移区102上构图由二氧化硅或其它常规掩蔽材料构成的第二掩模112,在漂移区上限定第一对开口114a和114b,其中各个开口位于p+阱108的相对侧上。然后,通过第一对开口114a和114b,向n-漂移区102注入例如硼或铍离子116等p型掺杂剂,从而在p+阱108的相对侧上形成一对深p+注入118a、118b。如以下将介绍的,由于铍可以形成与漂移区102的突变结,所以深p+注入优选用铍。还应理解,深p+注入118a、118b可利用一个注入和剂量形成,例如通过以180keV的能量,以4×1015cm-2的剂量注入,提供约1016cm-3的载流子浓度。也可以以40keV的能量,以3.2×1015cm-2的剂量注入铍。或者,可以采用多种剂量和/或能量。

参见图1D,不去掉第二掩模112,通过第一和第二开口114a和114b,注入例如氮等n型离子122,形成一对浅n+注入124a、124b。可以采用一种或多种注入,如以下所述。可以提供大于约1018cm-3的载流子浓度。应理解,由于图1C的深p+注入和图1D的浅n+注入使用相同的第二掩模112,所以这些注入可以自对准。

参见图1E,去掉第二掩模112,形成第三掩模126。如图1E所示,可以由二氧化硅或其它常规掩蔽材料构成的第三掩模126在漂移区102的表面102a上限定第二对开口128a、128b。第二对开口128a、128b与各浅n型注入124a、124b隔开,并与p+阱108相对。

再参见图1E,通过第二对开口128a、128b,向n-漂移区102注入例如氮等p型掺杂剂130,形成一对n+漏区134a、134b。然后,去掉第三掩模126。

所属领域的技术人员应理解,图1B、1C、1D和1E的步骤顺序可以改变。所以,例如,可以在形成图1C的深p+注入118a、118b之后,形成图1B的p+阱108,也可以在形成图1D的浅n+注入124a、124b后形成。图1B的p+阱也可以在图1E的n+漏区134a、134b形成后形成。另外,图1C的深p+注入118a、118b可以在形成图1D的浅n+注入124a、124b后形成。如果是这种情况,则较好在注入了浅n+注入124a、124b后,在掩模能允许、且足以电激活n型掺杂剂的温度和时间下进行退火。

图1E的n+漏区134a、134b也可以在形成图1D的浅n+注入124a、124b、图1C的深p+注入118a、118b和/或图1B的p+阱108之前形成。n+漏区134a、134b也可以与图1D的浅n+区124a、124b同时注入。如果n+漏区134a、134b与浅n+注入124a、124b同时注入,则可以在第二掩模112中形成第二对开口128a、128b,从而能够同时注入。

参见图1F,在足以使深p型注入118a、118b横向扩散到包围各浅n型注入124a、124b的碳化硅衬底的表面102a的温度和时间下进行退火,同时不使各深p型注入通过各浅n型注入124a、124b纵向扩散到碳化硅衬底的表面。例如,较好是深p型注入到浅n型注入124a、124b的纵向扩散小于浅n型注入124a、124b的厚度的0.5%。例如,可以在约1600℃下,进行5分钟退火,使深p型注入扩散约1微米。然而,也可以采用其它退火温度和时间。例如,可以用在约1500℃-约1600℃间的退火温度和约1分钟-30分钟的退火时间,使硼从深p型注入在纵向和横向扩散约0.5微米-3微米的距离。

因此,通过如箭头142所示,远离表面102a纵向,如箭头144所示,向着表面102a横向和纵向,从深p+注入118a、118b扩散p+掺杂剂,形成一对p+扩散区136a、136b。如箭头144所示,横向扩散围绕浅n+注入124a、124b扩散到与p+阱108相对的漂移区的表面102a。如区136c所示,也可以发生到p+阱108的横向扩散,从而进一步改善欧姆接触。

最后,参见图1G,形成绝缘栅及源和漏接触。例如,可通过地毯式淀积镍,然后构图地毯式淀积的镍,形成源接触146和一对隔开的漏接触147a、147b。图1G中,源接触146标记为S,漏接触147a、147b标记为D1和D2。如图1G所示,源接触提供在浅n+注入124a、124b上和p+阱108上延伸的公用源接触。漏接触147a、147b分别电接触n+漏134a、134b。

继续图1G的介绍,在n-漂移区102的表面上形成一对栅绝缘区148a、148b,例如二氧化硅,各个栅绝缘区与已横向扩散到n-漂移区102的表面的p+扩散区136a、136b的一部分接触,与p+阱108相对。于是,这些区在碳化硅衬底的表面在横向扩散p型注入中形成一对沟道区150a、150b。因而形成与源区对准的自对准沟道区。然后,在栅绝缘对148a、148b上形成一对栅接触152a、152b。图1G中栅接触标记为G1和G2,可以包括镍。

还应理解,形成图1G所示的绝缘区和接触可以按与上述不同的顺序形成。例如,可以与源接触146和漏接触147a、147b同时形成栅接触152a、152b。优选栅接触152a、152b在形成源接触146和漏接触147a、147b之前形成。

图2是图1G的完成器件的俯视图。如图所示,形成一对共源极LIDMOSFET。应理解,可以在碳化硅衬底上复制这对共源极LIDMOSFET,从而形成单元阵列。另外,如果需要不包括公共源极的单元,则可以复制图1A-1G的左边一半或右边一半。

参见图3A-3G,下面介绍根据本发明形成碳化硅纵向功率MOSFETs的方法。由于这些纵向功率MOSFETs是利用注入和扩散制造的,所以这里也称它们为碳化硅纵向注入扩散MOSFETs(VIDMOSFETs)。

参见图3A,提供包括n-漂移区102的碳化硅衬底100’。由于图3A-3G示出了通过衬底导通的纵向MOSFET的制造方法,所以衬底100’较好是利用已知技术制造的n+导电类型的碳化硅衬底。n+导电类型的碳化硅衬底可以具有约1016cm-3至1019cm-3的载流子浓度。N-漂移区102也可以象图1A所述的那样制造。还应理解,如先前所述,n+衬底100’和n-漂移区102的组合也可以称作衬底。

参见图3B,在碳化硅衬底表面102a,向漂移区102注入一对隔开的p+阱108a、108b。一对隔开的p+阱108a、108b按图1D所示的方式利用包括一对开口的第一掩模104’注入到漂移区102的表面102a中。也如所述,p+阱较好通过注入铝离子106形成。

所属领域的技术人员应理解,纵向碳化硅MOSFETs一般按单元重复。因此,将介绍线110a、和110b间的单元,图3B-3G中和4中标示出了该单元。为方便展示,未示出线110a和110b外的重复单元。

参见图3C,象图1C所示的那样,形成一对开口114a、114b,除改进的第二掩模112’用于在一对铝阱108a、108b之间形成这些开口外。然后,象图1C所示的那样,注入硼更好是铍离子116,形成深p+注入118a、118b。

参见图3D,像已结合图1D介绍的那样,利用相同的第二掩模112’,例如用氮离子122注入浅n+注入124a、124b。

参见图3E,按图1F所示的方式进行退火。应理解,由于图3A-3G示出了纵向MOSFET的制造方法,所以可以省去图1E所示的一对n+漏134a、134b的制造步骤。还应理解,象图1B-1F所示的那样,制造p+阱108a、108b、深p+注入118a、118b、和浅n+注入124a、124b的顺序可以改变。

参见图3F,在浅n型注入124a、124b上形成一对例如包括镍的源接触146a、146b,并在p阱108a、108b上与之相邻延伸,就象图1G所示的那样。在碳化硅衬底100的与n-漂移区102相对的面上形成漏接触147。漏接触147较好也包括镍。

最后,如图3G所示,在漂移区102的表面102a上形成栅绝缘区148,该区在扩散到碳化硅衬底表面的深p型注入136a、136b间和之上延伸,包围各浅n型注入。因此,这些区在浅n型注入之间的碳化硅衬底表面102a上,在横向扩散的p型注入中,形成一对沟道区150a、150b。在栅绝缘区148上形成例如包括镍的栅接触152。如图1G所示的那样,形成栅绝缘区148及源、漏和栅接触的顺序可以改变。

图4是已完成结构的俯视图。图中未示出下表面上的漏接触。

下面介绍对本发明制造碳化硅功率器件的一些附加考虑。

图1B-1G的p+阱108和图3B-3G的108a、108b可以这样形成,利用以25keV的能量和2×1015cm-2的剂量的第一铝注入,和以90keV的能量和4×1015cm-2的剂量的第二铝注入,通过室温或高温下的注入,形成深为0.1微米,载流子浓度为5×1020cm-3的铝阱。1C-1G和图3C-3G的深p+区118a、118b可以这样形成,在室温下,以450keV的第一能量和3.2×1014cm-2的剂量,和以370keV的第二能量和1.5×1014cm-2的剂量,通过注入硼在0.4微米-1微米的深度形成2×1018cm-3的载流子浓度。最后,可以在室温下,利用四次氮的注入,制造图1D-1G和图3D-3G的浅n+注入124a、124b。第一注入以25keV的能量和3×1014cm-2的剂量进行。第二、第三和第四注入分别以60keV、120keV和200keV的能量和6×1014cm-2、8×1014cm-2和1×1015cm-2的剂量进行。在1600℃退火5分钟后,在衬底表面102a上形成宽度为0.3微米的图1G和3G所示沟道区150a、150b。p+扩散区136a、136b的深度可以从衬底表面102a延伸1.5微米。

如上所述,由于铍可以与漂移区102形成突变结,所以深p+注入优选用铍。图5和6比较了退火后硼和铍的扩散情况。

更具体说,图5示出了对于硼来说,在室温下,以180keV的能量和4×1015cm-2的剂量,注入到4H-SiC,提供2.3×1015cm-3的硼载流子浓度时,硼浓度与深度的关系。在1500℃退火10分钟。如图5所示,退火后,所注入的硼扩散,仅逐渐下降。

相反,如图6所示,在室温下,以40keV的能量和3.2×1015cm-2的剂量,在4G-SiC中注入铍,提供1×1019cm-3的铍浓度。如图6所示,在1500℃退火10分钟后,所注入的铍在约1000nm处,以基本恒定的浓度快速下降。因此,对于铍来说,可以发生更深更均匀的扩散,与硼相比,可以与漂移区形成突变结。

图7也示出了退火期间注入的铍的扩散情况。铍在图6所示的条件下注入。如图7所示,在退火温度从1400℃升高到1700℃且恒定的退火时间为3分钟时,扩散深度连续增大,同时可以保持均匀,并表现为突然下降。因此,铍优于硼。

参见图8,该图示出了在1650℃下,在10分钟的退火期间内所注入的硼和氮的扩散情况。图8中,硼在室温下,以180keV的能量和4×1015cm-2的剂量注入。分别以25和60keV的能量和1.5×1014cm-2和2.5×1014cm-2的剂量进行两次氮注入。如图8所示,在1650℃下的10分钟退火期间,只有很少氮发生扩散。然而,该退火期间大量硼扩散。然而,应注意,尽管硼扩散较深,远离浅氮注入,但硼不会通过浅氮注入扩散到碳化硅衬底的表面。

因此,可利用自对准的源和p-基区及均匀的p-沟道,制造高性能碳化硅功率器件。可以在衬底的整个表面上横向形成反型层。对于低阈值电压和较高激活的注入n+源来说,可以实现p-基区的逆向分布。由于不必用铝作p-基区,所以可以实现较高质量和/或较薄的栅氧化区,因而可以进一步降低电阈值。

另外,p-基区处不必存在强电场,所以可以避免与散射或场强有关的问题。在n+氧化物中不必存在尖角,所以可以减少导通态工作时热电子的注入。由于扩散沟道可以提供没有反应离子腐蚀损伤的碳化硅/二氧化硅界面,从而提供低界面俘获密度和固定电荷,所以可以使沟道具有高迁移率。

最后,通过省去了至少一个掩模,并提供自对准,可以降低严密对准容差的要求,所以可以简化制造。因此,可以提供制造碳化硅功率器件的改进方法。

在附图和说明书中,公开了本发明的典型优选实施例,尽管使用了特定术语,但它们仅用于一般意义上的描述,并非为了限制,本发明的范围记载于以下的权利要求书中。

Claims (44)

1.一种制造碳化硅功率器件的方法,包括以下步骤:

掩蔽碳化硅衬底的表面,在表面限定开口;

以形成埋藏式深p型注入的注入能量和剂量,通过所说开口向碳化硅衬底注入p型掺杂剂;

以相对于埋藏式深p型注入形成浅n型注入的注入能量和剂量,通过所说开口向碳化硅衬底注入n型掺杂剂;

在不使埋藏式深p型注入通过浅n型注入纵向扩散到碳化硅衬底的表面的条件下,以足以使埋藏式深p型注入横向扩散到包围浅n型注入的碳化硅衬底的表面的温度和时间,进行退火。

2、根据权利要求1的方法,其中首先注入p型掺杂剂的步骤包括以形成埋藏式深p型注入的多个注入能量和剂量,通过所说开口,在碳化硅衬底中注入p型掺杂剂的步骤;及

其中然后注入n型掺杂剂的步骤包括然后以相对于埋藏式深p型注入形成浅n型注入的多个注入能量和剂量,通过所说开口,在碳化硅衬底中注入n型掺杂剂的步骤。

3、根据权利要求2的方法,其中首先注入p型掺杂剂的步骤包括以形成埋藏式深p型注入的多个注入能量和剂量,通过所说开口,在碳化硅衬底中注入硼的步骤;及

其中然后注入n型掺杂剂的步骤包括然后以相对于埋藏式深p型注入形成浅n型注入的多个注入能量和剂量,通过所说开口,在碳化硅衬底中注入氮的步骤。

4、根据权利要求1的方法,其中首先注入p型掺杂剂的步骤包括注入硼的步骤,其中然后注入n型掺杂剂的步骤包括注入氮的步骤。

5、根据权利要求1的方法,其中首先注入p型掺杂剂的步骤包括注入铍的步骤,其中然后注入n型掺杂剂的步骤包括注入氮的步骤。

6、根据权利要求1的方法,还包括在碳化硅衬底的表面注入铝阱,电接触横向扩散的埋藏式深p型注入的步骤。

7、一种制造碳化硅功率器件的方法,包括以下步骤:

掩蔽碳化硅衬底的表面,在表面限定开口;

首先,以形成浅n型注入的注入能量和剂量,通过所说开口向碳化硅衬底注入n型掺杂剂;

电激活所说n型掺杂剂;

然后以相对于浅n型注入形成埋藏式深p型注入的注入能量和剂量,通过所说开口向碳化硅衬底注入p型掺杂剂;

在不使埋藏式深p型通过浅n型注入纵向扩散到碳化硅衬底的表面的条件下,以足以使埋藏式深p型注入横向扩散到包围浅n型注入的碳化硅衬底的表面的温度和时间,进行退火。

8、根据权利要求7的方法,其中首先注入n型掺杂剂的步骤包括以形成浅n型注入的多个注入能量和剂量,通过所说开口,在碳化硅衬底中注入n型掺杂剂的步骤;及

其中然后注入p型掺杂剂的步骤包括然后以相对于浅n型注入形成埋藏式深p型注入的多个注入能量和剂量,通过所说开口,在碳化硅衬底中注入p型掺杂剂的步骤。

9、根据权利要求8的方法,其中首先注入n型掺杂剂的步骤包括以形成浅n型注入的多个注入能量和剂量,通过所说开口,在碳化硅衬底中注入氮的步骤;及

其中然后注入p型掺杂剂的步骤包括然后以相对于浅n型注入形成埋藏式深p型注入的多个注入能量和剂量,通过所说开口,在碳化硅衬底中注入硼的步骤。

10、根据权利要求7的方法,其中首先注入n型掺杂剂的步骤包括注入氮的步骤,其中然后注入p型掺杂剂的步骤包括注入硼的步骤。

11、根据权利要求7的方法,其中首先注入n型掺杂剂的步骤包括注入氮的步骤,其中然后注入p型掺杂剂的步骤包括注入铍的步骤。

12、根据权利要求7的方法,还包括在碳化硅衬底的表面注入铝阱,电接触横向扩散的埋藏式深p型注入的步骤。

13、一种制造碳化硅横向功率金属氧化物半导体场效应晶体管的方法,包括以下步骤:

在碳化硅衬底的表面上,在漂移区注入铝阱;

掩蔽碳化硅衬底表面上的漂移区,以便在漂移区上限定第一对开口,各个所说开口位于相应铝阱的相对两侧上;

然后以形成深p型注入的注入能量和剂量,通过第一对开口向碳化硅衬底注入p型掺杂剂;

以相对于深p型注入形成浅n型注入的注入能量和剂量,通过第一对开口向碳化硅衬底注入n型掺杂剂;

在碳化硅衬底的表面上掩蔽漂移区,从而在漂移区上限定第二对开口,各开口远离各相应浅n型注入并与铝阱相对;

通过第二对开口向碳化硅衬底注入n型掺杂剂,以限定一对漏区;

在不使各深p型注入通过各相应浅n型注入纵向扩散到碳化硅衬底的表面的条件下,以足以使各深p型注入横向扩散到包围各浅n型注入的碳化硅衬底的表面的温度和时间,进行退火,从而在碳化硅衬底的表面上,在横向扩散的p型注入中形成一对沟道区,各沟道区位于铝阱的各相应相对侧上;

在碳化硅衬底表面,在漂移区上形成一对栅绝缘区,各栅绝缘区与该对沟道区的相应一个接触;及

在浅n型注入和两浅n型注入间的铝阱上、在漏区上、在所说绝缘区上,分别形成公共源接触、一对漏接触和一对栅接触。

14、根据权利要求13的方法,其中首先注入p型掺杂剂的步骤包括以形成深p型注入的多个注入能量和剂量,通过第一对开口,在碳化硅衬底表面漂移区中注入p型掺杂剂的步骤;及

其中然后注入n型掺杂剂的步骤包括然后以相对于深p型注入形成浅n型注入的多个注入能量和剂量,通过第一对开口,在碳化硅衬底表面漂移区中注入n型掺杂剂的步骤。

15、根据权利要求14的方法,其中首先注入p型掺杂剂的步骤包括以形成深p型注入的多个注入能量和剂量,通过第一对开口,在碳化硅衬底表面漂移区中注入硼的步骤;及

其中然后注入n型掺杂剂的步骤包括然后以相对于深p型注入形成浅n型注入的多个注入能量和剂量,通过第一对开口,在碳化硅衬底表面漂移区中注入氮的步骤。

16、根据权利要求14的方法,其中首先注入p型掺杂剂的步骤包括以形成深p型注入的多个注入能量和剂量,通过第一对开口,在碳化硅衬底表面漂移区中注入铍的步骤;及

其中然后注入n型掺杂剂的步骤包括然后以相对于深p型注入形成n型注入的多个注入能量和剂量,通过第一对开口,在碳化硅衬底表面漂移区中注入氮的步骤。

17、根据权利要求13的方法,其中首先注入p型掺杂剂的步骤包括注入硼的步骤,其中然后注入n型掺杂剂的步骤包括注入氮的步骤。

18、根据权利要求13的方法,其中首先注入p型掺杂剂的步骤包括注入铍的步骤,其中然后注入n型掺杂剂的步骤包括注入氮的步骤。

19、根据权利要求13的方法,其中注入铝阱的步骤在注入n型掺杂剂的步骤之后,以便铝阱注入在两浅n型注入之间。

20、根据权利要求13的方法,其中在注入n型掺杂剂的步骤之后,进行首先注入p型掺杂剂,然后注入n型掺杂剂的步骤,以便在形成深p型注入和浅n型注入之前,形成一对漏区。

21、根据权利要求13的方法,其中同时进行注入n型掺杂剂和注入n型掺杂剂的步骤,以便同时形成浅n型注入和一对漏区。

22、一种制造碳化硅侧向功率金属氧化物半导体场效应晶体管的方法,包括以下步骤:

在碳化硅衬底表面上,在漂移区中注入铝阱;

掩蔽碳化硅衬底表面上的漂移区,以在漂移区上限定第一对开口,各个开口位于各铝阱的相对两侧上;

首先以形成浅n型注入的注入能量和剂量,通过第一对开口向碳化硅衬底注入n型掺杂剂;

电激活n型掺杂剂;

然后以相对于浅n型注入形成深p型注入的注入能量和剂量,通过第一对开口向碳化硅衬底注入p型掺杂剂;

在碳化硅衬底的表面上掩蔽漂移区,从而在漂移区上限定第二对开口,其中各开口远离各相应浅n型注入并与铝阱相对;

通过第二对开口向碳化硅衬底注入n型掺杂剂,以限定一对漏区;

在不使各深p型注入通过各浅n型注入纵向扩散到碳化硅衬底的表面的条件下,以足以使各深p型注入横向扩散到包围各浅n型注入的碳化硅衬底的表面的温度和时间,进行退火,从而在碳化硅衬底的表面上,在横向扩散的p型注入中形成一对沟道区,其中各沟道区位于铝阱的各相应相对侧上;

在碳化硅衬底表面,在漂移区上形成一对栅绝缘区,各栅绝缘区与各个沟道区接触;及

在浅n型注入和两浅n型注入间的铝阱上、在漏区上、在所说一对绝缘区上,分别形成公共源接触、一对漏接触和一对栅接触。

23、根据权利要求22的方法,其中首先注入n型掺杂剂的步骤包括以形成浅n型注入的多个注入能量和剂量,通过第一对开口,在碳化硅衬底表面漂移区中注入n型掺杂剂的步骤;及

其中然后注入p型掺杂剂的步骤包括然后以相对于浅n型注入形成深p型注入的多个注入能量和剂量,通过第一对开口,在碳化硅衬底表面漂移区中注入p型掺杂剂的步骤。

24、根据权利要求23的方法,其中首先注入n型掺杂剂的步骤包括以形成浅n型注入的多个注入能量和剂量,通过第一对开口,在碳化硅衬底表面漂移区中注入氮的步骤;及

其中然后注入p型掺杂剂的步骤包括然后以相对于浅n型注入形成深p型注入的多个注入能量和剂量,通过第一对开口,在碳化硅衬底表面漂移区中注入硼的步骤。

25、根据权利要求23的方法,其中首先注入n型掺杂剂的步骤包括以形成浅n型注入的多个注入能量和剂量,通过第一对开口,在碳化硅衬底表面漂移区中注入氮的步骤;及

其中然后注入p型掺杂剂的步骤包括然后以相对于浅n型注入形成深p型注入的多个注入能量和剂量,通过第一对开口,在碳化硅衬底表面漂移区中注入铍的步骤。

26、根据权利要求22的方法,其中首先注入n型掺杂剂的步骤包括注入氮的步骤,其中然后注入p型掺杂剂的步骤包括注入硼的步骤。

27、根据权利要求22的方法,其中首先注入n型掺杂剂的步骤包括注入氮的步骤,其中然后注入p型掺杂剂的步骤包括注入铍的步骤。

28、根据权利要求22的方法,其中注入铝阱的步骤在注入n型掺杂剂的步骤之后,以便铝阱注入在两浅n型注入之间。

29、根据权利要求22的方法,其中在注入n型掺杂剂的步骤之后,进行首先注入p型掺杂剂,然后注入n型掺杂剂的步骤,以便在形成深p型注入和浅n型注入之前,形成一对漏区。

30、根据权利要求22的方法,其中同时进行注入n型掺杂剂和注入n型掺杂剂的步骤,以便同时形成浅n型注入和一对漏区。

31、一种制造碳化硅纵向功率金属氧化物半导体场效应晶体管的方法,包括以下步骤:

在碳化硅衬底表面上,在漂移区中注入一对隔开的铝阱;

掩蔽碳化硅衬底表面上的漂移区,以在漂移区上所说一对铝阱之间限定第一对开口;

首先以形成深p型注入的注入能量和剂量,通过第一对开口向碳化硅衬底注入p型掺杂剂;

然后以相对于深p型注入形成浅n型注入的注入能量和剂量,通过第一对开口向碳化硅衬底注入n型掺杂剂;

在不使各深p型注入通过各浅n型注入纵向扩散到碳化硅衬底的表面的条件下,以足以使各深p型注入横向扩散到包围各浅n型注入的碳化硅衬底的表面的温度和时间,进行退火,从而在碳化硅衬底的表面上,在两浅n型注入之间,在横向扩散的p型注入中形成一对沟道区;

在所说一对沟道形成区上和之间延伸的碳化硅衬底表面上,形成一对栅绝缘区;

在相应浅n型注入形成一对源接触、栅接触和漏接触,并分别延伸在与浅n型注入相邻的铝阱上、在所说栅绝缘区上和与漂移区相对的碳化硅衬底的第二表面上。

32、根据权利要求31的方法,其中首先注入p型掺杂剂的步骤包括以形成深p型注入的多个注入能量和剂量,通过第一对开口,在碳化硅衬底表面漂移区中注入p型掺杂剂的步骤;及

其中然后注入n型掺杂剂的步骤包括然后以相对于深p型注入形成浅n型注入的多个注入能量和剂量,通过第一对开口,在碳化硅衬底表面漂移区中注入n型掺杂剂的步骤。

33、根据权利要求32的方法,其中首先注入p型掺杂剂的步骤包括以形成深p型注入的多个注入能量和剂量,通过第一对开口,在碳化硅衬底表面漂移区中注入硼的步骤;及

其中然后注入n型掺杂剂的步骤包括然后以相对于深p型注入形成浅n型注入的多个注入能量和剂量,通过第一对开口,在碳化硅衬底表面漂移区中注入氮的步骤。

34、根据权利要求32的方法,其中首先注入p型掺杂剂的步骤包括以形成深p型注入的多个注入能量和剂量,通过第一对开口,在碳化硅衬底表面漂移区中注入铍的步骤;及

其中然后注入n型掺杂剂的步骤包括然后以相对于深p型注入形成浅n型注入的多个注入能量和剂量,通过第一对开口,在碳化硅衬底表面漂移区中注入氮的步骤。

35、根据权利要求31的方法,其中首先注入p型掺杂剂的步骤包括注入硼的步骤,其中然后注入n型掺杂剂的步骤包括注入氮的步骤。

36、根据权利要求31的方法,其中首先注入p型掺杂剂的步骤包括注入铍的步骤,其中然后注入n型掺杂剂的步骤包括注入氮的步骤。

37、根据权利要求31的方法,其中注入一对隔开的铝阱的步骤在注入n型掺杂剂的步骤之后,以便铝阱注入在浅n型注入之外。

38、一种制造碳化硅纵向功率金属氧化物半导体场效应晶体管的方法,包括以下步骤:

在碳化硅衬底表面上,在漂移区中注入一对隔开的铝阱;

掩蔽碳化硅衬底表面上的漂移区,以在漂移区上所说一对铝阱间限定第一对开口;

首先以形成浅n型注入的注入能量和剂量,通过第一对开口向碳化硅衬底注入n型掺杂剂;

电激活n型掺杂剂;

然后以相对于浅n型注入形成深p型注入的注入能量和剂量,通过第一对开口向碳化硅衬底注入p型掺杂剂;

在不使各深p型注入通过各浅n型注入纵向扩散到碳化硅衬底的表面的条件下,以足以使各深p型注入横向扩散到包围各浅n型注入的碳化硅衬底的表面的温度和时间,进行退火,从而在碳化硅衬底的表面上,在两浅n型注入之间,在横向扩散的p型注入中形成一对沟道区;

在所说一对沟道形成区上和之间延伸的碳化硅衬底表面,形成一对栅绝缘区;

在浅n型注入形成一对源接触、栅接触和漏接触,并分别延伸在与浅n型注入相邻的铝阱上、在所说栅绝缘区上和与漂移区相对的碳化硅衬底的第二表面上。

39、根据权利要求38的方法,其中首先注入n型掺杂剂的步骤包括以形成浅n型注入的多个注入能量和剂量,通过第一对开口,在碳化硅衬底表面漂移区中注入n型掺杂剂的步骤;及

其中然后注入p型掺杂剂的步骤包括然后以相对于浅n型注入形成深p型注入的多个注入能量和剂量,通过第一对开口,在碳化硅衬底表面漂移区中注入p型掺杂剂的步骤。

40、根据权利要求39的方法,其中首先注入n型掺杂剂的步骤包括以形成浅n型注入的多个注入能量和剂量,通过第一对开口,在碳化硅衬底表面漂移区中注入氮的步骤;及

其中然后注入p型掺杂剂的步骤包括然后以相对于浅n型注入形成深p型注入的多个注入能量和剂量,通过第一对开口,在碳化硅衬底表面漂移区中注入硼的步骤。

41、根据权利要求39的方法,其中首先注入n型掺杂剂的步骤包括以形成浅n型注入的多个注入能量和剂量,通过第一对开口,在碳化硅衬底表面漂移区中注入氮的步骤;及

其中然后注入p型掺杂剂的步骤包括然后以相对于浅n型注入形成深p型注入的多个注入能量和剂量,通过第一对开口,在碳化硅衬底表面漂移区中注入氮的步骤。

42、根据权利要求38的方法,其中首先注入n型掺杂剂的步骤包括注入氮的步骤,其中然后注入p型掺杂剂的步骤包括注入硼的步骤。

43、根据权利要求38的方法,其中首先注入n型掺杂剂的步骤包括注入氮的步骤,其中然后注入p型掺杂剂的步骤包括注入铍的步骤。

44、根据权利要求38的方法,其中注入一对隔开的铝阱的步骤在注入n型掺杂剂的步骤之后,以便铝阱注入在浅n型注入之外。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/093,207 US6107142A (en) | 1998-06-08 | 1998-06-08 | Self-aligned methods of fabricating silicon carbide power devices by implantation and lateral diffusion |

| US09/093,207 | 1998-06-08 | ||

| US09/093207 | 1998-06-08 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1304551A CN1304551A (zh) | 2001-07-18 |

| CN1155066C true CN1155066C (zh) | 2004-06-23 |

Family

ID=22237747

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB998071021A Expired - Lifetime CN1155066C (zh) | 1998-06-08 | 1999-06-07 | 利用注入和横向扩散制造碳化硅功率器件的自对准方法 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US6107142A (zh) |

| EP (2) | EP1086491A1 (zh) |

| JP (2) | JP5184724B2 (zh) |

| KR (1) | KR100596061B1 (zh) |

| CN (1) | CN1155066C (zh) |

| AU (1) | AU4550399A (zh) |

| CA (1) | CA2333579C (zh) |

| WO (1) | WO1999065073A1 (zh) |

Families Citing this family (59)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3988262B2 (ja) * | 1998-07-24 | 2007-10-10 | 富士電機デバイステクノロジー株式会社 | 縦型超接合半導体素子およびその製造方法 |

| US6972436B2 (en) * | 1998-08-28 | 2005-12-06 | Cree, Inc. | High voltage, high temperature capacitor and interconnection structures |

| EP1058303A1 (en) * | 1999-05-31 | 2000-12-06 | STMicroelectronics S.r.l. | Fabrication of VDMOS structure with reduced parasitic effects |

| US6504176B2 (en) * | 2000-04-06 | 2003-01-07 | Matshushita Electric Industrial Co., Ltd. | Field effect transistor and method of manufacturing the same |

| US6429041B1 (en) | 2000-07-13 | 2002-08-06 | Cree, Inc. | Methods of fabricating silicon carbide inversion channel devices without the need to utilize P-type implantation |

| US6610366B2 (en) | 2000-10-03 | 2003-08-26 | Cree, Inc. | Method of N2O annealing an oxide layer on a silicon carbide layer |

| US6956238B2 (en) | 2000-10-03 | 2005-10-18 | Cree, Inc. | Silicon carbide power metal-oxide semiconductor field effect transistors having a shorting channel and methods of fabricating silicon carbide metal-oxide semiconductor field effect transistors having a shorting channel |

| US7067176B2 (en) | 2000-10-03 | 2006-06-27 | Cree, Inc. | Method of fabricating an oxide layer on a silicon carbide layer utilizing an anneal in a hydrogen environment |

| US6767843B2 (en) | 2000-10-03 | 2004-07-27 | Cree, Inc. | Method of N2O growth of an oxide layer on a silicon carbide layer |

| KR100393201B1 (ko) * | 2001-04-16 | 2003-07-31 | 페어차일드코리아반도체 주식회사 | 낮은 온 저항과 높은 브레이크다운 전압을 갖는 고전압수평형 디모스 트랜지스터 |

| US6507046B2 (en) | 2001-05-11 | 2003-01-14 | Cree, Inc. | High-resistivity silicon carbide substrate for semiconductor devices with high break down voltage |

| JP3939195B2 (ja) * | 2002-05-13 | 2007-07-04 | ローム株式会社 | 半導体装置の製造方法および半導体装置 |

| US7022378B2 (en) * | 2002-08-30 | 2006-04-04 | Cree, Inc. | Nitrogen passivation of interface states in SiO2/SiC structures |

| US7221010B2 (en) * | 2002-12-20 | 2007-05-22 | Cree, Inc. | Vertical JFET limited silicon carbide power metal-oxide semiconductor field effect transistors |

| US6979863B2 (en) * | 2003-04-24 | 2005-12-27 | Cree, Inc. | Silicon carbide MOSFETs with integrated antiparallel junction barrier Schottky free wheeling diodes and methods of fabricating the same |

| US7074643B2 (en) * | 2003-04-24 | 2006-07-11 | Cree, Inc. | Silicon carbide power devices with self-aligned source and well regions and methods of fabricating same |

| US7118970B2 (en) * | 2004-06-22 | 2006-10-10 | Cree, Inc. | Methods of fabricating silicon carbide devices with hybrid well regions |

| US7414268B2 (en) | 2005-05-18 | 2008-08-19 | Cree, Inc. | High voltage silicon carbide MOS-bipolar devices having bi-directional blocking capabilities |

| US20060261346A1 (en) * | 2005-05-18 | 2006-11-23 | Sei-Hyung Ryu | High voltage silicon carbide devices having bi-directional blocking capabilities and methods of fabricating the same |

| US7391057B2 (en) * | 2005-05-18 | 2008-06-24 | Cree, Inc. | High voltage silicon carbide devices having bi-directional blocking capabilities |

| US7615801B2 (en) * | 2005-05-18 | 2009-11-10 | Cree, Inc. | High voltage silicon carbide devices having bi-directional blocking capabilities |

| US7528040B2 (en) * | 2005-05-24 | 2009-05-05 | Cree, Inc. | Methods of fabricating silicon carbide devices having smooth channels |

| US7727904B2 (en) * | 2005-09-16 | 2010-06-01 | Cree, Inc. | Methods of forming SiC MOSFETs with high inversion layer mobility |

| US7728402B2 (en) | 2006-08-01 | 2010-06-01 | Cree, Inc. | Semiconductor devices including schottky diodes with controlled breakdown |

| US8432012B2 (en) | 2006-08-01 | 2013-04-30 | Cree, Inc. | Semiconductor devices including schottky diodes having overlapping doped regions and methods of fabricating same |

| EP2052414B1 (en) | 2006-08-17 | 2016-03-30 | Cree, Inc. | High power insulated gate bipolar transistors |

| US8835987B2 (en) | 2007-02-27 | 2014-09-16 | Cree, Inc. | Insulated gate bipolar transistors including current suppressing layers |

| JP4442698B2 (ja) * | 2007-07-25 | 2010-03-31 | 三菱電機株式会社 | 炭化珪素半導体装置の製造方法 |

| US8232558B2 (en) | 2008-05-21 | 2012-07-31 | Cree, Inc. | Junction barrier Schottky diodes with current surge capability |

| US8796809B2 (en) | 2008-09-08 | 2014-08-05 | Cree, Inc. | Varactor diode with doped voltage blocking layer |

| US7829402B2 (en) * | 2009-02-10 | 2010-11-09 | General Electric Company | MOSFET devices and methods of making |

| US8288220B2 (en) * | 2009-03-27 | 2012-10-16 | Cree, Inc. | Methods of forming semiconductor devices including epitaxial layers and related structures |

| US8294507B2 (en) | 2009-05-08 | 2012-10-23 | Cree, Inc. | Wide bandgap bipolar turn-off thyristor having non-negative temperature coefficient and related control circuits |

| US8629509B2 (en) | 2009-06-02 | 2014-01-14 | Cree, Inc. | High voltage insulated gate bipolar transistors with minority carrier diverter |

| US8193848B2 (en) | 2009-06-02 | 2012-06-05 | Cree, Inc. | Power switching devices having controllable surge current capabilities |

| US8541787B2 (en) | 2009-07-15 | 2013-09-24 | Cree, Inc. | High breakdown voltage wide band-gap MOS-gated bipolar junction transistors with avalanche capability |

| US8354690B2 (en) | 2009-08-31 | 2013-01-15 | Cree, Inc. | Solid-state pinch off thyristor circuits |

| US9117739B2 (en) | 2010-03-08 | 2015-08-25 | Cree, Inc. | Semiconductor devices with heterojunction barrier regions and methods of fabricating same |

| US8415671B2 (en) | 2010-04-16 | 2013-04-09 | Cree, Inc. | Wide band-gap MOSFETs having a heterojunction under gate trenches thereof and related methods of forming such devices |

| DE102011002468A1 (de) | 2011-01-05 | 2012-07-05 | Robert Bosch Gmbh | Verfahren zur Herstellung einer Siliziumkarbid-Halbleiterstruktur sowie eine verfahrensgemäß hergestellte Halbleiterstruktur |

| US9142662B2 (en) | 2011-05-06 | 2015-09-22 | Cree, Inc. | Field effect transistor devices with low source resistance |

| US9673283B2 (en) | 2011-05-06 | 2017-06-06 | Cree, Inc. | Power module for supporting high current densities |

| US9029945B2 (en) | 2011-05-06 | 2015-05-12 | Cree, Inc. | Field effect transistor devices with low source resistance |

| US9984894B2 (en) | 2011-08-03 | 2018-05-29 | Cree, Inc. | Forming SiC MOSFETs with high channel mobility by treating the oxide interface with cesium ions |

| US8664665B2 (en) | 2011-09-11 | 2014-03-04 | Cree, Inc. | Schottky diode employing recesses for elements of junction barrier array |

| US9373617B2 (en) | 2011-09-11 | 2016-06-21 | Cree, Inc. | High current, low switching loss SiC power module |

| US8618582B2 (en) | 2011-09-11 | 2013-12-31 | Cree, Inc. | Edge termination structure employing recesses for edge termination elements |

| US9640617B2 (en) | 2011-09-11 | 2017-05-02 | Cree, Inc. | High performance power module |

| US8680587B2 (en) | 2011-09-11 | 2014-03-25 | Cree, Inc. | Schottky diode |

| US8941188B2 (en) * | 2012-03-26 | 2015-01-27 | Infineon Technologies Austria Ag | Semiconductor arrangement with a superjunction transistor and a further device integrated in a common semiconductor body |

| US9018048B2 (en) * | 2012-09-27 | 2015-04-28 | Stmicroelectronics S.R.L. | Process for manufactuirng super-barrier rectifiers |

| RU2528554C1 (ru) * | 2013-04-25 | 2014-09-20 | федеральное государственное автономное образовательное учреждение высшего профессионального образования "Национальный исследовательский ядерный университет МИФИ" (НИЯУ МИФИ) | Способ формирования высоковольтного карбидокремниевого диода на основе ионно-легированных p-n-структур |

| US9768259B2 (en) * | 2013-07-26 | 2017-09-19 | Cree, Inc. | Controlled ion implantation into silicon carbide using channeling and devices fabricated using controlled ion implantation into silicon carbide using channeling |

| JP6206012B2 (ja) * | 2013-09-06 | 2017-10-04 | 住友電気工業株式会社 | 炭化珪素半導体装置 |

| US9673315B2 (en) | 2015-03-24 | 2017-06-06 | Kabushiki Kaisha Toshiba | Semiconductor device, inverter circuit, driving device, vehicle, and elevator |

| JP6988216B2 (ja) | 2017-07-12 | 2022-01-05 | 富士電機株式会社 | 半導体装置の製造方法 |

| JP7058337B2 (ja) * | 2018-02-28 | 2022-04-21 | ヒタチ・エナジー・スウィツァーランド・アクチェンゲゼルシャフト | Al/Be共注入により炭化ケイ素をp型ドーピングする方法 |

| JP6862381B2 (ja) | 2018-03-02 | 2021-04-21 | 株式会社東芝 | 半導体装置 |

| US10636660B2 (en) | 2018-09-28 | 2020-04-28 | General Electric Company | Super-junction semiconductor device fabrication |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3629011A (en) * | 1967-09-11 | 1971-12-21 | Matsushita Electric Ind Co Ltd | Method for diffusing an impurity substance into silicon carbide |

| US5242841A (en) * | 1992-03-25 | 1993-09-07 | Texas Instruments Incorporated | Method of making LDMOS transistor with self-aligned source/backgate and photo-aligned gate |

| JP3146694B2 (ja) * | 1992-11-12 | 2001-03-19 | 富士電機株式会社 | 炭化けい素mosfetおよび炭化けい素mosfetの製造方法 |

| US5444002A (en) * | 1993-12-22 | 1995-08-22 | United Microelectronics Corp. | Method of fabricating a short-channel DMOS transistor with removable sidewall spacers |

| US5399883A (en) * | 1994-05-04 | 1995-03-21 | North Carolina State University At Raleigh | High voltage silicon carbide MESFETs and methods of fabricating same |

| TW286435B (zh) * | 1994-07-27 | 1996-09-21 | Siemens Ag | |

| US5510281A (en) * | 1995-03-20 | 1996-04-23 | General Electric Company | Method of fabricating a self-aligned DMOS transistor device using SiC and spacers |

| SE9501310D0 (sv) * | 1995-04-10 | 1995-04-10 | Abb Research Ltd | A method for introduction of an impurity dopant in SiC, a semiconductor device formed by the mehtod and a use of a highly doped amorphous layer as a source for dopant diffusion into SiC |

| US5849620A (en) * | 1995-10-18 | 1998-12-15 | Abb Research Ltd. | Method for producing a semiconductor device comprising an implantation step |

| SE9601174D0 (sv) * | 1996-03-27 | 1996-03-27 | Abb Research Ltd | A method for producing a semiconductor device having a semiconductor layer of SiC and such a device |

| JP4629809B2 (ja) * | 1996-03-27 | 2011-02-09 | クリー,インコーポレイテッド | SiCの半導体層を有する半導体素子を製造する方法 |

| SE9602745D0 (sv) * | 1996-07-11 | 1996-07-11 | Abb Research Ltd | A method for producing a channel region layer in a SiC-layer for a voltage controlled semiconductor device |

| US5837572A (en) * | 1997-01-10 | 1998-11-17 | Advanced Micro Devices, Inc. | CMOS integrated circuit formed by using removable spacers to produce asymmetrical NMOS junctions before asymmetrical PMOS junctions for optimizing thermal diffusivity of dopants implanted therein |

| US5877041A (en) * | 1997-06-30 | 1999-03-02 | Harris Corporation | Self-aligned power field effect transistor in silicon carbide |

-

1998

- 1998-06-08 US US09/093,207 patent/US6107142A/en not_active Expired - Lifetime

-

1999

- 1999-06-07 EP EP99928439A patent/EP1086491A1/en not_active Withdrawn

- 1999-06-07 WO PCT/US1999/012714 patent/WO1999065073A1/en active IP Right Grant

- 1999-06-07 KR KR1020007013620A patent/KR100596061B1/ko not_active IP Right Cessation

- 1999-06-07 CN CNB998071021A patent/CN1155066C/zh not_active Expired - Lifetime

- 1999-06-07 AU AU45503/99A patent/AU4550399A/en not_active Abandoned

- 1999-06-07 JP JP2000553992A patent/JP5184724B2/ja not_active Expired - Lifetime

- 1999-06-07 EP EP06115562A patent/EP1701377A3/en not_active Ceased

- 1999-06-07 CA CA002333579A patent/CA2333579C/en not_active Expired - Lifetime

-

2011

- 2011-01-14 JP JP2011006255A patent/JP5295274B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| KR20010052492A (ko) | 2001-06-25 |

| EP1086491A1 (en) | 2001-03-28 |

| CA2333579C (en) | 2009-09-08 |

| CA2333579A1 (en) | 1999-12-16 |

| US6107142A (en) | 2000-08-22 |

| JP2002518828A (ja) | 2002-06-25 |

| CN1304551A (zh) | 2001-07-18 |

| EP1701377A2 (en) | 2006-09-13 |

| JP5184724B2 (ja) | 2013-04-17 |

| WO1999065073A1 (en) | 1999-12-16 |

| JP5295274B2 (ja) | 2013-09-18 |

| AU4550399A (en) | 1999-12-30 |

| JP2011097093A (ja) | 2011-05-12 |

| EP1701377A3 (en) | 2008-08-06 |

| KR100596061B1 (ko) | 2006-07-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1155066C (zh) | 利用注入和横向扩散制造碳化硅功率器件的自对准方法 | |

| CN1132225C (zh) | 通过受控退火制造碳化硅功率器件的方法 | |

| CN1079996C (zh) | 高压金属氧化物硅场效应晶体管结构 | |

| CN100555663C (zh) | 碳化硅器件及其制造方法 | |

| EP2052414B1 (en) | High power insulated gate bipolar transistors | |

| CN1505170A (zh) | SiC-MISFET及其制造方法 | |

| CN1271720C (zh) | 耐高压的绝缘体上的硅型半导体器件 | |

| CN1717811A (zh) | 源极区下面具有隐埋p型层的晶体管及其制造方法 | |

| CN1992337A (zh) | 具有碳化硅钝化层的碳化硅双极结型晶体管及其制造方法 | |

| CN1295795C (zh) | 电力半导体器件 | |

| CN1557022A (zh) | 半导体装置及其制造方法 | |

| US5893736A (en) | Methods of forming insulated gate semiconductor devices having spaced epitaxial JFET regions therein | |

| CN112655096A (zh) | 超结碳化硅半导体装置及超结碳化硅半导体装置的制造方法 | |

| CN1838435A (zh) | 结型半导体装置及其制造方法 | |

| CN1154570A (zh) | 用改进的小型区抑制何短沟道的mos晶体管及其制造方法 | |

| Vathulya et al. | A novel 6H-SiC power DMOSFET with implanted p-well spacer | |

| CN1638144A (zh) | 半导体器件及其制造方法 | |

| CN1729577A (zh) | 碳化硅功率mos场效应晶体管及制造方法 | |

| CN1494162A (zh) | 半导体衬底及其制造方法和半导体器件及其制造方法 | |

| CN1202001A (zh) | 具有金属-绝缘膜-半导体三层结构的晶体管的制造方法 | |

| CN1823423A (zh) | 半导体装置及其制造方法 | |

| CN1485927A (zh) | 半导体衬底及其制造方法,以及半导体器件及其制造方法 | |

| Ng et al. | A novel planar power MOSFET with laterally uniform body and ion-implanted JFET region | |

| CN117317026B (zh) | 一种半导体器件及其制造方法 | |

| WO2023095363A1 (ja) | 半導体装置とその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CX01 | Expiry of patent term |

Granted publication date: 20040623 |

|

| CX01 | Expiry of patent term |