CN1309849A - 采用动态半双工保持环路的公平 - Google Patents

采用动态半双工保持环路的公平 Download PDFInfo

- Publication number

- CN1309849A CN1309849A CN99803266A CN99803266A CN1309849A CN 1309849 A CN1309849 A CN 1309849A CN 99803266 A CN99803266 A CN 99803266A CN 99803266 A CN99803266 A CN 99803266A CN 1309849 A CN1309849 A CN 1309849A

- Authority

- CN

- China

- Prior art keywords

- loop

- port

- data

- channel

- communication channel

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/54—Store-and-forward switching systems

- H04L12/56—Packet switching systems

- H04L12/5601—Transfer mode dependent, e.g. ATM

- H04L12/5602—Bandwidth control in ATM Networks, e.g. leaky bucket

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/28—Data switching networks characterised by path configuration, e.g. LAN [Local Area Networks] or WAN [Wide Area Networks]

- H04L12/42—Loop networks

- H04L12/427—Loop networks with decentralised control

- H04L12/433—Loop networks with decentralised control with asynchronous transmission, e.g. token ring, register insertion

Abstract

一种保持环路公平性的方法和装置。某些实施例包括动态半双工特性。一个方面包括一通信信道系统和保持环路公平性的方法,它包括具有一个或多个端口第一信道节点,每一端口支持光纤信道仲裁环路串行通信信道,并与之相连。端口中的一个将对端口相连的信道控制进行仲裁,其中,对信道环路的控制在赢得了仲裁以后,公平保持装置至少部分根据第一端口和通信信道之间是否出现了预定的使用量而释放对通信信道的控制。在某些实施例中,预定的使用量包括第一预定量数据的转发。在某些实施例中,如果小于第二预定量的剩余数据是要转发的,则禁止释放对信道的控制。

Description

相关申请

本申请根据美国专利法第35条第119(e)条款,请求保护1998年2月24日申请的临时专利申请60/075,797的利益。

发明领域

本发明涉及大容量存储装置领域。本发明尤其涉及采用数据传输动态半双工模式保持环路公平的改进的光纤信道仲裁一环路(“FC-AL”)装置和方法。

发明背景

任何一个计算机系统的一个主要元件都是用于存储数据的装置。计算机系统有许多可以存储数据的装置。计算机系统中存储大量数据的一个共同点是将数据存储在磁盘驱动器上。磁盘驱动器的最基本部件是旋转的磁盘、使传感器移动到磁盘上不同区域的致动器以及用来在磁盘上写入和读出数据的电路。磁盘驱动器还包括对数据进行编码从而可以在磁盘表面上成功检索出和写入数据的电路。微处理器除了将数据送回请求的计算机以及从请求的计算机取得数据而存储到磁盘上以外,还控制磁盘驱动器的大多数操作。

在磁盘驱动器和计算机系统其余部分之间转发数据的接口通常是一个总线或信道,如小型计算机系统接口(“SCSI”),或光纤信道。这些接口的某些方面通常是被标准化的,以便可以更换来自不同制造商的器件,并且所有的器件都可以连接到一个公共的接口上。这样的标准通常是由某种标准委员会或组织如美国国家标准协会(“ANSI”)规定的。

在各种存储装置和各种计算机之间交换数据的一种标准化接口是光纤信道。在某些实施例中,光纤信道标准包括仲裁环路(将在下面描述)。在某些实施例中,光纤信道标准支持类似于SCSI的协议,用来控制数据转发。

光纤信道与小型计算机标准接口(“SCSI”)设计相比,具有明显的优点。与用于传统SCSI设计的每秒二和二十兆字节相比,光纤信道具有明显更高的带宽,目前可以高达约每秒106兆字节。与典型的SCSI环境中最大7或15个装置相比,光纤信道提供更大的连接性,可以连接高达126个装置(包括主机)。光纤信道可以与单个的连接器相连,并且不需要开关(switch)。与用于SCSI环境下最大总长度为25米相比,采用同轴电导线的光纤信道可以在装置间达30米的距离下工作,并且采用光纤用于整个信道时可以达10公里。

在SCSI环境下,数据传输中的差错是通过奇偶性来检测的。而在光纤信道中,差错是通过运行非奇偶性和循环冗余码检验(“CRC检验”)信息来识别的。参见本发明人Westby的标题为“采用以多端口设计的CRC发生器的CRC检验(CRCChecking Using a CRC Generator in a Multi-port Design))”的美国专利5,802,080和标题为“16B/20B编码器(16B/20B Encoder)”的美国专利5,663,724可以得到更多的信息,这两个专利均已转让给本发明的受让人:SeagateTechnology,Inc.。

光纤信道仲裁环路(“FC-AL”)是一个工业标准系统,它采用指向字节的DC平衡(0,4)运行长度有限8B/10B隔离块传输码方案。FC-AL在106.25MHz的时钟频率下工作。一种形式的8B/10B编码器/译码器见Franaszek等人标题为“指向字节的DC平衡(0,4)8B/10B隔离块传输码”、授权日为1984年12月4日的美国专利4,486,739中的描述。

光纤信道仲裁环路(“FC-AL”)允许多个装置连接在一起,每一个装置成为是一个“节点”。一个节点可以是计算机系统的任何一种装置(计算机、工作站、打印机、磁盘驱动器、扫描器等),计算机系统有一个接口,使得该接口可以与一种光纤信道“拓扑”结构相连(其定义见下文)。每一个节点具有至少一个端口,称为一个NL端口(“节点环路端口”),用以提供对其他节点的访问。将两个或更多个端口连接在一起的元件统称为“拓扑结构”或“环路”。每一节点与拓扑结构或环路中的所有其他的节点进行通信。

尽管数据可以在光纤信道上传送到其他节点(外界)的端口,但端口是光纤信道节点的连接。典型的光纤信道驱动器有两个在驱动器节点中分组(packaged)的端口。每一端口包括一对“光纤”一一根光纤携带进入端口的信息,而另一根光纤携带出自该端口的信息。每一“光纤”是一个串行数据连接,并且在一种实施例中,每一光纤实际上是一根同轴线(例如用在节点相互靠近时的同轴铜导线);在其他的实施例中,光纤是作为一种用于至少某些路径的光纤实现其功能的(例如,用于节点分开明显距离的时候,例如不同房间特别是不同建筑物中的节点)。与每一端口相连的光纤对(一条光纤携带进入端口的数据,而另一光纤携带出自该端口的数据)称为“链路”,并且是每一拓扑结构的一部分。链路携带有节点间“帧”中分组的信息或信号。每一条链路可以处理许多种类型的帧(例如,初始化、数据和控制帧)。

由于每一条光纤所携带的数据仅沿一个方向,所以,节点是一条沿环路相互连接起来的,其中,节点必须在它们有数据要传送时仲裁环路的控制。“仲裁”是协调节点确定哪一个节点具有环路控制的过程。光纤信道仲裁环路连接无中枢或无交换机的环路中的多个节点。节点端口采用仲裁操作,建立起点对点数据转发电路。FC-AL是一个分布式拓扑结构,该结构中,每一端口包括至少所必须的最少的建立起电路的功能。仲裁环路拓扑结构用来连接两个与126个节点端口之间的任意数量的节点。

在某些实施例中,每一节点包括两个端口(每一端口与一个独立的环路相连),具有冗余性,从而当一个环路出故障时,另一个环路可以完成环路的责任。双端口可使得两个主机(例如两个主计算机)可以共享一个驱动器。

公平背景

“公平(fairness)”一词在本发明中是一种操作方式,其中,共享资源如光纤信道环路是在及时基础上对多个用户中的每一个用户如多个磁盘驱动器100中的每一个而形成的;即,没有不适当的延迟,并且对于与数据量成正比的时间来说,每一磁盘驱动器100需要进行转发。“操作不公平”是这样一种操作方式,其中,每一用户,如一个磁盘驱动器将控制共享资源(如光纤信道环路)太频繁或者时间太长,从而剥夺了其他磁盘驱动器使用环路的需求。

“公平”使得每一端口能够访问环路(根据优先顺序),并发送它想要的尽可能多的信息(没有时间限制)。随后,它必须在其他端口进行访问之前,等待对增益(gain)的仲裁。

环路协议使得每一个L_Port(端口)(也称为环路端口;L_Port可以是一个普通的环路端口“NL_Port”,也可以是一个通常用来将两个环路相互连接起来的结构(fabric)环路端口“FL_Port”)能够连续进行仲裁,以访问环路。优先顺序是根据仲裁环路物理地址(AL_PA)分配给每一个参加的L端口的。至于其他优先顺序化的协议,这会产生较低优先顺序的L_Port不能访问环路的情况。访问公平算规建立起一个访问窗口,在这个窗口中,所有的L_Port具有仲裁和赢得访问环路的机会。当所有的L_Port具有了一次访问环路的机会的时候,就启动了一个新的访问窗口。一个L_Poert会再次进行仲裁,并最终赢得对新访问窗口中环路的访问。并不是要求每一个L_Port都访问任何一个访问窗口中的环路的。

当采用访问公平算规的一个L_Port进行了仲裁,并赢得访问环路的时候,该L_Port将不会再次进行仲裁,直到该L_Port已经发出了至少一次“空闲”。在第一个L_Port赢得了仲裁与发出一个“空闲”之间的时间是一个访问窗口。一特定的仲裁原始信号(即ARB(F0))用来防止对访问窗口的较早的复位。复位公平算规的细节见“光纤信道FC-AL技术规范”(ANSI标准:Fibre Channel FC-ALX3T11/Project 960D/Rev.4.5和Fibre Channel FC-AL2 X3T11/Project 1133D/Rev.6.3)。

一旦L_Port赢得了仲裁的时候,访问公开算规是不限制其控制环路的时间的,就象ANSI X3.230,FC-PH不限制等级1连接的时间一样。然而,如果访问被拒绝的时间比E_D_TOV的长,那么访问窗口就被复位,并且L_Port可以开始进行仲裁。

尽管所有的L_Port都将执行公平算规,但不管是FL_Port还是NL_Port都不会被要求在所有的时间里都采用公平算规。例如,如果一个L_Port要求比其他的L_Port更多的环路访问,那么L_Port就选择是不公平的。

为了向所有的L_Port提供相等的环路访问,建议每一个L_Port采用访问公平算规。当一个L_Port采用访问公平算规的时候,它被称作是一个“公平”L_Port。

当一个公平的L_Port进行了仲裁,访问了环路,并且没有检测到另一个L_Port也在进行仲裁,那么该L_Port将无限期地保持已有电路开路,或者使该电路闭合,并保留打开环路上另一个L_Port的环路所有权(即不进行再仲裁)。

当一个公平的L_Port已经访问了环路并检测到另一个L_Port在进行仲裁时,L_Port会在尽可能早的时间里使环路闭合。L_Port将在打开不同L_Port之前闭合该环路,并在下一个访问窗口中再次进行仲裁。

某些环路的结构会要求某些L_Port比每一访问窗口一次具有更多次对环路的访问。这些L_Port的例子包括(但不局限于限于)子系统控制器或文件服务器。

一个L_Port可以被初始化(或者是临时选择),而不采用访问公平算规。当L_Port不采用公平算规时,它被称作是一个“不公平的”L_Port。对是否参与访问公平性的判断是根据是否需要进行实施的。

当一个不公平的L_Port已经进行了仲裁,以及赢得了对环路的访问并且没有检测到另一个L_Port在进行仲裁时,则L_Port将无限期地使已有电路保持开路,或者使电路闭合,并保留在环路上打开另一个L_Port的环路拥有权(即,不进行再仲裁)。

当一个不公平的L_Port控制环路并检测到另一个L_Port在进行仲裁时,不公平的L_Port会在尽可能早的时间里使环路闭合。该不公平的L_Port会保留该环路的所有权(即不进行再仲裁),并打开环路上的另一个L_Port。

一个参与的FL_Port根据其AL_PA总是在环路上具有最高优先权的L_Port。一个AL_Port是不采用访问公平算规的,这是因为其大多数业务是与结构(Fabric)的其余部分有关的。

当有关FL_Port控制环路并检测到另一个NL_Port在进行仲裁时,FL_Port可以在尽可能早的时间里使环路闭合。由于FL_Port具有最高的优先权并且是不采用公平算规的,所以它将永远赢得仲裁。所以,如果需要与另一个NL_Port进行通信,则FL_Port会保留其对环路的访问(即不进行仲裁),并打开环路上的另一个NL_Port。

所以,需要一种保持环路公平的安排,特别是在包括动态半双工特征的光纤信道实施例中。

发明概述

下面描述用来保持环路公平的方法和装置。某些动态实施例包括动态半双工性能。本发明的一个方面包括一个保持环路公平的通信信道系统,它包括具有一个或多个端口的第一信道节点,每一端口支持一个光纤信道仲裁的环路串行通信信道,并与该信道相连。其中的一个端口将对该端口相连的信道的控制进行仲裁,其中,信道环路的控制在赢得了仲裁以后,公平保持装置会至少部分根据第一端口和通信信道之间是否已经出现预定用量,控制要释放的通信信道。

本发明的另一个方面是提供一种通信方法,它包括控制光纤信道仲裁环路串联通信信道的环路控制;以及至少部分根据第一端口和通信信道之间是否出现的预定用量的通信信道的释放控制。

在上述系统和方法的某些实施例中,预定用量包括第一预定数据量的转发。在某些这样的实施例中,如果剩余要传送的第二预定数据量较少,则禁止该信道的释放。

附图简述

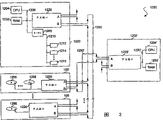

图1是具有光纤信道节点接口的磁盘驱动器100的方框图。

图2是具有本发明的信息处理系统1200的方框图。

图3是光纤信道节点接口芯片(chip)110的方框图。

图4是光纤信道环路端口电路20的方框图。

图5是光纤信道环路控制电路40的方框图。

详细描述

在较佳实施例的下述详细描述中,标号是附图的一部分,附图是用来描述可以实施本发明的特定实施例的。应当理解的是,也可以采用其他的实施例,在不偏离本发明的范围的情况下,还可以有各种结构变化。

本申请中所描述的本发明适用于各种类型的磁盘驱动器,包括硬盘驱动器、ZIP(邮政区分号)驱动器、软盘驱动器、光盘驱动器、CDROM(“紧致盘只读存储器”)驱动器,和其他类型的驱动器、驱动器系统(“廉价/独立的磁盘驱动器冗余阵列”,或RAID、配置)或其他的驱动器,这里,数据是在驱动器和其他装置或信息处理系统之间传递的。在某些实施例中,本发明是用于非磁盘装置的节点接口的,如枢纽(hub)或交换局(如用来将多个光纤信道环路互相连接)、工作站、打印机和连接在光纤信道仲裁环路上的其他装置或信息处理系统。

图1绘出的是具有光纤信道节点接口的磁盘驱动装置100的方框图。更多的信息可以在标题为“环路初始化和响应的方法和专用帧缓冲器(Method andDedicated Frame Buffer for Loop Initialization and Responses)”的美国专利申请09/193,387中找到。

参考图2以及图1,光纤信道环路接口电路1220(也称为节点接口1220)包括环路初始化和响应的专用发射帧缓冲器73。在一种实施例中,每一节点接口1220包括两个端口116(称为端口A和端口B)。(“环路初始化”是通过发送一个或多个由专用的非数据帧组成的序列(并监视对这些帧的响应)来完成的,用以对光纤信道环路初始化。“响应”是响应于命令或来自其他节点的查询而发送的非数据帧。)光纤信道仲裁环路的通信信道1250(也称为环路1250或光纤信道环路1250)可以用来在磁盘存储装置100和计算机(或其他的信息处理系统)1202或其他的信息处理装置之间传送数据。在一种实施例中,光纤信道环路1250是串行通信信道;其其他的实施例中,两条或多条并行线路(或“光纤”)用来构成光纤信道环路1250。具有这样的专用发射帧缓冲器73使得双端口节点1220的一个端口116能够发送初始化帧或应答帧,而另一个端口发送或接收数据帧。端口116是串行线,一条线路117用于入站数据,而另一条线路118用于出站数据,两条线路117和118连接到通信信道环路1250,并形成通信信道环路1250的一部分。专用接收缓冲器(53,53’和55)用于双端口节点的每一个端口116。(注意,具有用带撇的标号(如53’)的每一个方框具有与不带撇的相应方框(如53)相同的功能但用于不同的环路端口或通信信道)。与某一帧一起从光纤信道1250接收的循环冗余码信息存储在一个或多个帧缓冲器(53,53’或55)中的一个缓冲器内,并且随后结果检查,以确保数据在帧缓冲器(53,53’或55)中时的完整性。只要可编程的数据量可以用于传输,就保持对环路1250的控制(即,环路连接保持打开),以便减少对环路1250的控制仲裁所需的总的时间量。

在某些实施例中,磁盘驱动器100包括一个磁性存储头磁盘组件(“HDA”),它具有一个或多个磁盘母板(disc platter)134、每一磁盘母板的一个或多个磁读/写传感器150,和一个臂致动器组件126。传感器(或“磁头”)与HDA接口113之间的信号往返于磁盘母板134之间转发数据。所以,某些实施例的“磁盘驱动器”(如图1中的磁盘驱动器1256)包括HDA 114和HDA接口113(如传统的SCSI驱动器),并且一个或多个这样的传统磁盘驱动器1256与一个外部节点接口1220相连,以便如图1所示与一个环路或光纤信道拓扑结构相连。在其他的实施例中,“磁盘驱动器”由图2中的磁盘驱动器100典型化,并且包括与整个磁盘驱动器100中的磁盘驱动器1256组装在一起。在一个实施例中,数据又轮流往返于片外缓冲器111之间传送。本发明提供了一种专用的单片缓冲器119,在所示的实施例中,它包括用于每一端口(即缓冲器53和53’)的接收非数据帧缓冲器53(也称为“入站非数据缓冲器53”)、在一个实施例中可以同时用于两个端口的发射帧缓冲器73(在其他的实施例中一次一个缓冲器仅用于一个端口),以及带有CRC检验器596的共享数据帧缓冲器55。

在一个实施例中,环路端口收发器块115(即115和115’),它包括端口收发器,而该端口收发器使通过端口A和端口B到与之相连的光纤信道环路1250(见图2)的数据转发串行化和去串行化。在某些实施例中,收发器115是用作外收发器的;而在其他的实施例中,这些收发器在片地位于方框110中。在某些实施例中,右侧接口(即相对于图1中的收发器115或115’的右侧)是10位宽的并行输入-输出信号;在其他的实施例中,它们是20位宽。方框110、111、112、端口A收发器115和端口B收发器115’形成光纤信道节点接口1220。在某些实施例中,端口收发器115和115’是在单个的芯片110内的。在其他的实施例中,收发器115和115’,包括它们的串行器/去串行器是在与芯片110分开的电路上实现的。

在其他的实施例中收发器115仅仅是串行环路1250和芯片110之间的接口,其中,用于10位宽或20位宽的数据的串行和去串行是在片发生的。

图2是计算机系统1200的示意图。本发明最适用于用在计算机系统1200内。计算机系统1200还可以被称作是电子系统或信息处理系统,并且包括一个中央处理单元(“CPU”)、存储器和系统总线。计算机系统1200包括一个具有中央处理单元1204的CPU信息处理单元1202、随机存取存储器(“RAM”)1232,和用来在通信上将中央处理单元1204与随机存取存储器1232耦合起来的系统总线1230。CPU信息处理系统1202包括光纤信道节点接口1220。一个或多个磁盘存储信息处理系统100到100’中的每一个都包括一个或多个磁盘驱动装置1256和光纤信道节点接口1220。

在某些实施例中,多个磁盘驱动器1256与一个单节点接口1220相连,例如在RAID(廉价/独立磁盘驱动器冗余阵列)结构中,装置100’是一个磁盘驱动器的RAID阵列。CPU信息处理系统1202还可以包括一个输入/输出接口电路1209,该电路驱动内部输入/输出总线1210和几个外围装置,如1212、1214和1216,这些装置可以与输入/输出总线1210相连。外围装置可以包括硬盘驱动器、磁-光驱动器、软盘驱动器、监视器、键盘和其他这样的外围设备。任何类型的磁盘驱动器或其他外围装置可以采用这里所描述的光纤信道方法和装置(特别是例如光纤信道节点接口1220中的改进)。对于每一种装置,无论是A端口还是B端口都可以用来与任何一个给定的环路1250相连。

系统1200的一种实施例还可以有选择性地包括第二CPU信息处理系统1202’(它与系统1202是相同或相似的),它具有中央处理单元1204’(与中央处理单元1204相同)、随机存取存储器(“RAM”)1232’(与RAM 1232相同),和一个用来在通信上将中央处理单元1204’和随机存取存储器1232’耦合起来的系统总线1230’(与系统总线1230相同)。CPU信息处理单元1202’包括其自己的光纤信道节点接口1220’(与节点接口1220相同),但是却通过第二光纤信道环路1250’(与环路1250是分开并且是独立的)与一个或多个磁盘系统100相连(在所描述的例子中,它仅与磁盘系统100’相连,但在其他的实施例中,它与所有的装置或磁盘系统100到100’相连)。这种结构使得两个CPU信息处理系统1202和1202’能够采用用于每一个CPU信息处理系统1202的分开的光纤信道环路共享一个或多个磁盘系统100。然而在其他的实施例中,所有的装置100到100’以及所有的CPU信息处理系统1202到1202’都与环路1250和1250’相连。

构建本发明的一个实施例中所使用的光纤信道规范包括下面的ANSI标准:

光纤信道FC-PH X3T11/Project755D/Rev.4.3

物理和信令接口

光纤信道FC-AL X3T11/Project960D/Rev.4.5

仲裁环路

光纤信道FC-AL2 X3T11/Project 1133D/Rev.6.3

仲裁环路

光纤信道FCP X3T10/ Rev.012

SCSI协议 X3.2

69-199X

Ⅰ.保持具有动态半双工的环路公平

本发明的一个实施例提供一种用来保持(或者等效地用来提供)具有动态半双工(“DHD”)命令或指令的环路公平的公平保持装置175和方法,以及提供采用DHD命令的公平的方法。

尽管从本质上说,光纤信道是一条全双工链路(帧可以同时在光纤对中沿两个方向行进),但某些环路端口(L_Port)仅可以支持沿一个方向的数据传送。即使当端口能够进行全双工操作时,也存在可以减少环路仲裁的情况。

动态半双工(DHD)是一个在环路上由一个处于OPEN(开路)状态下的端口传送的环路原语,向处在OPENED(开路的)状态下的端口提示,没有更多的帧要传送。DHD还使得端口能够更有效地利用建立起来的电路:

1.使得仅能够进行半双工数据转发的端口在无需再仲裁的情况下沿相反的方向传送帧。

2.使得即使处于OPEN状态下的端口在已经结束了数据传送的时候,处于OPENED状态下的端口仍能够发送所有的帧。

处在OPEN状态下的端口通常发送第一CLS,用以使环路闭合。当存在全双工电路时,处于OPENED端口接收,并且可以继续发射帧,直到它不再有更多的缓冲器对缓冲器积分(BB_Credit-R_Rdy)。一旦OPENED端口不再能够发送任何帧,则必须将CLS回送到OPEN端口。

至少有两种情况,可以用来转发关闭启动(close initiative),而不是传送CLS:

1.某些结构是不能够同时在该节点处处理发送和接收转发。这些节点通常具有等待用于OPEN端口的帧,但由于它们的半双工设计,是不能利用已有的双向电路的优点的。

2.即使是可以进行全双工转发,如果OPEN端口发送CLS,OPENED端口也仅能够根据已有的积分来发送帧。(例如,一端口是OPENED,以接收新的命令,接收2 R_Rdy的,并已读取了用于OPEN端口的数据。OPENED端口在它必须闭合前只能够发送两个数据帧。)

为了避免该额外的再仲裁循环,提供该DHD原信号。由OPEN L_Port发送DHD,而不是发送CLS。发送DHD使得OPEN端口能够继续发送R_Rdy和链路控制帧(但没有数据帧)。OPENED端口记住了它已经接收了DHD,并保持关闭启动,期望当它不再有要发送到OPEN端口的帧时发送第一CLS。

“公平”在上下文中指的是一种操作方式,其中,共享资源,如光纤信道环路1250是在及时的基础上为多个用户中的每一个用户如磁盘驱动器100可用,即,没有不适当的延迟,并且对于与数据量成比例的时间,每一磁盘驱动器100需要进行转发。“播放不公平(playing unfair)”是一种操作方式,这时,用户例如CPU信息处理系统1202(用作启动器(initiator))的一个端口控制着共享资源,而不等待每一其他用户轮到的时候。播放不公平(playing unfair)在某些这样有限的情况下是需要的(例如,使运行快速的装置比运行较慢的装置有更多的机会),这是因为它使得如CPU信息处理系统1202在大量速度较慢的磁盘驱动器100上开始工作。使一个磁盘驱动器100播放不公平会使从该装置的数据转发比其他装置的转发更快,但通常会使系统性能更差,这是因为其他的磁盘驱动器100不会得到服务,并且也不会自由地进行其他的操作,并且还因为CPU信息处理系统1202将不得不等待太长的时间,以便从那些其他磁盘驱动器100得到数据(见图2)。

在如本发明中所涉及的光纤信道仲裁环路设计中,环路端口1220必须对环路1250作出仲裁。采用一种优先权系统(priority system)来判断哪一个端口1220获得了对环路1250的控制,并且采用一种“公平”来确保端口不是饥饿(starved)的。作为一种目标装置,磁盘驱动器100通常是播放公平的,并且所具有的优先等级更低,这确保了每一个驱动器100对环路1250的访问是均等的。启动器(如CPU信息处理系统1202)可以是播放不公平的,以保持驱动器序列是全满的(驱动器序列是每一个磁盘驱动器100等待发送给它的指令的等待的和当前的操作列表)。“启动器”是一个请求要由另一个装置(也称为“目标”)执行的输入/输出(“I/O”)的光纤信道环路上的装置。

“全双工”是这样一种操作方式,这时,数据可以在它被接收到端口1220内的完全相同的时刻在端口发送出去。“半双工”是另一种操作方式,这时,数据能够在一端口发送出去或接收到该端口内,但仅仅是交替的,并且不是同时进行的。

本发明的一个方面是一种被加到光纤信道仲裁环路结构(FC-AL-2)的、称为“动态半双工”的特性。即使端口能够进行全双工操作(如下面在第Ⅱ、Ⅲ、Ⅳ和Ⅴ部分中描述的设计),也会有许多种环路仲裁循环数会通过提供DHD特性而减少的情况。例如,当OPEN端口(处于OPEN状态的端口116)发送CLS原信号时,OPENED端口会根据已有的积分仅发送帧。(例如,节点接口1220的端口116是OPENED以接收新的命令,它接收两个R_RDY,并且已经读取了用于OPEN端口的数据。OPENED端口在它必须闭合前仅能够发送两个数据帧。)采用动态半双工时,OPEN端口发送DHD原语(primitive)而不是CLS,并继续发送R_RDY。这可以使已经读取了数据的磁盘驱动器100能够在接收了新命令时完成转发,并且甚至不必对环路进行仲裁。这一DHD特性可以减少仲裁循环,但也会使环路公平性失真。

例如,在按照本发明的系统1200中(见图2),信息处理系统1202向磁盘驱动器100发送一条读操作命令(磁盘驱动器100将返回多个数据帧),并发送一个DHD原语信号(这使得磁盘驱动器100在延长的时间里保持对环路1250的控制,以便在不放弃控制的情况下完成大量数据帧的转发,并且随后必须对环路1250的控制进行再仲裁)。所以,由于允许已经接收了DHD原语信号的磁盘驱动器100再次采用再仲裁窗,即使它先前已经赢得了仲裁,并且正等待下一个公平窗口。环路的公平性(所有装置具有均等访问环路资源的能力)失真了。

具有较高优先等级地址并且播放不公平(即,以牺牲其他优先等级较低的地址的装置为代价而采用其高优先等级地址对环路进行控制,即使它们已经等待了很长时间了)的启动器信息处理系统1202(见图2)赢得仲裁,并向驱动器100发送新的命令(例如,DHD命令)。该驱动器100由于已经读取了用于启动器1202的数据而已经对环路1250进行了仲裁。当驱动器100接收DHD命令时,它被允许发送其所有的数据帧和完成操作的响应。其他没有新命令而不能打开的装置(如装置100’)必须等待,直到它们“公平”赢得了仲裁为止。同时,结束了命令的装置100可能已经读取了下一个命令的数据。由于前一个命令完成了,所以启动器1202会向该驱动器100发送一条新的命令,以保持其队列完整。新的命令会使驱动器100完成另一个读转发。超时以后,某些驱动器会“饥饿”而访问环路1250,并结束那些比用于接收DHD的命令更少的命令。

本发明的改进的公平保持特性限制了允许一个节点保持对环路1250进行控制的时间长度,因此就确保了其他的节点116在一合理的时间里轮到一次(因而避免了“饥饿”)。在一个实施例中,允许一个节点116保持对环路的控制的时间长度是通过调节任一操作所转发的最大帧数来调节的。在一个实施例中,如果该节点116充分靠近其数据转发的完成,它也被允许进行该转发,即使它超过了被允许的最大帧数。

按照本发明,为了在采用动态半双工时保持环路公平性,在节点接口1200中加入数值帧极限特性。在一个实施例中,上数值极限确定的是允许多少数据帧在装置(如磁盘驱动器100)接收了DHD命令(也称为DHD“原语”)以后传送出去,除非该转发是接近完成的。在某些实施例中,数值极限是可编程的,并且是由销售商特有的登录参数(在一个实施例中)或模式页设置(另一个实施例中)或者通过一微处理器(另一个实施例中)设置成缺省值来设置的。这使得启动器1220能够进行可编程调节该使用驱动器100的应用场合(即CPU信息处理系统1202中运行的软件)下的数值极限值,或者使驱动器能够设置一合理值。

在一实施例中,本发明提供了一种如图1所示的公平保持装置175。在一个实施例中,一16位计数器160(也称为dhd_cnt_out(15:0);见图1)在接收到DHD时由init_zero信号159置零,并且对于每一传送的帧递增(采用递增器161)。比较器162检查DHD计数器160何时达到了极限寄存器163中存储的数值极限值(也称为dhd_max_frms(15:0)),以决定何时终止数据转发(关闭环路1250)。比较器162输出suspend_xfer信号164。在一种实施例中,suspend_xfer信号164使数据帧发送操作终止,并暂时使环路关闭,以使其他的装置能够使用环路1250(即,该实施例忽略下面描述的信号169和信号170,并且通过使suspend_xfer信号172等于suspend_xfer信号164而达到该极限值时终止进行转发)。在另一个实施例中,还提供-enable(使能)_DHD_suspend(中断)信号170,用于保持公平装置175,作为与门171的输入(即,该实施例忽略了下述信号169,并且当使能信号170处于“开启”时达到极限时终断转发;当使能信号170处于“断开”时,终止本发明的公平保持性能)。

在其他的实施例中,计数器160是为其他的数据转发而启动的(而不仅仅是在接收到DHD命令的时候)。在某些实施例中,计数器160被一递减计数器取代,它是通过用上述说明中装入极限寄存器163的值对其进行装载来初始化的;并且递减计数器在转发了每一帧的时候递减,并且一旦达到零,即启动信号164,从而向上述方框160、161、162和163提供等效的功能。

如上所述,在某些实施例中,计数器160监视所转发的帧数。在其他的实施例中,计数器160监视字节数或字数,或所转发的其他数据量。

同时,在其他的实施例中,计数器160由监视转发期间所经过的时间长度并且在经过了预定的时间长度以后启动信号164的定时器代替。这提供了与上述相似的功能,但根据时间长度而不是根据所转发的数据量提供公平性。在某些这样的实施例中,与门171仍然用来在少于预定的数据剩余量要转发时以及/或者终止enable_DHD_suspend信号170时,禁止suspend_xfer信号。

如上所述,在某些实施例中,计数器165监视所转发的帧数。在其他的实施例中,计数器165监视字节数或字数,或所转发的其他数据量。

同时,在其他的实施例中,计数器165由监视转发期间所经过的时间长度并且在经过了预定的时间长度以后启动信号169的定时器代替。这提供了与上述相似的功能,但根据时间长度而不是根据所转发的数据量提供公平性。在某些这样的实施例中,与门171仍然用来在少于预定的数据剩余量要转发时以及/或者终止enable_DHD_suspend信号170时,用来禁止suspend_xfer信号。

在一种实施例中,转发长度计数器165逻辑电路采用的是字数,而不是帧数。

尽管上面的描述针对的是包含动态半双工特性的实施例,但还有其他的实施例,其中,所提供的本发明的公平保持特性175是独立于DHD特性的。例如,在某些实施例中,提供公平保持特性175,但没有提供DHD特性。在其他的实施例中,两种特性都具备,但当接收到DHD命令时,采用的是公平保持特性,并且在某些其他的情况下也是这样,以便对那些情况增强其公平性。例如,在一种实施例中,将写数据从信息处理系统1202转发到磁盘驱动器100。

在一个实施例中,提供转发长度计数器165(也称为xfr_cnt_out(26:0))。转发长度计数器165由逻辑电路166递减,表示要转发的剩余字数;并且,发送长度计数器165和递减器166形成数据发送帧长度计数器82。该实施例将转发长度计数器165中计得的其余字数与最小长度寄存器168(也称为dhd_cmpl_len(26:0))中保持的可编程值比较,以使在接近完成转发时阻塞转发的终断(即,当要转发的剩余字数少于最小长度寄存器168中保持的值时,转发被定义为“接近完成”)。在一种实施例中,与门171组成驱动信号suspend_xfer172的信号164和信号160的逻辑与,这接着引起数据帧发送操作的中断,并临时使环路关闭,使其他的装置能够使用环路1250(即,该实施例忽略下述信号170,并且当达到极限时中断转发,除非剩余的字数少于寄存器168中的值)。在另一个实施例中,还提供用于公平保持特性175的enable_DHD_suspend信号170,作为与门171的输入。该中断转发(与门171的输出)的逻辑等式如下所述:

suspend_xfer信号172=(enable_DHD_suspend=‘1’

AND(dhd_cnt_out(15:0)=dhd_max_frms(15:0))

AND(xfr_cnt_out(26:0)≥(dhd_cmpl_len(26:0)))

所以,为了保持环路仲裁公平,如果接收到DHD原始信号,并且“开路”端口(该端口是打开的)处具有读数据,则该端口将数据上传到dhd_max_frms计数器,并且使环路关闭。如果转发接近结束(即,小于dhd_cmpl_len中的值),则该端口结束转发而不是立即关闭。转发就是这样完成了,而无需再次进行仲裁。dhd_max_frms和dhd_comp_len中的值是可以通过模式页(mode page)初始化或通过逻辑值来设置的,以使该特性更灵活。

当要转发数据帧时,计数器160在接收到DHD原始信号时被复位,并且接着计数器160达到极限寄存器163中保持的允许最大值。当计数器160达到极限寄存器163中保持的允许最大值时(除非转发已接近结束),则不会转发更多的数据帧,直到赢得下一个用于环路1250的时间仲裁。

“suspend_xfer”输出信号172由环路控制电路40用作端口A和B开路控制电路42的输入(见图5所示以及下面的说明),用以在已经接收到DHD时在环路上发送一个关闭信号。由于DHD模式会允许进行很长的转发以中断环路的公平,所以suspend_xfer信号172恢复或保持环路公平。

在一种实施例中,还提供suspend_xfer信号172作为输入端口环路控制状态机42/42’,并使端口开路控制状态机42/42’“关闭”环路(即释放环路1250的控制,以便允许其他装置的端口能够对环路进行仲裁),从而防止端口不公平地保持环路1250的控制。在某些实施例中,suspend_xfer信号172在转发了一定量的数据(例如字数)时被启动。在其他的实施例中,在经过了预定的时间长度以后,启动suspend_xfer信号172。不管是在哪一种实施例中,如果剩余要转发的预定数据量(例如帧数)较少,则禁止suspend_xfer信号172的启动。在上述任何一种或一些实施例中,如果禁止enable_DHD_suspend信号170,则禁止suspend_xfer信号172的启动。

Ⅱ.用于环路初始化和响应的专用帧缓冲器

对于本发明的一种实施例,已经在第三代专用集成电路(“ASIC”)芯片(光纤信道接口芯片110)中加入了帧缓冲器,以使两个端口能够同时工作。还提供了两个接收非数据帧的缓冲器(图1中也称为“接收非数据帧缓冲器”53和53’),以使能够在节点的两个端口处同时接收命令和FCP帧(光纤信道协议帧)(并且还使得能够进行全双工操作,即,在端口的一条光纤上进行接收,而在同一端口的另一条光纤上进行发送)。这就使得在同一端口和/或另一端口上的数据转发期间,在一个端口上接收新的命令,而不是在暂停转发或结束转发前进行等待。由于与传统的方法相比可以更早得到命令,本发明使得可以对命令进行分类和最佳化,同时进行数据转发,从而提高了系统1200的性能。

图3是光纤信道节点接口芯片110的方框图。本发明中的光纤信道节点-接口逻辑电路110负责光纤信道协议,包括仲裁环路逻辑和帧形成逻辑。一种实施例对于级别3 SCSI结构(见上面提及的FC AL技术规范)是最佳的,它仅采用由光纤信道协议(“FCP”)标准所定义的SCSI上级别协议。光纤信道节点接口逻辑电路110包括四个在片帧缓冲器(53,53’,55和73)用以帮助双端口和全双工操作,以及支持各种缓冲器带宽。光纤信道节点-接口逻辑电路110还与微处理器112接口相连,使得微处理器112能够配置光纤信道节点-接口逻辑电路110,并读取有关光纤信道节点-接口逻辑电路110现有条件的状态信息。

光纤信道节点-接口逻辑电路110包括两个环路端口电路20(一个用于端口A,而另一个用于端口B,每一个端口具有一个数据输入接口和数据输出接口以支持环路通信)、环路控制电路40(也称为帧发送电路40)、接收路径逻辑电路50、转发控制逻辑电路60、单个帧发送电路70、发送路径多路复用器(“mux”)79、数据帧发送路径逻辑电路80和微处理器接口90。这些块支持这样的功能,如:接收帧处理、发送数据帧产生、单个帧发送产生、转发控制和处理器接口连接。

微处理器接口电路90提供对光纤信道节点-接口逻辑电路110中寄存器和计数器进行访问的微处理器112。(在描述“微处理器”时,应当理解,这样的术语包括任何适合于可编程的逻辑装置。)在光纤信道接口的响应之前,由外微处理器112使接口寄存器初始化。而输出转发是通过该接口初始化的,并且通过该接口可得接收的转发的状态。

图3中的输入信号包括A_IN 3021,它将数据输入从光纤信道16传递到用于端口A的环路端口电路20;以及B_IN 3022,它将数据输入从光纤信道16传递到用于端口B的环路端口电路20内。DATA FROM OFF-CHIP BUFFER(来自片外缓冲器的数据)3052将数据从片外缓冲器111传递到接收路径。TO OFF-CHIP BUFFER(至片外缓冲器)3052将数据从接收路径50传递到片外缓冲器111。BUFFER STATUS(缓冲器状态)3061将状态提供给转发控制器60。进入MPU接口90的MPU ADDRESS(MPU地址)3091和MPU DATA(MPU数据)3095分别从微处理器112提供地址和数据。进入MPU接口90的READ_ENABLE(读_使能)3092和WRITE_ENABLE(写使能)3093从微处理器112提供使能信号。信号MPU 3076使微处理器112能够访问发送帧缓冲器73。A_OUT3023将数据从用于端口A的环路端口电路20提供到光纤信道16,而B_OUT3024将数据从用于端口B的环路端口电路20传递到光纤信道16。

图4是光纤信道环路端口电路20的方框图。本发明分一个实施例的光纤信道设计包括两个支持用于直接连接外围设备的双端口光纤信道接口的相同的环路端口电路20。在一个实施例中,光纤信道环路端口电路20包括接收寄存器21、8B/10B译码器逻辑电路22、字同步状态机23、接收时钟丢失检测器24、同步丢失定时器25、仲裁环路逻辑电路26以及8B/10B编码器27。

在一种实施例中,每一环路端口电路20用10位的数据接口与外收发器115接口相连(见图1)。在这样一种实施例中,收发器115使往返于并行接口(如一个10位宽或20位宽的接口)之间的数据串行化或使串行化的数据去串行化。在其他的实施例中,这些收发器115是集成在芯片110内的。(从光纤信道输入的)并行数据用接收时钟从每一收发器115的接收器部分捕获,并且在用并行8B/10B译码器译码之前转换成20位宽的格式。随后,在将16位的数据加上两个k-字符(用于表示特定顺序的集合)放入仲裁的环路逻辑电路26内之前,对其进行检查字有效性。使仲裁环路逻辑电路26的输出与发射器时钟重新同步,并且传送到接收格式逻辑电路,或通过编码器27在环路1250上再传送。在一种实施例中,操作期间,编码器27将一个8位的字符转换成一个10位的字符;在其他的实施例中,在每一操作期间,将两个或多个8位的字符转换成相应数量的10位字符。(见标题为“16B/20B编码器”的5,663,724号美国专利)。仲裁环路逻辑电路26包括环路状态机、有序集合译码器,以及弹性插入和删除功能。环路端口电路20实施仲裁环路协议,如光纤信道仲裁环路ANSI标准所定义的那样(即,上述FC-AL和/或FC-AL2)。

在一种实施例中,光纤信道数据是由收发器115串行传送,并转换成10位并行数据的。接收寄存器21用收发器115的接收器部分所产生的时钟,从收发器115捕获10位数据(A_IN 3021或B_IN 3022)。数据通过8B/10B译码器22传送前,被立即转换成20位宽(即,2个10位字符宽)。尽管被称作是“8B/10B译码器”,但在一种实施例中,译码器22在每一操作期间将一个10位的字符转换成一个8位的字符;在其他的实施例中,每次操作时,两个或多个10位的字符被转换成相应数量的8位字符。

8B/10B译码器逻辑电路22输入由接收寄存器21捕获的编码数据。两个10位字符被并行译码,以输出两个8位的字符。检查输入字符的运行非奇偶性,并将差错状态传送到字同步状态机23,以及仲裁环路逻辑电路26。在运行非奇偶性差错后的下一个有序集上强迫负运行非奇偶性。还检查是否违反编码规则,并将编码违反状态传送到字同步状态机23。

接收时钟丢失检测器24检测来自收发器115的接收时钟是什么时候停止的。当检测到“接收时钟丢失”时,使字同步状态机23复位,并防止数据进入仲裁环路逻辑电路26中的FIFO(FIFO是一个先进先出存储器,通常用作总线或具有不同速率的处理过程之间的接口)。当前填充字(“CFW”,将在下面更详细地描述)是在重新取得字同步前传送的。

字同步状态机23逻辑电路监视字同步的输入流。字同步是在用合适的字节/控制字符排列检测三个有效有序集并且没有检测到介入的无效字符时实现的。“字同步丢失”是按照FC-PH(即,FC-PH物理和信令接口X3T11/Project755D/Rev.4.3)标准定义的。当实现了字同步的时候,数据被输入到仲裁环路逻辑电路26中的FIF0内。

同步丢失定时器25用来判断对于一个以上的最大帧时间是否已经出现了字同步丢失情况(由于它可以最多占用一个帧的时间来检测三个有效的有序集)。当该定时器超时时,微处理器112由LOSS-0F-SYNC(同步丢失)中断信号4025中断,从而它可以动作。

仲裁环路逻辑电路26包括一环路弹性FIFO、环路FIFO控制逻辑电路、有序集译码逻辑电路、环路状态机逻辑电路、当前填充字选择逻辑电路、环路输出多路复用器逻辑电路,以及其他的杂项功能。环路弹性FIFO提供使输入数据(由接收时钟控制定时的)与发送时钟再同步所需的缓冲。环路FIFO控制逻辑电路监视仲裁环路逻辑电路26的状态,以判断是否需要插入或删除操作。有序集是由有序集确认逻辑电路译码的。这些有序集包括FC-PH定义的有序集(即FC-PH物理和信令接口X3T11/Project 755D/Rev.4.3),它包括帧定义符和仲裁环路有序集。当前填充字选择逻辑电路监视环路状态和译码有序集,以确定当前填充字(“CFW”)。当起动仲裁环路时,硬件状态机采用有序集译码,执行FC-AL标准中所描述的环路功能(即,光纤信道FC-AL1仲裁环路标准X3T11/Project960D/Rev.4.5,或光纤信道FC-AL2仲裁环路标准X3T11/Project1133D/Rev.6.3)。输入LOOP A TRANSMIT CONTROL OUTPUT(环路A发送控制输出)6425和LOOP B TRANSMIT CONTROL OUTPUT(环路B发送控制输出)6427从图5所示的逻辑电路向仲裁环路逻辑电路26提供输入。输出LOOP A STATES AND CONTROL(环路A状态和控制)6422和LOOP B STATES AND CONTROL(环路B状态和控制)6432控制各个环路的输出,并将状态提供给环路控制逻辑电路,由它接着向环路控制40产生请求(见图5)。输出LOOP A DATA(环路A数据)4026和LOOP B DATA(环路B数据)4027将数据提供给各个本地端口。

在一种实施例中,8B/10B编码逻辑电路27从仲裁环路逻辑电路26接受16位的数据和2个k-字符(较低的k永远是0)。在一种实施例中,输入被编码成两个10位的字符,它们是分开的,并且一次输出一个到收发器115(见图1),由其将数据转换成串行流。在其他的实施例中,两个10位的字符(即20位)被并行发送到收发器115,由其将数据转换成串行流。发送多路复用器79(见图3)还提供状态,以表示帧结尾(“EOF”)定义符是何时转发的,以使编码器27根据当前运行非奇偶性选择EOF的正确类型(或“味道”)。同时,当端口正进行传送(处于开路状态)的时候,或者当仲裁环路逻辑电路26正传送原始信号时,在每一非EOF原始信号的开头时,强迫运行非奇偶性是负的。输出信号A_OUT 3023和B_OUT 3024将数据发送到各个收发器115和115’。

图5是环路控制电路40的方框图(也称为帧发送(“XMIT”)电路40)。环路控制电路40(见图3和5)包括控制逻辑电路,向合适的仲裁环路状态机(端口A和端口B的仲裁环路逻辑电路26)产生请求,并向发送帧状态机72和81产生请求,开始发送帧或R_RDY。

发送数据顺序装置逻辑电路41包括一个在由微处理器112请求转发时启动的逻辑电路。发送数据顺序装置逻辑电路41用输入信号TRANSMIT STATUS INPUT(发送状态输入)6411监视转发,并产生用于转发每一阶段的“使能信号”(即,使能信号TRANSMIT CONTROL OUTPUTS(发送控制输出)6413)。这使得能够在没有微处理器112的介入情况下产生转发就绪和FCP响应。

环路端口A/B开路控制状态机42(端口A)和42’(端口B)处理这样的情况,即当端口由另一个L_端口打开的时候,或者环路1250打开以发送帧的时候的情况。该逻辑电路产生仲裁和使环路1250关闭的请求,以及请求发送R_RDY和各种帧,并且可以配置用于半双工或全双工操作。

开始请求仲裁时,必须满足下面的条件:

-来自微处理器112的请求,用xmit端口使能信号发送帧,

-发送端口处于监视状态,

-转发长度计数不为零,

-没有来自微处理器112要求暂停转发的请求,以及

-(非数据转发或具有转发就绪的数据写转发还没有具有满足的数据阈值或具有满足的数据阈值和满足的数据帧缓冲器阈值进行数据读转发)。

当端口配置用于半双工模式时,可以是仅在已开路状态时传送R_RDY。当端口配置用于全双工模式时,R_RDY可以是在已开路状态或开路状态下传送的。引起R_RDY传送的条件包括已有的“缓冲器对缓冲器积分(BB_Credit)和小于最大BB_Credit的现有R_RDY”。(缓冲器对缓冲器积分控制逻辑电路603向连接的端口发送缓冲器积分,使得能够发送帧。该积分是通过发送R_RDY来发出的。)

当端口配置用于半双工模式,帧可以是仅在开路状态时传送。当端口配置用于全双工模式,帧可以是在开路状态下传送的,或者在端口在由帧接收在全双工模式下开路时而处于开路状态。

当满足所有下面的条件时,产生发送帧的请求:-数据帧缓冲器55具有数据

-具有缓冲器对缓冲器积分(接收R_RDY)

-非数据转发,或数据读转发和转发长度接收器(方框609中)是非零

使环路1250闭合的条件(由端口116释放的通信信道的控制)包括:

-当进入已打开状态时,是没有缓冲器对缓冲器积分

-为了公平,即,DHD计数器160达到可以转发的帧数的预定极限(由图1中极限寄存器163所指定),并且(任选)留下大于最小长度帧数(如最小长度寄存器163所指定的)待转发,并且(任选)enable_DHD_suspend信号170工作

-当处于打开状态时,没有未完成的R_RDY,也没有更多的BB_Credit

-当端口处于打开状态时,启动处理器忙请求

-转发已完成

-没有数据读转发操作和数据

-接收到CLS原始信号,并且没有更多的BB_Credit

-微处理器暂停请求等待,并且逻辑介于帧之间

图5中,环路端口A/B开路启动状态机46(端口A)和46’(端口B)处理环路1250处于开路启动状态。逻辑电路46和46’产生发送帧的请求。每一端口有一个状态机(分别是46和46’)。这些状态机在微处理器112向它提出请求时产生发送帧的请求,并监视EOF的传输。当传送完成时,向微处理器112产生一个转发完成信号。

方框40的输入包括PORT BB_CREDIT AVAILABLE TO TRANSMIT R_RDY 6017和PORT CREDIT AVAILABLE TO TRANSMIT A FRAME 6020、LOOP A STATUS ANDCONTROL 6422和LOOP B STATES AND CONTROL 6432(见4),以及DATA AVAILABLE6019。方框40的输出包括TRANSMIT CONTROL OUTPUT 6413、LOOPA TRANSMITCONTROL OUTPUTS 6425和LOOP B TRANSMIT CONTROL OUTPUTS 6427。

Ⅲ.用于接收帧的专用帧缓冲器

在双端口光纤信道仲裁环路设计1200中,在片帧缓冲器119中的缓冲器可以用来管理入站帧和出站帧。接收和发送的帧通常是以较低转发速率存储在一个大的片外区域(例如,片外缓冲器111)内的。即使在片外缓冲器111能够对一个端口具有全转发速率,对于双端口设计,所需的带宽要大得多,从而增加了成本。可以有各种方式来构成FC-AL ASIC 110中的在片帧缓冲器119(见图1),以实现性能、硅片面积(real estate)和成本之间的平衡。本说明书详细介绍了专用帧缓冲器53和53’(整个在片帧缓冲器119的元件)的使用,用以在每一个端口上同时接收非数据类型的帧,以及提供专用的大数据帧缓冲器55(也是整个在片帧缓冲器119的元件)。在按照本发明的双端口设计中,帧可以同时在两个端口116上接收。这些帧在接收到以后通常被移送到和存储在一个更大的片外存储器111中。更详细的信息可参见标题为“环路初始化和响应的方法和专用幀缓冲器”的美国专利申请09/193,387。

Ⅳ.为了在片存储器中的数据完整性采用光纤信道CRC

按照本发明的一个方面,临时存储光纤信道帧的帧缓冲器使得帧能够在最大的光纤信道接口数据转发速率下接收。随后,帧可以在一个较低、更容易管理的速度下转发到片外存储器中。各种机制,如奇偶性、CRC或其他的冗余功能可以有选择地用来在数据存储在帧缓冲器中的时候保护数据。

在一种实施例中,通过具有数据的帧缓冲器传送接收到的光纤信道循环冗余码(“CRC”)(即,CRC是存储在具有帧的帧缓冲器内的,并且随后用帧读出),加强了数据完整性检查,可以去除使RAM加宽的多余的奇偶位。

Ⅴ.减少仲裁环路开销的方法和装置

在光纤信道仲裁环路设计1200中,环路端口116的节点1220必须仲裁对环路1250的访问。采用优先级系统来判断哪一个端口赢得了环路1250的控制,并且采用“公平”方案来确保这些端口不是饥饿的。作为目标装置,磁盘驱动器100通常比CPU信息处理系统工程202具有更低的优先级,因而结果是,驱动器100不得不等待赢得仲裁,直到更高优先级的装置完成它们的访问为止。当环路端口116的节点接口1220赢得了环路1250的控制时,在使环路1250关闭前,它必须发送尽可能多的帧,以便避免不必要的仲裁循环。但当不再具有数据的时候,环路端口116的节点接口1220使环路1250关闭,使其他的端口能够访问环路1250。这是在某些其它的控制器结构中使用的方法。本发明根据端口处有无数据,通过改变对是否要关闭环路1250的判断规则,提供了一种增强环路特性的机制,因而降低了整个环路开销。

在某些其他的控制器结构中,当传送帧结尾定义符时,该端口判断是否具有另一个帧。如果不再有数据了(例如没有一个完整的帧用于传输),则环路1250关闭。随后,又立刻有数据了,从而端口必须再次进行仲裁,并在继续转发前赢得仲裁。如果这是在进行最后一个帧的转发时发生的,则转发的完成被推迟,这会导致下一个命令前的延迟。本发明提供了一种控制器结构设计的机制,使得在端口处具有数据时环路1250保持打开。在一种实施例中,当满足下述条件时,如果端口处预期有充分的进一步的数据,则环路1250保持打开(以验证保持对环路的控制):

-至少X个幀是片外的,以及

-在数据幀缓冲器55中至少有Y个数据字。

在一种实施例中,如果具有预定数据量(至少一半的幀是在片的,并且至少一个幀是片外的),则环路1250保持打开,但整个幀在片可得之前,幀的转发不会开始。

本发明的一个目标是保持环路1250打开,并避免在端口116立刻具有数据时的多余的仲裁循环。如果等待的是一个延长的时间(例如,等待进行磁头切换所需的时间),则环路1250不必保持打开以等待具有数据,这是因为,这将阻碍环路1250上的其他端口进行转发。

结论

上面描述的是一种保持环路公平的改进的通信信道系统(1200),它包括具有一个或多个端口的信道节点(1220)。每一个端口(116)支持光纤信道仲裁环路串行通信信道(1250),并与之相连。端口中的一个将仲裁该端口连接的信道(1250)的控制,其中,信道环路(1250)的控制在赢得了仲裁以后,公平保持装置(175)至少会部分根据在第一端口和通信信道(1250)之间是否已经出现了预定的使用量,而使通信信道释放。

在一种实施例中,预定的使用量包括在预定的时间长度内保持对通信信道的控制。

在另一种实施例中,预定的使用量包括已经转发了第一预定数据量。在这样的实施例中,系统(1200)还包括监视已经转发的数据量的第一计数器。与第一计数器偶合的第一比较器电路(162)至少部分根据第一计数器(160)监视的数据量是否达到预定的数据量,释放对通信信道的控制。在一种实施例中,第一预定数据量是保持在寄存器(163)中的。

在某些实施例中,系统(1200)还包括一个监视要转发的剩余数据量的第二计数器(165)。第二比较器电路(167)与第二计数器(165)偶合,并且至少部分根据第二计数器(165)所监视的数据量是否小于第二预定数据量,禁止释放对通信信道的控制。在一种实施例中,第二预定数据量是保持在寄存器(168)中的。

在某些实施例中,系统(1200)还支持动态半双工,并且其中的第一计数器(160)和第一比较器(162)在第一端口接收到动态半双工命令时即开始启动。

在某些实施例中,第一预定数据量和预定第二数据量是可编程的量。

系统(1200)的某些实施例还包括一个与第一信道节点(1220)偶合的磁盘存储装置(114)。计算机系统(1202)包括第二信道节点(1220),其中的第二信道节点(1220与光纤信道环路(1250)的第一信道节点(1220)偶合的,以便通过光纤信道仲裁的环路串行通信信道,在第一和第二信道节点之间转发数据。

本发明的另一个方面提供了一种方法,它包括(a)对光纤信道仲裁环路串行通信信道的环路控制进行仲裁;以及(b)至少部分根据第一端口和通信信道之间是否发生了预定的使用量,释放对通信信道的控制。

在一种方法实施例中,释放步骤(b)还包括(bⅰ)判断对通信信道的控制是否保持了预定的时间;以及(bⅱ)根据判断步骤b(ⅰ),释放对环路的控制。

在另一种方法实施例中,释放步骤(b)还包括步骤(b)(ⅲ)判断是否已经转发了预定的数据量;以及(b)(ⅳ)根据判断步骤(b)(ⅲ),释放对环路的控制。在一种这样的实施例中判断步骤(b)(ⅲ)还包括(b)(ⅲ)(A)监视已经转发的帧数,提供第一值;以及(b)(ⅲ)(B)将第一值与第一预定数据量比较。

在另一种方法实施例中,释放步骤(b)还包括(bⅴ):判断第二预定量的数据是否保持要转发;以及(bⅵ):根据步骤(bⅴ),禁止释放对环路的控制。

上述方法的某些实施例还包括步骤(c):接收动态半双工命令;以及(d):在接收到动态半双工命令以后,使判断步骤(b)(ⅲ)初始化。在某些实施例中,初始化步骤(d)还包括(d)(ⅰ):可编程地设置第一预定量的数据和第二预定量的数据。

本发明的另一个方面提供了一种保持环路公平的光纤信道节点控制器系统。该系统包括:光纤信道仲裁环路串行通信信道(1250)、具有与光纤信道仲裁串行通信信道(1250)相连的第一端口(116)的第一信道节点(1220),其中,第一端口对该端口相连的通信信道的控制进行仲裁;而上述公平保持装置用来至少部分根据第一端口和通信信道之间是否出现了预定的数据使用量,释放对通信信道的控制。

应当理解,上述说明是描述性的,而非限定性的。尽管在上文中已经给出了本发明的许多特征和优点,以及各种实施例的结构和功能的细节,对这些细节作各种变更和其他的实施例对本领域的技术人员来说在研究了上述说明以后是很明显的。所以,本发明的范围是由权利要求书以及与之等效来限定。

Claims (18)

1.一种保持环路公平的通信信道系统,其特征在于,它包含:

具有第一端口用来与光纤信道仲裁环路串行通信信道相连的第一信道节点,其中,所述第一端口仲裁对该端口相连的通信信道的控制;以及

与所述第一端口偶合的公平保持装置,其中,所述第一端口仲裁对所述通信信道的环路的控制,并且在实现了控制以后,所述公平保持装置至少部分根据所述第一端口与所述通信信道之间是否出现了预定的使用量,释放对通信信道的控制。

2.如权利要求1所述的系统,其特征在于,所述预定的使用量包括所述通信信道的控制保持了预定的时间长度。

3.如权利要求1所述的系统,其特征在于,所述预定的使用量包括已经转发了的数据的第一预定量。

4.如权利要求3所述的系统,其特征在于,它还包括:

监视已经转发的数据量的第一计数器;以及

与所述第一计数器偶合的的第一比较器,用来至少部分根据所述第一计数器监视的数据量是否达到第一预定数据量,释放对通信信道的控制。

5.如权利要求3所述的系统,其特征在于,它还包括:

监视要转发的剩余数据量的第二计数器;以及

与所述第二计数器偶合的的第二比较器电路,用来至少部分根据所述第二计数器监视的数据量是否小于第二预定数据量,禁止释放对通信信道的控制。

6.如权利要求4所述的系统,其特征在于,它还包括:

监视要转发的剩余数据量的第二计数器;以及

与所述第二计数器偶合的的第二比较器电路,用来至少部分根据所述第二计数器监视的数据量是否小于第二预定数据量,禁止释放对通信信道的控制。

7.如权利要求6所述的系统,其特征在于,所述第一信道节点支持动态半双工,并且所述第一计数器和所述第一比较器在所述第一端口接收到一动态半双工命令时被初始化。

8.如权利要求7所述的系统,其特征在于,所述数量的第一预定量和所述数据的第二预定量是可编程量。

9.如权利要求4所述的系统,其特征在于,它还包含:

与所述第一信道节点偶合的磁盘存储驱动器;以及

具有第二信道节点的计算机系统,其中,所述第二信道节点与光纤信道环路中的第一信道节点偶合,以便通过所述光线信道仲裁环路串行通信信道在所述第一和第二信道节点之间转发数据。

10.如权利要求1所述的系统,其特征在于,它还包含:

光纤信道仲裁环路串行通信信道;

与所述第一信道节点偶合的磁盘存储驱动器;以及

具有第二信道节点的计算机系统,其中,所述第二信道节点与光纤信道环路中的第一信道节点偶合,以便通过所述光纤信道仲裁环路串行通信信道在所述第一和第二信道节点之间转发数据。

11.一种通信方法,其特征在于,它还包含下述步骤:

(a)仲裁对光纤信道仲裁环路串行通信信道的环路的控制;以及

(b)至少部分根据是否所述第一端口和所述通信信道之间已经出现的预定数据量,释放对通信信道的控制。

12.如权利要求11所述的方法,其特征在于,所述释放步骤(b)还包括下述步骤:

(b)(ⅰ)判断对所述通信信道的控制是否保持了预定的时间长度;以及

(b)(ⅱ)根据所述判断步骤(b)(ⅰ),释放对所述环路的控制。

13.如权利要求11所述的方法,其特征在于,所述释放步骤(b)还包括下述步骤:

(b)(ⅲ)判断是否转发了第一预定量的数据;以及

(b)(ⅳ)根据所述判断步骤(b)(ⅲ),释放对所述环路的控制。

14.如权利要求13所述的方法,其特征在于,所述判断步骤(b)(ⅲ)还包括下述步骤:

(b)(ⅲ)(A)监视已经转发的帧数,以提供第一值;以及

(b)(ⅲ)(B)将所述第一值与所述数据的第一预定量比较。

15.如权利要求13所述的方法,其特征在于,所述释放步骤(b)还包括下述步骤:

(b)(ⅴ)判断第二预定量的剩余数据是否要转发;以及

(b)(ⅵ)根据所述判断步骤(b)(ⅴ),禁止释放对所述环路的控制。

16.如权利要求13所述的方法,其特征在于,它还包括下述步骤:

(c)接收一动态半双工命令;以及

(d)在接收到所述动态半双工命令时,使所述判断步骤(b)(ⅲ)初始化。

17.如权利要求16所述的方法,其特征在于,所述出始化步骤(d)还包括下述步骤:

(d)(ⅰ)可编程设置所述数据的第一预定量和所述数据的第二预定量。

18.一种保持环路公平的光纤信道节点控制器系统,其特征在于,它包含:

光纤信道仲裁环路串行通信信道;

具有与光纤信道仲裁环路串行通信信道相连的第一端口的第一信道节点,其中,所述第一端口对所述端口相连的通信信道的控制进行仲裁;以及

公平保持装置,用来至少部分根据所述第一端口和所述通信信道之间是否出现了预定的使用量,释放对所述通信信道的控制。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US7579798P | 1998-02-24 | 1998-02-24 | |

| US60/075,797 | 1998-02-24 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN1309849A true CN1309849A (zh) | 2001-08-22 |

Family

ID=22128043

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN99803266A Pending CN1309849A (zh) | 1998-02-24 | 1999-02-24 | 采用动态半双工保持环路的公平 |

Country Status (7)

| Country | Link |

|---|---|

| US (2) | US6061360A (zh) |

| JP (1) | JP4076724B2 (zh) |

| KR (1) | KR100607392B1 (zh) |

| CN (1) | CN1309849A (zh) |

| DE (1) | DE19982971T1 (zh) |

| GB (1) | GB2349319B (zh) |

| WO (1) | WO1999043002A2 (zh) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN110637289A (zh) * | 2017-05-18 | 2019-12-31 | 凌力尔特科技控股有限责任公司 | 协调事件排序 |

| CN112565402A (zh) * | 2020-12-02 | 2021-03-26 | 浙江强脑科技有限公司 | 数据传输方法、装置、设备及计算机可读存储介质 |

Families Citing this family (76)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6430225B1 (en) * | 1996-07-19 | 2002-08-06 | Sony Corporation | Apparatus and method for digital data transmission |

| GB2349319B (en) * | 1998-02-24 | 2003-05-28 | Seagate Technology | Preserving loop fairness with dynamic half-duplex |

| US6298067B1 (en) * | 1998-05-01 | 2001-10-02 | 3 Com Corporation | Distributed arbitration scheme for network device |

| US6260092B1 (en) * | 1998-09-24 | 2001-07-10 | Philips Semiconductors, Inc. | Point to point or ring connectable bus bridge and an interface with method for enhancing link performance in a point to point connectable bus bridge system using the fiber channel |

| US6459701B1 (en) * | 1999-08-06 | 2002-10-01 | Emulex Corporation | Variable access fairness in a fibre channel arbitrated loop |

| US6986137B1 (en) * | 1999-09-28 | 2006-01-10 | International Business Machines Corporation | Method, system and program products for managing logical processors of a computing environment |

| US6651125B2 (en) * | 1999-09-28 | 2003-11-18 | International Business Machines Corporation | Processing channel subsystem pending I/O work queues based on priorities |

| AU1602101A (en) * | 1999-11-12 | 2001-06-06 | Zebrazone, Inc. | Highly distributed computer server architecture and operating system |

| US6952734B1 (en) | 2000-08-21 | 2005-10-04 | Hewlett-Packard Development Company, L.P. | Method for recovery of paths between storage area network nodes with probationary period and desperation repair |

| US6922414B1 (en) * | 2000-08-21 | 2005-07-26 | Hewlett-Packard Development Company, L.P. | Apparatus and method for dynamic command queue depth adjustment for storage area network nodes |

| US6999460B1 (en) * | 2000-10-16 | 2006-02-14 | Storage Technology Corporation | Arbitrated loop port switching |

| US20020118692A1 (en) * | 2001-01-04 | 2002-08-29 | Oberman Stuart F. | Ensuring proper packet ordering in a cut-through and early-forwarding network switch |

| US7042891B2 (en) * | 2001-01-04 | 2006-05-09 | Nishan Systems, Inc. | Dynamic selection of lowest latency path in a network switch |

| US20020110131A1 (en) * | 2001-02-12 | 2002-08-15 | Elliott Stephen J. | System and method for arbitrating access to fibre channel system for storage or LAN interface applications |

| US7385970B1 (en) * | 2001-12-07 | 2008-06-10 | Redback Networks, Inc. | Method and apparatus for balancing bandwidth among multiple ports of a network element |

| US7630300B2 (en) | 2002-07-02 | 2009-12-08 | Emulex Design & Manufacturing Corporation | Methods and apparatus for trunking in fibre channel arbitrated loop systems |

| US7664018B2 (en) | 2002-07-02 | 2010-02-16 | Emulex Design & Manufacturing Corporation | Methods and apparatus for switching fibre channel arbitrated loop devices |

| US7660316B2 (en) * | 2002-07-02 | 2010-02-09 | Emulex Design & Manufacturing Corporation | Methods and apparatus for device access fairness in fibre channel arbitrated loop systems |

| US7230929B2 (en) * | 2002-07-22 | 2007-06-12 | Qlogic, Corporation | Method and system for dynamically assigning domain identification in a multi-module fibre channel switch |

| US7154886B2 (en) * | 2002-07-22 | 2006-12-26 | Qlogic Corporation | Method and system for primary blade selection in a multi-module fiber channel switch |

| US7334046B1 (en) | 2002-08-05 | 2008-02-19 | Qlogic, Corporation | System and method for optimizing frame routing in a network |

| US7397768B1 (en) | 2002-09-11 | 2008-07-08 | Qlogic, Corporation | Zone management in a multi-module fibre channel switch |

| US7362717B1 (en) | 2002-10-03 | 2008-04-22 | Qlogic, Corporation | Method and system for using distributed name servers in multi-module fibre channel switches |

| US7319669B1 (en) | 2002-11-22 | 2008-01-15 | Qlogic, Corporation | Method and system for controlling packet flow in networks |

| US7782784B2 (en) * | 2003-01-10 | 2010-08-24 | Cisco Technology, Inc. | Port analyzer adapter |

| US7899048B1 (en) | 2003-01-15 | 2011-03-01 | Cisco Technology, Inc. | Method and apparatus for remotely monitoring network traffic through a generic network |

| US20040190554A1 (en) * | 2003-03-26 | 2004-09-30 | Galloway William C. | Fair multilevel arbitration system |

| US7355966B2 (en) * | 2003-07-16 | 2008-04-08 | Qlogic, Corporation | Method and system for minimizing disruption in common-access networks |

| US7471635B2 (en) * | 2003-07-16 | 2008-12-30 | Qlogic, Corporation | Method and apparatus for test pattern generation |

| US7453802B2 (en) * | 2003-07-16 | 2008-11-18 | Qlogic, Corporation | Method and apparatus for detecting and removing orphaned primitives in a fibre channel network |

| US7620059B2 (en) | 2003-07-16 | 2009-11-17 | Qlogic, Corporation | Method and apparatus for accelerating receive-modify-send frames in a fibre channel network |

| US7463646B2 (en) * | 2003-07-16 | 2008-12-09 | Qlogic Corporation | Method and system for fibre channel arbitrated loop acceleration |

| US7525910B2 (en) * | 2003-07-16 | 2009-04-28 | Qlogic, Corporation | Method and system for non-disruptive data capture in networks |

| US7388843B2 (en) * | 2003-07-16 | 2008-06-17 | Qlogic, Corporation | Method and apparatus for testing loop pathway integrity in a fibre channel arbitrated loop |

| US7406092B2 (en) * | 2003-07-21 | 2008-07-29 | Qlogic, Corporation | Programmable pseudo virtual lanes for fibre channel systems |

| US7580354B2 (en) * | 2003-07-21 | 2009-08-25 | Qlogic, Corporation | Multi-speed cut through operation in fibre channel switches |

| US7792115B2 (en) | 2003-07-21 | 2010-09-07 | Qlogic, Corporation | Method and system for routing and filtering network data packets in fibre channel systems |

| US7512067B2 (en) * | 2003-07-21 | 2009-03-31 | Qlogic, Corporation | Method and system for congestion control based on optimum bandwidth allocation in a fibre channel switch |

| US7430175B2 (en) * | 2003-07-21 | 2008-09-30 | Qlogic, Corporation | Method and system for managing traffic in fibre channel systems |

| US7522529B2 (en) * | 2003-07-21 | 2009-04-21 | Qlogic, Corporation | Method and system for detecting congestion and over subscription in a fibre channel network |

| US7525983B2 (en) * | 2003-07-21 | 2009-04-28 | Qlogic, Corporation | Method and system for selecting virtual lanes in fibre channel switches |

| US7447224B2 (en) * | 2003-07-21 | 2008-11-04 | Qlogic, Corporation | Method and system for routing fibre channel frames |

| US7466700B2 (en) * | 2003-07-21 | 2008-12-16 | Qlogic, Corporation | LUN based hard zoning in fibre channel switches |

| US7573909B2 (en) | 2003-07-21 | 2009-08-11 | Qlogic, Corporation | Method and system for programmable data dependant network routing |

| US7646767B2 (en) | 2003-07-21 | 2010-01-12 | Qlogic, Corporation | Method and system for programmable data dependant network routing |

| US7630384B2 (en) | 2003-07-21 | 2009-12-08 | Qlogic, Corporation | Method and system for distributing credit in fibre channel systems |

| US7894348B2 (en) | 2003-07-21 | 2011-02-22 | Qlogic, Corporation | Method and system for congestion control in a fibre channel switch |

| US7684401B2 (en) | 2003-07-21 | 2010-03-23 | Qlogic, Corporation | Method and system for using extended fabric features with fibre channel switch elements |

| US7558281B2 (en) * | 2003-07-21 | 2009-07-07 | Qlogic, Corporation | Method and system for configuring fibre channel ports |

| US7477655B2 (en) * | 2003-07-21 | 2009-01-13 | Qlogic, Corporation | Method and system for power control of fibre channel switches |

| US7522522B2 (en) * | 2003-07-21 | 2009-04-21 | Qlogic, Corporation | Method and system for reducing latency and congestion in fibre channel switches |

| US7420982B2 (en) * | 2003-07-21 | 2008-09-02 | Qlogic, Corporation | Method and system for keeping a fibre channel arbitrated loop open during frame gaps |

| US7583597B2 (en) * | 2003-07-21 | 2009-09-01 | Qlogic Corporation | Method and system for improving bandwidth and reducing idles in fibre channel switches |

| US8165136B1 (en) | 2003-09-03 | 2012-04-24 | Cisco Technology, Inc. | Virtual port based SPAN |

| US7474666B2 (en) | 2003-09-03 | 2009-01-06 | Cisco Technology, Inc. | Switch port analyzers |

| US7352701B1 (en) | 2003-09-19 | 2008-04-01 | Qlogic, Corporation | Buffer to buffer credit recovery for in-line fibre channel credit extension devices |

| JP4210922B2 (ja) * | 2003-10-27 | 2009-01-21 | ソニー株式会社 | 撮像装置および方法 |

| US7564789B2 (en) | 2004-02-05 | 2009-07-21 | Qlogic, Corporation | Method and system for reducing deadlock in fibre channel fabrics using virtual lanes |

| US7480293B2 (en) | 2004-02-05 | 2009-01-20 | Qlogic, Corporation | Method and system for preventing deadlock in fibre channel fabrics using frame priorities |

| US7340167B2 (en) * | 2004-04-23 | 2008-03-04 | Qlogic, Corporation | Fibre channel transparent switch for mixed switch fabrics |

| US7930377B2 (en) | 2004-04-23 | 2011-04-19 | Qlogic, Corporation | Method and system for using boot servers in networks |

| US7404020B2 (en) * | 2004-07-20 | 2008-07-22 | Qlogic, Corporation | Integrated fibre channel fabric controller |

| US7411958B2 (en) * | 2004-10-01 | 2008-08-12 | Qlogic, Corporation | Method and system for transferring data directly between storage devices in a storage area network |

| US8295299B2 (en) | 2004-10-01 | 2012-10-23 | Qlogic, Corporation | High speed fibre channel switch element |

| US7593997B2 (en) * | 2004-10-01 | 2009-09-22 | Qlogic, Corporation | Method and system for LUN remapping in fibre channel networks |

| US7380030B2 (en) * | 2004-10-01 | 2008-05-27 | Qlogic, Corp. | Method and system for using an in-line credit extender with a host bus adapter |

| US7519058B2 (en) | 2005-01-18 | 2009-04-14 | Qlogic, Corporation | Address translation in fibre channel switches |

| US7106537B1 (en) | 2005-02-02 | 2006-09-12 | Western Digital Technologies, Inc. | Disk drive using a timer to arbitrate periodic serial communication with a power driver |

| US7609649B1 (en) * | 2005-04-26 | 2009-10-27 | Cisco Technology, Inc. | Methods and apparatus for improving network based virtualization performance |

| US20070198761A1 (en) * | 2005-12-28 | 2007-08-23 | Duerk Vicky P | Connection management mechanism |

| US8111610B2 (en) * | 2008-01-25 | 2012-02-07 | Emulex Design & Manufacturing Corporation | Flagging of port conditions in high speed networks |

| US8542617B2 (en) * | 2008-06-02 | 2013-09-24 | Apple Inc. | Adaptive operational full-duplex and half-duplex FDD modes in wireless networks |

| US8667197B2 (en) * | 2010-09-08 | 2014-03-04 | Intel Corporation | Providing a fine-grained arbitration system |

| US10061734B2 (en) | 2015-05-20 | 2018-08-28 | International Business Machines Corporation | Adjustment of buffer credits and other parameters in a startup phase of communications between a plurality of channels and a control unit |

| US9864716B2 (en) * | 2015-05-20 | 2018-01-09 | International Business Machines Corporation | Receiving buffer credits by a plurality of channels of one or more host computational devices for transmitting data to a control unit |

| US9892065B2 (en) | 2015-05-20 | 2018-02-13 | International Business Machines Corporation | Adjustments of buffer credits for optimizing the number of retry operations and transfer ready operations |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4486739A (en) * | 1982-06-30 | 1984-12-04 | International Business Machines Corporation | Byte oriented DC balanced (0,4) 8B/10B partitioned block transmission code |

| US5367643A (en) * | 1991-02-06 | 1994-11-22 | International Business Machines Corporation | Generic high bandwidth adapter having data packet memory configured in three level hierarchy for temporary storage of variable length data packets |

| US5379386A (en) * | 1991-09-05 | 1995-01-03 | International Business Machines Corp. | Micro channel interface controller |

| US6076131A (en) * | 1992-12-30 | 2000-06-13 | Intel Corporation | Routing resource reserve/release protocol for multi-processor computer systems |

| US5598541A (en) * | 1994-10-24 | 1997-01-28 | Lsi Logic Corporation | Node loop port communication interface super core for fibre channel |

| US5638518A (en) * | 1994-10-24 | 1997-06-10 | Lsi Logic Corporation | Node loop core for implementing transmission protocol in fibre channel |

| JP3348330B2 (ja) * | 1995-04-21 | 2002-11-20 | ソニー株式会社 | 通信制御方法 |

| US5831985A (en) * | 1995-11-09 | 1998-11-03 | Emc Corporation | Method and apparatus for controlling concurrent data transmission from multiple sources in a channel communication system |

| US5663724A (en) * | 1996-03-28 | 1997-09-02 | Seagate Technology, Inc. | 16B/20B encoder |

| US5802080A (en) * | 1996-03-28 | 1998-09-01 | Seagate Technology, Inc. | CRC checking using a CRC generator in a multi-port design |

| US5751715A (en) * | 1996-08-08 | 1998-05-12 | Gadzoox Microsystems, Inc. | Accelerator fiber channel hub and protocol |

| US6298405B1 (en) * | 1997-02-14 | 2001-10-02 | Canon Kabushiki Kaisha | Data communication system, printing system and data communication apparatus |

| US6118776A (en) * | 1997-02-18 | 2000-09-12 | Vixel Corporation | Methods and apparatus for fiber channel interconnection of private loop devices |

| GB2349319B (en) * | 1998-02-24 | 2003-05-28 | Seagate Technology | Preserving loop fairness with dynamic half-duplex |

-

1999

- 1999-02-24 GB GB0018845A patent/GB2349319B/en not_active Expired - Fee Related

- 1999-02-24 KR KR1020007009408A patent/KR100607392B1/ko not_active IP Right Cessation

- 1999-02-24 US US09/256,108 patent/US6061360A/en not_active Expired - Lifetime

- 1999-02-24 DE DE19982971T patent/DE19982971T1/de not_active Withdrawn

- 1999-02-24 WO PCT/US1999/003955 patent/WO1999043002A2/en active IP Right Grant

- 1999-02-24 CN CN99803266A patent/CN1309849A/zh active Pending

- 1999-02-24 JP JP2000532850A patent/JP4076724B2/ja not_active Expired - Fee Related

-

2000

- 2000-05-08 US US09/567,174 patent/US6553036B1/en not_active Expired - Lifetime

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN110637289A (zh) * | 2017-05-18 | 2019-12-31 | 凌力尔特科技控股有限责任公司 | 协调事件排序 |

| CN112565402A (zh) * | 2020-12-02 | 2021-03-26 | 浙江强脑科技有限公司 | 数据传输方法、装置、设备及计算机可读存储介质 |

| CN112565402B (zh) * | 2020-12-02 | 2022-10-28 | 浙江强脑科技有限公司 | 数据传输方法、装置、设备及计算机可读存储介质 |

Also Published As

| Publication number | Publication date |

|---|---|

| GB2349319B (en) | 2003-05-28 |

| WO1999043002A3 (en) | 1999-10-28 |

| GB0018845D0 (en) | 2000-09-20 |

| US6553036B1 (en) | 2003-04-22 |

| US6061360A (en) | 2000-05-09 |

| GB2349319A (en) | 2000-10-25 |

| WO1999043002A2 (en) | 1999-08-26 |

| DE19982971T1 (de) | 2001-02-15 |

| JP2002504765A (ja) | 2002-02-12 |

| JP4076724B2 (ja) | 2008-04-16 |

| KR100607392B1 (ko) | 2006-08-02 |

| KR20010086257A (ko) | 2001-09-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1309849A (zh) | 采用动态半双工保持环路的公平 | |

| CN1123832C (zh) | 接收帧的方法和专用帧缓冲器 | |

| US6574688B1 (en) | Port manager controller for connecting various function modules | |

| US7787490B2 (en) | Method and apparatus for multiplexing multiple protocol handlers on a shared memory bus | |

| US7552289B2 (en) | Method and apparatus for arbitrating access of a serial ATA storage device by multiple hosts with separate host adapters | |

| EP1835413B1 (en) | Data communication circuit and arbitration method | |

| TWI408558B (zh) | 用於動態地平衡pci-express頻寬的系統 | |

| US7577773B1 (en) | Method and system for DMA optimization | |

| TWI402686B (zh) | 通用序列匯流排輸出入埠傳送器及其傳送方法 | |

| US7290066B2 (en) | Methods and structure for improved transfer rate performance in a SAS wide port environment | |

| JPH04233352A (ja) | システムメモリからネットワークへのパケットに配列されるデータのフローを制御するネットワークアダプタおよびデータのフローを制御する方法 | |

| CN1828574A (zh) | 使用串行连接总线的计算机系统及多cpu互连方法 | |

| CN1689283A (zh) | 使用仲裁系统处理超级帧的方法和装置 | |

| US20050013319A1 (en) | Method and system for an integrated host PCI I/O bridge and dual port gigabit Ethernet controller | |

| CN101052938A (zh) | 低等待时间的数据分组的接收和处理 | |

| CN1199118C (zh) | 计算机系统 | |

| US9223731B2 (en) | Arbitration circuit and control method thereof | |

| WO2006036468A1 (en) | Method and system for optimizing data transfer in networks | |

| US5898876A (en) | Efficient arbitration within point-to-point ringlet-based computer systems | |

| JP2008530650A (ja) | スケーラブルユニバーサルシリアルバスアーキテクチャ | |

| US20050083942A1 (en) | Transmit prioritizer context prioritization scheme |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C02 | Deemed withdrawal of patent application after publication (patent law 2001) | ||

| WD01 | Invention patent application deemed withdrawn after publication |