CN1431663A - 磁随机存取存储器 - Google Patents

磁随机存取存储器 Download PDFInfo

- Publication number

- CN1431663A CN1431663A CN02151849A CN02151849A CN1431663A CN 1431663 A CN1431663 A CN 1431663A CN 02151849 A CN02151849 A CN 02151849A CN 02151849 A CN02151849 A CN 02151849A CN 1431663 A CN1431663 A CN 1431663A

- Authority

- CN

- China

- Prior art keywords

- random access

- access memory

- writing line

- magnetic random

- magnetosphere

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/14—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using thin-film elements

- G11C11/15—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using thin-film elements using multiple magnetic layers

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/165—Auxiliary circuits

- G11C11/1659—Cell access

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/165—Auxiliary circuits

- G11C11/1653—Address circuits or decoders

- G11C11/1657—Word-line or row circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/71—Three dimensional array

Abstract

提供一种磁随机存取存储器。将MTJ元件在半导体衬底上边叠置成多层。MTJ元件的固定层上,连接有起读出线功能沿X方向延伸的第1导电线。MTJ元件的自由层上,连接有起写入线和读出线功能沿X方向延伸的第2导电线。写入线沿Y方向延伸,并为在其上下存在的两个MTJ元件所共用。在写入线上下存在的两个MTJ元件,相对于其写入线对称地进行配置。

Description

(相关申请的交叉引用

本申请是基于2001年11月30日提出的在先日本专利申请号2001-367755,和2001年11月30日提出的申请号2001-367941,并主张其优先权,在这里作为参考引用其全部内容。)

技术领域

本发明涉及利用因隧道磁致电阻效应存储“1”、“0”-信息的MTJ(磁隧道结)元件,构成存储单元的磁随机存取存储器(MRAM)。

背景技术

近年来,提出很多用新的原理存储信息的存储器,而其中之一,就有利用由Roy Scheuerlein et.al提出的隧道磁致电阻(以下用TMR表示)效应的存储器(例如,可参考ISSCC2000 Technical Digest p.28「A 10ns Read and WriteNon-Volatile Memory Array Using a Magnetic Tunnel Junction and FETSwitch in each Cell」)。

磁随机存取存储器,利用MTJ元件,存储“1”、“0”-信息。MTJ元件具有由两层磁性层(强磁性层)夹着绝缘层(隧道势垒)的构造。存入MTJ元件的信息,由两层磁性层的自旋方向为平行或反平行来判断。

这里,所谓平行,是指两层磁性层的自旋方向为相同,所谓反平行(anti-parallel),是指两层磁性层的自旋方向为相反。

一般,构成MTJ元件的两层磁性层中的一层成为固定自旋方向的固定层。把“1”、“0”-信息存入MTJ元件的场合,随写入信息,改变这两层磁性层中另一层(自由层)的自旋方向。

发明内容

本发明第1方面的磁随机存取存储器具备:由固定自旋方向的第1磁性层、存储数据的第2磁性层和夹入第1与第2磁性层之间的绝缘层构成的第1和第2MTJ元件;配置于该第1和第2MTJ元件之间,产生作用于该第1和第2MTJ元件的磁场的第1写入线。构成该第1MTJ元件的第1磁性层、绝缘层和第2磁性层与构成该第2MTJ元件的该第1磁性层、绝缘层和第2磁性层的位置关系为相对于第1写入线对称。

本发明第二方面的磁随机存取存储器具备:具有多层叠置的多个MTJ元件的阵列;配置于该阵列内的第1导电线;以及配置于该阵列内,具有与该第1导电线同样功能,配置在该第1导电线上边的第2导电线,该第1和第2导电线为串联或并联连接。

本发明第三方面的磁随机存取存储器具备:具有多层叠置的多个MTJ元件的阵列;以及沿上述多个MTJ元件叠置的方向延伸,在写入时产生磁场的第1写入线。

附图说明

图1是表示关于布线共用的发明参考例的剖面图。

图2是表示关于布线共用的发明参考例的剖面图。

图3是表示关于是布线共用的发明第1例的剖面图。

图4是表示关于是布线共用的发明第2例的剖面图。

图5是表示关于布线共用的发明第3例的剖面图。

图6是表示关于串联/并联连接布线的发明参考例的平面图。

图7是表示关于串联/并联连接布线的发明第1例的平面图。

图8是图7的X方向的剖面图。

图9是图7的Y方向的剖面图。

图10表示关于串联/并联连接布线的发明第2例的剖面图。

图11是图10的Y方向的剖面图。

图12表示关于串联/并联连接布线的发明第3例的剖面图。

图13表示关于串联/并联连接布线的发明第4例的剖面图。

图14表示关于串联/并联连接布线的发明第5例的剖面图。

图15是图14的构造Y方向的剖面图。

图16是表示关于串联/并联连接布线的发明第6例的剖面图。

图17是表示关于三维布线的发明参考例的立体图。

图18是表示关于三维布线的发明参考例的剖面图。

图19是表示关于三维布线的发明参考例的立体图

图20是表示关于三维布线的发明参考例的剖面图。

图21是表示关于三维布线的发明第1例的立体图

图22是表示关于三维布线的发明第2例的立体图。

图23是表示关于三维布线的发明第3例的立体图。

图24是表示关于三维布线的发明第4例的立体图。

图25是表示关于三维布线的发明第5例的立体图。

图26是表示写入线与MTJ元件的位置关系的平面图。

图27是表示关于三维布线的发明第6例的立体图。

图28是表示关于三维布线的发明第7例的立体图。

图29是表示关于三维布线的发明第8例的立体图。

具体实施方式

以下,参照附图,详细说明根据本发明实施例的磁随机存取存储器。

1.布线的共用化

(1)背景技术

近年来,提出了各种器件构造或电路构造的MRAM,其中之一,具有将多个MTJ元件连接到1个开关元件(选择晶体管)的器件构造。该构造,有利于达到单元高密度或读出容限的提高。

例如,梯形单元构造中,在上部线与下部线之间并联连接多个MTJ元件。如图1所示,该单元构造中,在衬底上边多层(本例中,为4层)叠置多个MTJ元件10。并且,在各层中,将多个MTJ元件10并联连接到上部线11与下部线12之间。

上部线11沿X方向延伸,其一端连到选择晶体管14。下部线12也沿X方向延伸,其一端连到读出放大器(S/A)15等外围电路。本例中,读出电流沿着上部线11、MTJ元件10、下部线12的路径,即,沿X方向流动。写入线13与MTJ元件10邻接进行配置,并沿Y方向延伸。

图2的单元构造是将图1下部线与写入线一体化的例子。即,下部线12沿Y方向延伸,其一端连到读出放大器(S/A)。写入时下部线12起写入线功能,读出时,下部线12起读出(read)线功能。即,读出电流首先流入上部线(X方向)11,而后,经由MTJ元件10流到下部线(Y方向)12。

磁随机存取存储器的基本构造是,每1个MTJ元件对应1个开关元件(选择晶体管)的1单元-1晶体管构造。但是,多层叠置MTJ元件的器件构造中,如果每1个MTJ元件对应1个开关元件的话,开关元件数就不断增加,将不利于单元高密度化。

因此,采用多层叠置MTJ元件10的器件构造场合,即使每1个MTJ元件不对应1个开关元件,也采用能进行读出动作或写入动作这样的器件构造。

例如,图1和图2中表示的器件构造中,对于MTJ元件10的阵列各层,把多个MTJ元件10连接到上部线11与下部线12之间。而且,例如,将选择晶体管14连接到上部线11的一端,将读出放大器(S/A)15连接到下部线12的一端。

可是,这时,图1的例子中,在MTJ元件10的阵列各层上,需要配置上部线(读出/写入线)11、下部线(读出线)12和写入线13总计3条线,并且,图2的例子中,MTJ元件10的各层上,需要配置上部线(读出/写入线)11和下部线(读出/写入线)12总计2条线。

而且,在衬底上边多层叠置的MTJ元件阵列内,配置这种写入线或读出线(电流总线)时,随着MTJ元件的叠置数继续增多,器件构造将复杂化,而且,因制造步骤数的增大而引起工艺成本增加就成了问题。

并且,MTJ元件的特性,受其配置的表面(底膜)的平整度影响很大。该平整度因MTJ元件的叠置数越多越恶化,所以随MTJ元件的叠置数增加,MTJ元件特性的恶化变成问题。

(2)概要

本发明例(共用布线)应用于具有多层叠置MTJ元件阵列构造的磁随机存取存储器。本发明例的磁随机存取存储器的特征是,在由上下方向邻接的2个MTJ元件共用1个MTJ元件上需要的2条写入线中的1条。并且,2个MTJ元件相对于共用的1条写入线为对称配置。

因此,可以减少MTJ元件阵列内配置的导线数,能够达到因制造步骤数削减而降低工艺成本。并且,也能抑制伴随MTJ元件叠置数增加带来的平整度恶化,能够提高MTJ元件的特性。

(3)实施例

①第1实施例

图3表示本发明第1实施例的磁随机存取存储器的单元阵列部分。

半导体衬底上边,把多个MTJ元件叠置成多层(本例中,为4层)。并且,各层中,MTJ元件10在X-Y平面内构成阵列。图3中,省去了有关沿Y方向的MTJ元件列。

写入线13配置在上下方向邻接的2个MTJ元件10之间,并沿Y方向延伸着。而且,本例中,因为由上下方向邻接的2个MTJ元件共用写入线13,所以采用以下这样的单元构造。即,写入线13不是在全部的层之间配置,而是例如,从半导体衬底一侧数起,配置在奇数层的MTJ元件10正上方,但在偶数层的MTJ元件10正下方。

本例中,从半导体衬底一侧数起,在第1层MTJ元件与第2层MTJ元件之间和第3层MTJ元件与第4层MTJ元件之间,分别配置写入线13。即,从半导体衬底一侧数起,第2层MTJ元件与第3层MTJ元件之间没有配置写入线13。

并且,本例中,相对于写入线13,对称配置其上下存在的2个MTJ元件。

即,MTJ元件10是由两层磁性层(强磁性层)和夹于其间的绝缘层(隧道势垒)构成,两层磁性层中固定自旋方向的固定层(或称钉扎层),被配置在远离写入线13的位置。并且,两层磁性层中能自由改变自旋方向的自由层被配置在靠近写入线13的位置。写入线13位于距该上下存在的2个MTJ元件10等距离的位置离开这2个MTJ元件。

各层中,MTJ元件10的固定层上连接有起读出线功能的第1导电线11A。第1导电线11A为沿X方向延伸,而且,共同连接到X方向配置的多个MTJ元件10的固定层。读出放大器(S/A)15连接到第1导电线11A的一端。

并且,各层中,起写入线和读出线功能的第2导电线12A连接到MTJ元件10的自由层。第2导电线12A沿X方向延伸,而且,共同连接到X方向配置的多个MTJ元件10的自由层。起选择晶体管功能的选择晶体管14连接到第2导电线12A的一端。

按照这种第1实施例的单元构造,为了给1个MTJ元件写入数据,由上下方向邻接的2个MTJ元件,使需要2条写入线之中的1条共有化。因此,可以减少MTJ元件阵列内所配置的导线数,能够达到因制造步骤次数的削减而降低工艺成本。并且,也能抑制伴随MTJ元件的叠置数增加带来的平整度恶化,可以提高MTJ元件特性。

并且,按照第1实施例的单元构造,把配置于写入线上下的2个MTJ元件配置成使其对于该写入线互相对称。因此,关于由写入线中流动的电流发生的磁场,作用于其上下配置的2个MTJ元件自由层的磁场强度实质上变成相同,能够控制作用于各MTJ元件的磁场离散。

②第2实施例

图4表示本发明第2实施例的磁随机存取存储器的单元阵列部分。

本实施例的磁随机存取存储器的特征是,与图3的磁随机存取存储器比较时,省略图3的读出线12A,使图3的写入线13具有读出线的功能。

在半导体衬底上,把多个MTJ元件10叠置成多层(本例中,为4层)。并且,各层中,MTJ元件10在X-Y平面内构成阵列。图4中,省去了有关沿Y方向的MTJ元件列。

各层中,MTJ元件10的自由层上连接省起写入线和读出线功能的第1导电线11A。第1导电线11A沿X方向延伸,而且,共同连接到X方向配置的多个MTJ元件10的自由层。第1导电线11A的一端,连接有作为选择晶体管的选择晶体管14。

并且,各层中,MTJ元件10的固定层上连接有起写入线和读出线功能的第2导电线12A。第2导电线12A沿Y方向延伸,而且,共同连接到Y方向配置的多个MTJ元件10的固定层。读出放大器(S/A)15连接到第2导电线12A的一端。

第2导电线12A被配置在上下方向邻接的2个MTJ元件10之间。即,第2导电线12A被其上下方向邻接的2个MTJ元件所共用。为此,第2导电线12A不是配置于全部的层之间,而是配置于例如,从半导体衬底一侧数起,第奇数个MTJ元件10正上方,而且,在第偶数个MTJ元件10正下方。

本例中,从半导体衬底一侧数起,在第1层MTJ元件与第2层MTJ元件之间和第3层MTJ元件与第4层MTJ元件之间,分别配置第2导电线12A。即,从半导体衬底一侧数起,第2层MTJ元件与第3层MTJ元件之间没有配置第2导电线12A。

并且,本例中,相对于第2导电线12A,对称配置其上下存在的2个MTJ元件。即,MTJ元件10是由两层磁性层(强磁性层)和夹于其间的绝缘层(隧道势垒)构成,2个磁性层中固定自旋方向的固定层,被配置在靠近第2导电线12A的位置。并且,两层磁性层中能自由改变自旋方向的自由层,被配置在远离第2导电线12A的位置。

按照这种第2实施例的单元构造,为了给1个MTJ元件写入数据,由上下方向邻接的2个MTJ元件,使需要2条写入线之中的1条共有化。因此,不用写入专用的导线或读出专用的导线,把1条导线使用于写入和读出,所以能够大幅度减少导线数。本例中,对1个MTJ元件的导线数实质上为1.5条。因此,能够达到因制造步骤次数的削减而降低工艺成本。并且,也能抑制伴随MTJ元件的叠置数增加带来的平整度恶化,可以提高MTJ元件特性。

并且,按照第2实施例,把配置于写入线上下的2个MTJ元件配置成使其对于该写入线互相对称。因此,关于由写入线中流动的电流发生的磁场,作用于其上下配置的2个MTJ元件自由层的磁场强度,基本上变成相同,能够控制作用于各MTJ元件的磁场离散。

③第3实施例

图5表示本发明第3实施例磁的随机存取存储器的单元阵列部分。

本实施例的磁随机存取存储器的特征是,与图4的磁随机存取存储器比较时,图4的第1导电线(写入线和读出线)11A被其上下方向邻接的2个MTJ元件所共用。

半导体衬底上边,把多个MTJ元件叠置成多层(本例中,为8层)。并且,各层中,MTJ元件10在X-Y平面内构成阵列。图5中,省去了有关沿Y方向的MTJ元件列。

各层中,MTJ元件10的自由层上,连接有起写入线和读出线功能的第1导电线11A。第1导电线11A沿X方向延伸,而且,共同连接到X方向配置的多个MTJ元件10的自由层。第1导电线11A的一端,连接有作为选择晶体管的选择晶体管14。

第1导电线11A被配置在上下方向邻接的2个MTJ元件10之间。即,第1导电线11A被其上下方向邻接的2个MTJ元件所共用。为此,第1导电线11A,不是配置于全部的层之间,而是配置于例如,从半导体衬底一侧数起,第奇数个MTJ元件10的正下方,而且,在第偶数个MTJ元件10的正上方。

本例中,从半导体衬底一侧数起,在第1层MTJ元件的正下方与第2层MTJ元件和第3层MTJ元件之间、第4层MTJ元件与第5层MTJ元件之间,第6层MTJ元件与第7层MTJ元件之间。第8层MTJ元件的正上方,分别配置第1导电线11A。

并且,本例中,相对于第1导电线11A,对称配置其上下存在的2个MTJ元件。即,MTJ元件10是由两层磁性层(强磁性层)和夹于其间的绝缘层(隧道势垒)构成,两层磁性层中固定自旋方向的固定层,被配置在远离第1导电线11A的位置。并且,两层磁性层中能自由改变自旋方向的自由层,被配置在离第1导电线11A很近的位置。

并且,各层中,MTJ元件10的固定层上,连接有起写入线和读出线功能的第2导电线12A。第2导电线12A沿Y方向延伸,而且,共同连接到沿Y方向配置的多个MTJ元件10的固定层。读出放大器(S/A)15连接到第2导电线12A的一端。

第2导电线12A被配置在上下方向邻接的2个MTJ元件10之间。即,第2导电线12A被其上下方向邻接的2个MTJ元件所共用。为此,第2导电线12A不是配置于全部的层之间,而是配置于例如,从半导体衬底一侧数起,第奇数个MTJ元件10的正上方,而且,在第偶数个MTJ元件10的正下方。

本例中,从半导体衬底一侧数起,在第1层MTJ元件与第2层MTJ元件之间、第3层MTJ元件与第4层MTJ元件之间、第5层MTJ元件与第6层MTJ元件之间、以及第7层MTJ元件与第8层MTJ元件之间,分别配置第2导电线12A。

并且,本例中,相对于第2导电线12A,对称配置其上下存在的2个MTJ元件。即,MTJ元件10是由两层磁性层(强磁性层)和夹于其间的绝缘层(隧道势垒)构成,两层磁性层中固定自旋方向的固定层,被配置在靠近第2导电线12A的位置。并且,两层磁性层中能自由改变自旋方向的自由层,被配置在远离第2导电线12A的位置。

按照这种第3实施例的单元构造,把连接MTJ元件自由层的导线和连接固定层的导线,规定可用作写入线和读出线,而且,由上下方向邻接的2个MTJ元件共用。

因此,可以大幅度减少MTJ元件阵列内配置的导线数,能够达到因制造步骤次数的削减而降低工艺成本。并且,也能抑制伴随MTJ元件的叠置数增加带来的平整度恶化,可以提高MTJ元件特性。

并且,按照第3实施例的单元构造,把配置于写入线上下的2个MTJ元件配置成使其对于该写入线互相对称。因此,关于由写入线中流动的电流发生的磁场,作用于其上下配置的2个MTJ元件自由层的磁场强度,实质上变成相同,能够控制作用于各MTJ元件的磁场离散。

(4)其它

上述第1到第3实施例中,对多层叠置MTJ元件的阵列构造的各层,都将X方向或Y方向的MTJ元件上共同连接写入线(或读出线)的器件作为前提进行说明,但是本发明的应用不限于这样的器件。

本发明只要是具有多层叠置MTJ元件阵列构造的磁随机存取存储器,也都可能应用于这样构造的器件。

并且,上述的第1到第3实施例中,与MTJ元件阵列内导线连接的晶体管一般的是MOS晶体管,但也可以是双极晶体管或二极管。

(5)结束语

以上,如说明的那样,按照本发明例的磁随机存取存储器,采用在其上下存在的MTJ元件之间共用写入线的至少1条的办法,可以减少MTJ元件阵列内配置的导线数,能够达到因制造步骤次数的削减而降低工艺成本。并且,因为减少MTJ元件阵列内配置的导线数,所以能够抑制伴随MTJ元件的叠置数增加带来的平整度恶化,可以提高MTJ元件特性。

2.串联(蛇形)/并联连接布线

(1)背景技术

磁随机存取存储器的基本构造是,1个MTJ元件对应1个开关元件(选择晶体管)的1单元-1晶体管构造。但是,多层叠置MTJ元件的器件构造中,如果1个MTJ元件对应1个开关元件的话,开关元件数就不断增加,将不利于单元高密度化。

因此,在多层叠置MTJ元件10的器件构造场合,即使1个MTJ元件不对应1个开关元件,也采用能进行读出动作或写入动作这样的器件构造。

例如,图1和图2中表示的器件构造中,对于MTJ元件10的阵列各层,把多个MTJ元件10连接到上部线11与下部线12之间。而且,例如,将选择晶体管14连接到上部线11的一端,将读出放大器(S/A)15连接到下部线12的一端。

可是,这时,图1的例子中,对于各个MTJ元件10的阵列各层上配置的上部线11就需要选择晶体管。并且,如图6所示,上部线11在MTJ元件10的阵列16上边,沿X方向延伸。即,规定集中于阵列16的端部区域17,配置连接到上部线11的选择晶体管。

同样,对于各个在MTJ元件10的阵列各层上配置的下部线(读出线)12就需要读出放大器(晶体管)。即,如图6所示,下部线12在MTJ元件10的阵列16上边沿X方向延伸,所以规定集中于阵列16的端部区域18,配置连接到下部线12的选择晶体管。

同样,对于各个在MTJ元件10的阵列各层上配置的写入线13,也需要选择晶体管。即,如图6所示,写入线13在MTJ元件10的阵列16上边沿Y方向延伸,所以规定集中于阵列16的端部区域19A、19B,配置连接到写入线13的选择晶体管。

尽管,大家都知道,在对MTJ元件的数据写入/读出动作的方面,起因于MTJ元件的特性,需要大电流。因此,可以预料,连接到下部线12和写入线13的晶体管尺寸必然需要增大。

因而,配置用于在阵列16外围配置电流驱动晶体管的区域17、18、19A、19B的面积也将增大,无法实现芯片尺寸的缩小、每芯片制造成本的降低等。并且,因为MTJ元件与叠置数成比例,选择晶体管的个数也增加,MTJ元件叠置个数变成非常多的话,在选择晶体管的布局方面需要很多时间,开发时间就拉长了。

(2)概要

本发明例(串联/并联连接布线)将应用于具有多层叠置MTJ元件阵列构造的磁随机存取存储器。

本发明例的磁随机存取存储器的特征是,在MTJ元件阵列的1行或1列内,串联或并联连接1层中每1个配置有相同功能的多条导线(例如,写入线、读出线等)。这时,对串联/并联连接的导线而言,其一端只要配置1个,或,其两端各配置1个晶体管就行,因而可以减少MTJ元件阵列端部配置的晶体管数。

并且,按照本发明例的器件构造,不管MTJ元件的叠置数,只要把晶体管连接到MTJ元件阵列内的1行或1列内串联或并联连接的导线上就行,所以即使增加MTJ元件的叠置数,增大存储器容量,既没有增加晶体管数,也不会使其布局复杂化。

进而,在MTJ元件布局的1行或1列内,不管MTJ元件的叠置数,晶体管数常常固定,所以把MTJ元件阵列制成1个小块,集合多个块成为大的存储单元阵列也行。这时,MTJ元件阵列的正下方,可以配置晶体管或读出放大器等的核心电路。

(3)实施例

①第1实施例

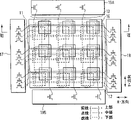

图7表示本发明第1实施例磁随机存取存储器的单元阵列部分布局。图8表示沿图7的单元阵列部分的X方向剖面图,即,沿图7的VIII-VIII线的剖面图。

在半导体衬底上边,把多个MTJ元件10叠置成多层(本例中,为3层)。并且,各层中,MTJ元件10在X-Y平面内构成阵列。

上部线11和下部线12一起沿X方向延伸,并在两线11、12之间,配置沿X方向配置的多个MTJ元件10。上部线11的一端,连接有选择晶体管14。并且,下部线12的一端,连接有读出放大器(S/A)15等的外围电路。

本实施例中,上部线11和下部线12起读出线功能。即,读出数据时,读出电流沿着上部线11、MTJ元件10、下部线12这样的路径,即,沿X方向流动。

就具体的读出方法来说,首先,在上部线11和下部线12中流动读出电流,例如,用读出放大器,检测这时的下部线12电位。其次,给选定的MTJ元件(存储单元)写入规定数据(“0”或“1”),而后,再次在上部线11和下部线12中流动读出电流,用读出放大器,检测这时的下部线12的电位。在第1次和第2次的读出中,如果用读出放大器检出的电位相同,那么就将选定的MTJ元件数据判断为与规定数据相同,如果不同,则选定的MTJ元件数据判断为与规定数据不同。最后,给选定的MTJ元件重新写入正确的数据。

在MTJ元件10阵列的各层,写入线13被配置在MTJ元件10上边,并沿Y方向延伸。并且,写入线13接近MTJ元件10的自由层进行配置。进而,把沿X方向配置的多个MTJ元件构成的组规定为1列,把沿Y方向偏置的多个MTJ元件构成的组规定为1行的场合,本例中,MTJ元件10阵列的1行内,串联连接各层配置的写入线13。

即,如图9所示,在MTJ元件10阵列的端部,通过接触塞,把上层的写入线13与下层的写入线13互相电连接起来。图9中,为了简化,省去了上部线和下部线。

就具体的写入方法来说,例如,在作为写入线功能的选定1列内的下部线12里,根据写入数据值,流动向着一方向或另一方向的写入电流。同时,在选定1行内的写入线13里流动向着一方向的写入电流。因此,给配置于下部线12与写入线13之间的MTJ元件(存储单元)10写入规定数据。

这样,本实施例中,MTJ元件10阵列的1行内,采用各层配置具有同样功能的线,即,串联地连接的写入线的办法,对该写入线,只要其两端每端配置1个晶体管就行。因此,能够大幅度减少MTJ元件10的阵列16的端部区域19A、19B上配置的晶体管数。

并且,按照这种器件构造,不管MTJ元件10的叠置数,MTJ元件10的阵列16的1行内,只要把晶体管连接到串联连接的导线上就行,即使增加MTJ元件10的叠置数,谋求存储容量的增大,也没有增加晶体管,也不会使其布局复杂化。

进而,连接到MTJ元件10的阵列16的行内各层中配置的写入线13的晶体管数常常为固定,所以把MTJ元件10的阵列16制成1个小块,集合多个块构成大的存储单元阵列也行。这时,如图9所示,各块内MTJ元件10的正下方,可以配置晶体管或读出放大器等的核心电路。

另外,图7中,记载着叠置的的MTJ元件、沿X方向延伸和沿Y方向洋使的线,各自在各层内使其互相偏移,这是为了分开容易说明的缘故,实际上不管互相偏移,或完全重叠,哪种也都可以。

②第2实施例

图10表示本发明第2实施例的磁随机存取存储器的单元阵列部分。

本实施例的磁随机存取存储器的特征是,若与图8的磁随机存取存储器比较,把图8的MTJ元件10叠置数分成4层。至于其它方面,成为与图8的磁随机存取存储器同样。

在半导体衬底上边,把多个MTJ元件叠置成多层(本例中,为4层)。并且,各层中,MTJ元件10在X-Y平面内构成阵列。

上部线11和下部线12一起沿X方向延伸,并在两线11、12之间,配置沿X方向配置的多个MTJ元件10。上部线11的一端,连接有选择晶体管14。并且,下部线12的一端,连接有读出放大器(S/A)15等的外围电路。

上部线11和下部线12起读出线功能。即,读出数据时,读出电流沿着上部线11、MTJ元件10、下部线12这样的路径,即,沿X方向流动。

在MTJ元件10的阵列各层,写入线13被配置在MTJ元件10上边,并沿Y方向延伸。并且,写入线13接近MTJ元件10的自由层进行配置。进而,把沿X方向配置的多个MTJ元件构成的组规定为1列,把沿Y方向偏置的多个MTJ元件构成的组规定为1行的场合,本例中,MTJ元件10的阵列1行内,串联连接各层配置的写入线13。

即,如图11所示,在MTJ元件10的阵列端部,通过接触塞,把上层的写入线13与下层的写入线13互相电连接起来,图11中,为了简化,省去了上部线和下部线。

本实施例中,MTJ元件10的叠置数为4层。即,MTJ元件10的叠置数为偶数层(2、4、6、…层)的场合,如图1所示,将用于连接写入线13和晶体管的2个接触部分,一起配置在MTJ元件10阵列部的一个端部。

这时,如图11所示,例如,在邻接块BK0的块BK1阵列的正下方,配置与块BK0内写入线13的一端连接的晶体管,并在块BK0陈列的正下方,配置与块BK0内写入线13的另一端连接的晶体管。

另外,正如上述第1实施例一样,MTJ元件10的叠置数为奇数层(3、5、7、…层)的场合,如图9所示,在MTJ元件10阵列部分的一个端部配置用于连接写入线13的一端和晶体管的接触部,在与MTJ元件10阵列部分的一端部对向的另一端部配置用于连接写入线13另一端和晶体管的接触部。

于是,这时,如图9所示,例如,在块BK0的阵列的正下方,各自配置连接块BK0内的写入线13一端和另一端的晶体管。

这样,本实施例中,MTJ元件10阵列的1行内,采用各层配置具有同样功能的线,即,串联地连接的写入线的办法,对该写入线,只要其两端每端配置1个晶体管就行。因此,能够大幅度减少MTJ元件10的阵列16的端部配置的晶体管数。

并且,按照这种器件构造,不管MTJ元件10的叠置数,MTJ元件10的阵列1行内,只要把晶体管连接到串联连接的导线上就行,所以即使增加MTJ元件10的叠置数,谋求存储容量的增大,也没有增加晶体管,也不会使其布局复杂化。

进而,连接到MTJ元件10的阵列行内的各层中配置的写入线13的晶体管数常常为固定,所以把MTJ元件10的阵列制成1个小块,集合多个块构成大的存储单元阵列也行。这时,如图11所示,各块内MTJ元件10的正下方,可以配置晶体管或读出放大器等的核心电路。

③第3实施例

图12表示本发明第3实施例的磁随机存取存储器的单元阵列部分。

本实施例的磁随机存取存储器的特征是,若与图10的磁随机存取存储器比较,对每1层改变图10的MTJ元件10的固定层磁化方向,至于其它方面,都与图10的磁随机存取存储器同样。

在半导体衬底上边,把多个MTJ元件叠置成多层(本例中,为4层)。并且,各层中,MTJ元件10在X-Y平面内构成阵列。

上部线11和下部线12一起沿X方向延伸,并在两线11、12之间,配置沿X方向配置的多个MTJ元件10。上部线11的一端,连接有选择晶体管14。并且,下部线12的一端,连接有读出放大器(S/A)15等的外围电路。

上部线11和下部线12起读出线功能。即,读出数据时,读出电流沿着上部线11、MTJ元件10、下部线12这样的路径,即,沿X方向流动。

在MTJ元件10的阵列各层,写入线13被配置在MTJ元件10上,并沿Y方向延伸。并且,写入线13接近MTJ元件10的自由层进行配置。进而,把沿X方向配置的多个MTJ元件构成的组规定为1列,把沿Y方向偏置的多个MTJ元件构成的组规定为1行的场合,本例中,MTJ元件10的阵列1行内,串联连接各层配置的写入线13。

即,如图11所示,在MTJ元件10的阵列端部,通过接触塞,把上层的写入线13与下层的写入线13互相电连接起来。

尽管,上述第2实施例中,由图11很清楚,在Y-Z平面内蛇形配置写入线13。这时,如图12所示,写入线13里流动一个方向电流时,在各层中,写入线13里流动的电流方向,每1层变成互相相反方向。

图12的场合,对第奇数层的写入线13,即,最靠近半导体衬底的第1层的写入线13和第3层的写入线13来说,从纸面表面向内流动写入电流,对第偶数层的写入线13,即,第2层和第4层的写入线13来说,从纸面内向外表面流动写入电流。

在这种状况下,例如,假设全部MTJ元件10的固定层磁化方向都是相同的,例如,给第奇数层的MTJ元件和第偶数层的MTJ元件写入相同数据的场合,写入线13里应该流动不同方向的写入电流。

即,全部MTJ元件10的固定层磁化方向为相同,下部线12的写入电流方向为一定的场合,如要是写入线13里只流动一个方向的写入电流的话,那么各层MTJ元件10的自由层磁化方向,对每层变成相反方向。即,各层MTJ元件10的磁化状态,对每1层,变成平行、反平行,也不管同样动作,对于各层的MTJ元件10,写入不同的数据。

这样,第2实施例中,写入线13里流动一方向电流的场合,各层中,流过写入线13的电流变成互相相反方向,所以有可能使写入动作的控制方法复杂化。

因此,本实施例中,为了解决这种事情,如图12所示,提出每1层改变MTJ元件10的固定层磁化方向的方案。这时,如果写入线13里只流动一方向写入电流,各层MTJ元件10的自由层磁化方向,对每1层都变成相反方向,而各层MTJ元件10的磁化状态对于各层变成相同(平行或反平行)。即,给各层的MTJ元件10,写入同样数据。

关于MTJ元件10的固定层磁化方向,按照现有的工艺,能够很容易对每1层改变磁化方向。即,为了使每1层变更MTJ元件10的固定层磁化方向,淀积构成固定层的材料时,就可以调整磁场的方向。

另外,本实施例中,通过对每1层变更MTJ元件10的固定层磁化方向,解决写入线13蛇形变动的问题,但除此以外,也有几个解决方法。

例如,虽然写入控制变为复杂,但是如上述那样,也可以一面给写入线13流动不同方向的电流,并且,一面变更流入下部线12的写入电流的方向。并且,可以认为,各层以不同的磁化状态保存同一数据,对各层变更数据判定的条件也行。

这样,本实施例中,变更每1层中MTJ元件的固定层磁化方向。这时,写入线里只流动一方向写入电流的话,各层MTJ元件的自由层磁化方向在每1层就变为相反方向,然而各层的MTJ元件磁化状态,对各层却成了相同(平行或反平行)。

因而,按照本实施例,获得与上述第2实施例磁的随机存取存储器同样的效果,同时也没有使写入动作的控制方法复杂化。

④第4实施例

图13表示本发明第4实施例的磁随机存取存储器单元阵列部分概要图。图13中,为了简化,省去了连接MTJ元件的上部线和下部线。

本实施例的磁随机存取存储器的特征是,若与图11的磁随机存取存储器比较,不是串联连接,而是并联累进图11的MTJ元件10的各层中配置的写入线13,至于其它方面,都与图11的磁随机存取存储器同样。

在半导体衬底上边,把多个MTJ元件叠置成多层(本例中,为4层)。并且,各层中,MTJ元件10在X-Y平面内构成阵列。

关于本实施例,也如图10所示,上部线11和下部线12一起沿X方向延伸,并在两线11、12之间,配置沿X方向配置的多个MTJ元件10。上部线11的一端,连接有选择晶体管14。并且,下部线12的一端,连接有读出放大器(S/A)15等的外围电路。

如图13所示,在MTJ元件10的阵列各层,写入线13被配置在MTJ元件10上边,并沿Y方向延伸。并且,写入线13接近MTJ元件10的自由层进行配置。进而,把沿X方向配置的多个MTJ元件构成的组规定为1列,把沿Y方向偏置的多个MTJ元件构成的组规定为1行的场合,本例中,MTJ元件10的阵列1行内,并联连接各层配置的写入线13。

即,在MTJ元件10的阵列端部,通过接触塞,把上层的写入线13与下层的写入线13互相电连接起来。

尽管,上述的第2实施例中,因为各层的写入线13互相串联连接,从图11很清楚,写入线13在Y-Z平面内为蛇形配置。对此,本实施例中,因为各层的写入线13互相并联连接,从图13很清楚,写入线13在Y-Z平面内呈梯子状。

本实施例中,写入线13里流动一方向电流的场合,与第2实施例不同,各层中。写入线13里流动的电流方向,成为互相相同方向。

所以,按照本实施例,获得与上述第2实施例的磁随机存取存储器同样的效果,同时如上述第2实施例那样,即使不采取对每1层变更MTJ元件的固定层磁化方向的对策,也容易控制写入动作。

并且,本实施例中,因为各层的写入线并联连接,在与MTJ元件阵列互相对向的2个端部各设置一个写入线与晶体管的接触部。因此,把MTJ元件阵列制成1个小块,集合多个块构成存储单元阵列也行。这时,各块内的MTJ元件阵列的正下方,很容易配置晶体管或读出放大器等的核心电路。

⑤第5实施例

图14表示本发明第5实施例的磁随机存取存储器的单元阵列部分。图15表示沿图14的单元阵列部分的Y方向剖面图。

第5实施例是组合上述第1实施例与「共用布线」的例子。

在半导体衬底上边,把多个MTJ元件叠置成多层(本例中,为4层)。并且,各层中,MTJ元件10在X-Y平面内构成阵列。

写入线13配置在上下方向邻接的2个MTJ元件10之间,并沿Y方向延伸。而且,本例中,由上下方向邻接的2个MTJ元件共用写入线13。即,写入线13不是配置在全部层之间,而是例如,从半导体衬底一侧数起,配置于第奇数层的MTJ元件10的正上方和第偶数层的MTJ元件10的正下方。

并且,把沿X方向配置的多个MTJ元件构成的组规定为1列,把沿Y方向偏置的多个MTJ元件构成的组规定为1行的场合,本例中,MTJ元件10的阵列1行内,把各层配置的写入线13串联连接起来。

并且,相对于写入线13,对称配置其上下存在的MTJ元件。即,MTJ元件10的两层磁性层中固定自旋方向的固定层配置于远离写入线13的位置,并且,能自由改变MTJ元件10的两层磁性层中自旋方向的自由层被配置在靠近写入线13的位置。写入线13位于距该上下存在的2个MTJ元件10等距离的位置,而且,离开这2个MTJ元件10。

各层中,MTJ元件10的固定层上,连接有起读出线功能的第1导电线11A。第1导电线11A沿X方向延伸,而且,共同连接到X方向配置的多个MTJ元件10的固定层。读出放大器(S/A)15连接到第1导电线11A的一端。

并且,各层中,起写入线和读出线功能的第2导电线12A连接到MTJ元件10的自由层。第2导电线12A沿X方向延伸,而且,共同连接到X方向配置的多个MTJ元件10的自由层。起选择晶体管功能的选择晶体管14连接到第2导电线12A的一端。

按照这样的第5实施例的单元构造,除获得与第1实施例同样的效果外,进而,也能获得有关上述「共用布线」的效果。

⑥第6实施例

图16表示本发明第6实施例的磁随机存取存储器的单元阵列部分。

第6实施例是把1列内存在的多层叠置的多个MTJ元件,集中连接到1个读出放大器上的例子。

在半导体衬底上边,把多个MTJ元件叠置成多层(本例中,为4层)。并且,各层中,MTJ元件10在X-Y平面内构成阵列。

写入线13配置在上下方向邻接的2个MTJ元件10之间,并沿Y方向延伸。而且,本例中,由上下方向邻接的2个MTJ元件共用写入线13。即,写入线13不是配置在全部层之间,而是例如,从半导体衬底一侧数起,配置于第奇数层的MTJ元件10的正上方和第偶数层的MTJ元件10的正下方。

并且,相对于写入线13,对称配置其上下存在的MTJ元件。即,MTJ元件10的两层磁性层中固定自旋方向的固定层(pin layer)配置于远离写入线13的位置,并且,能自由改变MTJ元件10的两层磁性层中自旋方向的自由层(freelayer)被配置在靠近写入线13的位置。写入线13位于距该上下存在的2个MTJ元件10等距离的位置,而且,离开这2个MTJ元件10。

各层中,MTJ元件10的固定层上,连接有起读出线功能的第1导电线11A。第1导电线11A沿X方向延伸,而且,共同连接到X方向配置的多个MTJ元件10的固定层。

本例中,把由X方向配置的多个MTJ元件组成的组规定为1列的场合,MTJ元件10的阵列1列内,将在各层配置的第1导电线11A的一端共同连接起来。共同连接的第1导电线11A连接到读出放大器(S/A)15。

并且,各层中,起写入线和读出线功能的第2导电线12A连接到MTJ元件10的自由层。第2导电线12A沿X方向延伸,而且,共同连接到X方向配置的多个MTJ元件10的自由层。

本例中,MTJ元件10的阵列11列内,对于各层中配置的第2导电线12A,也将其一端共同连接起来。第2导电线12A连接到起选择晶体管功能的选择晶体管14。

这样,第6实施例的单元构造中,共同连接第1导电线11A的一端,而且,将其连接点连到1个读出放大器(S/A)。并且,对第2导电线12A的一端也将其共同连接起来,并将该连接点连到选择晶体管14。

按照这种构成,也能获得与第1实施例同样的效果,例如,减少配置于存储单元阵列外围的晶体管数这样的效果。进而,本例中,也能获得有关上述「共用布线」的效果。

(4)其它

上述第1到第5实施例中,对多层叠置MTJ元件的阵列构造中,有关串联或并联连接配置于1行内各层的写入线(写入专用线)的场合进行说明,但是本发明的应用于除该写入线以外的MTJ元件阵列内配置的线。

例如,与第6实施例同样,也可以分别把本发明应用于图1的上部线11和下部线12,并且图2的上部线11和下部线12。

并且,第1到第4实施例中,虽然以配置于多层叠置的MTJ元件各层的线为例进行说明,但是例如,对于由上下MTJ元件共用线场合等,具有同样功能的线,不是配置于各层,而是每隔1层进行配置。

即使这样的场合,如第5实施例所示,也可以串联或并联连接每隔1层配置的线,构成本发明。

进而,在第1到第4实施例中,与MTJ元件阵列内的线连接的晶体管,一般是MOS晶体管,但也可以是双极晶体管或二极管。

只要是具有多层叠置MTJ元件的单元阵列构造的磁随机存取存储器,不管构造如何,本发明都可以应用。

(5)结束语

如以上说明的那样,按照本发明例的磁随机存取存储器,在多层叠置MTJ元件的阵列构造中,由于串联或并联连接各层中配置的具有同样功能的导线,该导线上,只要在其一端配置1个,或在其两端每端配置晶体管就行,可以减少配置于MTJ元件阵列端部的晶体管数。

并且,不管MTJ元件的叠置数,只要在MTJ元件阵列1行或1列内串联或并联连接的导线上连接晶体管就行。因此,即使增加MTJ元件的叠置数,谋求增大存储容量,既没有增大晶体管数,并且,也不会使其布局复杂化。

进而,因为连接到MTJ元件阵列1列内配置的导线的晶体管数是固定的,因此把MTJ元件阵列制成1个小块,集合多个块构成大的存储单元阵列也行。这时,可在MTJ元件阵列的正下方,配置晶体管或读出放大器等的核心电路。

3.三维布线

(1)背景技术

图17和图18表示本发明例的磁随机存取存储器的背景技术。

在半导体衬底上边,多层(本例中,为3层)叠置多个MTJ元件10。并且,各层中,在上部线11与下部线12之间并联连接多个MTJ元件10。

上部线11X方向延伸,其一端连接到选择晶体管14。下部线12也沿X方向延伸,其一端连接到读出放大器(S/A)15等外围电路。本例中,读出电流沿着上部线11、MTJ元件10、下部线12这样的路径,即沿X方向流动。写入线13邻接MTJ元件10配置,并沿Y方向延伸。

图19和图20表示对于图17和图18的单元构造,将下部线和写入线一体化的例子。

下部线12沿Y方向延伸,其一端连到读出放大器(S/A)。写入时,下部线12起到写入线的功能。读出时,下部线12起读出线功能。首先,读出电流流入上部线(X方向)11,而后,经由MTJ元件10流到下部线(Y方向)12。

磁随机存取存储器的单元基本构造是1个MTJ元件对应1个开关元件(选择晶体管)的1单元-1晶体管构造。但是,多层叠置MTJ元件的器件构造中,如果每1个MTJ元件对应1个开关元件的话,开关元件数将增加,不利于单元高密度化。

因而,多层叠置MTJ元件10的器件构造的场合,采用每1个MTJ元件不对应1个开关元件,也能进行读出动作或写入动作的这种器件构造。

例如,按图17到图20中所示的器件构造,在MTJ元件10的阵列各层中,把多个MTJ元件10连接到上部线11与下部线12之间。而且,例如,将选择晶体管14连到上部线11的一端,将读出放大器(S/A)15连到下部线12的一端。

但是,这时,图17和图18的例子中,在MTJ元件10的阵列各层,需要配置上部线(读出/写入线)11、下部线(读出线)12和写入线13的合计3条线。并且,图19和图20的例子中,MTJ元件10的阵列各层中,需要配置上部线(读出/写入线)11和下部线(读出/写入线)12的合计2条线。

而且,衬底上多层叠置的MTJ元件阵列内,配置这种写入线或读出线(电流总线)的场合,随着MTJ元件的叠置数增加,器件构造将复杂起来,发生以下这样的问题。

a.MTJ元件的特性受到其所配置的面(底膜)的平整度很大影响。该平整度因MTJ元件叠置数越多变得越恶化,所以随MTJ元件的叠置数增加,产生MTJ元件特性的恶化。

b.使用3条或其以上的线对MTJ元件进行数据写入/读出的场合(例如,图17和图18),1条读出线与1条写入线必须互相绝缘,而且,该条读出线必须接触MTJ元件。即,使1条写入线仅多离开MTJ元件1条读出线的厚度部分。

尽管,众所周知的事实是由读出线里流动电流发生的磁场强度与距离的二次方成反比。所以,正如上述那样,使用3条或其以上条线的场合,1条写入线与MTJ元件间的距离增大,其离散也将增加。即,由该条写入线里流动电流而施加于MTJ元件的磁场离散增加,对写入需要的磁场,必须确保充分的余量。

c.在MTJ元件阵列各层配置的导线各个端部,连接有晶体管。并且,这些导线在MTJ元件阵列上,沿X方向或Y方向延伸。因此,与这些导线连接的晶体管就应集中配置阵列端部区域(或阵列外围部分)(参照图6)

另一方面,至于对MTJ元件的数据写入/读出动作,大家都知道,起因于MTJ元件的特性,需要大电流。为此,连到这些导线的晶体管尺寸(或间距)必然要加大。

因此,MTJ元件的叠置数增加的话,与其成正比,1行或1列内需要设置的晶体管数增加,不可能在阵列的外围部分配置全部的晶体管,MTJ元件的间距又受晶体管的间距影响,不能提高MTJ元件的集成度。

(2)概要

本发明例(三维布线)是应用于具有多层叠置MTJ元件阵列构造的磁随机存取存储器。

本发明例的磁随机存取存储器的特征是,在MTJ元件阵列内三维配置用于数据写入/读出的多条线。

即,现有,全部使用于数据写入/读出的线都沿X方向或Y方向延伸。对此,本发明例的磁随机存取存储器中,设定多层叠置MTJ元件的方向为Z轴方向,在各层中MTJ元件都在X-Y轴方向构成阵列的场合,使用于数据写入/读出的多条导线中,至少1条沿Z方向延伸。

这样,通过三维配置使用于数据写入/读出的导线,可以减少X-Y轴方向延伸的导线数。Z方向延伸的导线,例如,可用接触工艺很容易形成。由以上,即使增加MTJ元件的叠置数,也能实现提高底膜平整度,提高MTJ元件特性。

并且,要是三维配置使用于数据写入/读出的导线,就会增加阵列内导线布局的自由度,例如,可在MTJ元件近旁配置2条写入线,能够抑制MTJ元件上所加磁场的离散。

进而,关于Z方向延伸的导线,其一端应该在MTJ元件阵列的正下方。因此,很容易在阵列的正下方形成连到该导线的晶体管,不必在阵列外围部分集中晶体管。(3)实施例

①第1实施例

图21表示本发明第1实施例的磁随机存取存储器的单元阵列部分的布局。

在半导体衬底上边,把多个MTJ元件10叠置成多层(本例中,为3层)。并且,各层中,MTJ元件10在X-Y平面内构成阵列。

上部线11起读出线功能,沿X方向延伸。上部线11,例如,接触MTJ元件10的自由层。下部线12起读出线和写入线功能,沿Y方向延伸。下部线12,例如,接触MTJ元件10的固定层。并且,例如,上部线11的一端,连接有选择晶体管,下部线12的一端,连接有读出放大器(S/A)。

写入线13沿Z轴方向延伸,并配置在Z轴方向叠置的多个MTJ元件10的近旁。向MTJ元件10写入的数据(自由层的磁化方向),通过由流入下部线12的沿Y轴方向流动的电流发生的磁场和由流入写入线13的沿Z轴方向流动的电流发生的磁场的合成磁场来决定。

写入线13的衬底侧一端,连接有选择晶体管(例如,MOS晶体管)14。该选择晶体管14配置在MTJ元件10的阵列正下方。

按照这种器件构造,在Z轴方向,延伸使用于数据写入/读出的多条导线之中的至少1条(本例中,为写入线13)。

例如,如果打算使用3条导线实行写入/读出的场合,以往,因为该3条导线全都是沿X轴方向或Y轴方向延伸,所以MTJ元件阵列的每1层,需要至少3此多层布线工艺。对此,本发明例中,关于Z轴方向延伸的导线,可用接触工艺形成,因而可以减少MTJ元件阵列每1层的多层布线工艺次数。

因此,即使增加MTJ元件的叠置数,也能实现提高底膜的平整度和提高MTJ元件的特性。

并且,要是三维配置数据写入/读出中所用的导线的话,阵列内线的布局自由度就增加。

例如,如果打算使用3条线实行写入/读出的场合,以往,就形成在写入专用的导线与MTJ元件之间配置读出线的构造,写入专用导线与MTJ元件的距离加大了。对此,本发明例中,例如,采用在Z轴方向延伸写入专用导线的办法,可在MTJ元件近旁配置该写入专用导线,能够抑制加到MTJ元件上的磁场离散。

进而,关于沿Z轴方向延伸的写入线,其一端应该存在于MTJ元件阵列的下方。所以,很容易在阵列正下方形成连到该导线的晶体管,能够缓和在阵列外围部分密集晶体管。

另外,本实施例中,MTJ元件阵列内配置三种类型的导线,各导线互相垂直,而且,制成互相沿不同的方向延伸这样的器件构造。这样,就可以在衬底上边分散配置与各导线连接的晶体管。

但是,本发明中,Z方向延伸的导线至少有1条就足够,此外的导线多条存在的场合,至于这些导线,无论沿同一方向延伸,或,无论沿不同的方向延伸,也都无妨。

②第2实施例

上述第1实施例中,表示MTJ元件阵列内配置了三种类型导线的场合,然而本发明也可以应用于MTJ元件阵列内,只配置具有起读出/写入线功能的两种导线的场合。

图22表示本发明第2实施例的磁随机存取存储器的单元阵列部分的布局。

在半导体衬底上边,把多个MTJ元件10叠置成多层(本例中,为3层)。并且,各层中,MTJ元件10在X-Y平面内构成阵列。

MTJ元件10上边,形成导电图形11C。用作写入线和读出线(电流总线)功能的导线13沿Z轴方向延伸,并配置在Z轴方向叠置的多个MTJ元件10近旁。并且,写入线13,连接到Z轴方向叠置的多个MTJ元件10的导电图形11C。

导线13的衬底侧一端,连接选择晶体管(例如,MOS晶体管)14。该选择晶体管14配置在MTJ元件10的阵列正下方。

下部线12用作写入线和读出线(电流总线)功能,沿Y方向延伸。下部线12,例如,与MTJ元件10的固定层接触。并且,例如,下部线12的一端,连接读出放大器(S/A)。

由MTJ元件10写入的数据(自由层的磁化方向)通过由随流入下部线12沿Y轴方向流动的电流发生的磁场和随流入写入线13里沿Z轴方向流动的电流发生的磁场的合成磁场来决定。

按照这种器件构造,沿Z轴方向延伸使用于数据写入/读出的多条导线之中至少1条(本例中,导线13)。关于Z轴方向延伸的导线,可用接触工艺形成,因而可以减少MTJ元件阵列每1层的多层布线工艺次数。

本实施例中,MTJ元件阵列的各层中,沿X方向或Y方向延伸的导线只有1条,所以与上述第1实施例比较,进而可以实现提高底膜的平整度,提高MTJ元件的特性。

并且,采用三维配置数据写入/读出中所用导线的办法,增加阵列内导线布局的自由度,并且,能够抑制给与MTJ元件的磁场的离散。

进而,关于Z轴方向延伸的写入线,其一端配置在MTJ元件阵列的正下方。即,通过将与该导线连接的晶体管配置在MTJ元件阵列的正下方,可以缓和阵列外围部分的晶体管密集。

③第3实施例

本实施例是上述第1实施例的磁随机存取存储器的变形例。

上述第1实施例中,MTJ元件阵列的1个层内,虽然对1个MTJ元件对应1条写入线,但是本实施例中,在MTJ元件阵列的1个层内,对X方向邻接的2个MTJ元件对应1条写入线。即,在MTJ元件阵列的层内,1条写入线夹入2个MTJ元件中间。

由于形成这样的构成,可将Z轴方向延伸的写入线条数减少到上述第1实施例中需要条数的一半,正因此,能够实现MTJ元件的高密度。

图23表示本发明第3实施例的磁随机存取存储器的单元阵列部分的布局。

在半导体衬底上边,把多个MTJ10元件叠置成多层(本例中,为3层)。并且,各层中,MTJ元件10在X-Y平面内构成阵列。

上部线11起读出线功能,沿X方向延伸。上部线11,例如与MTJ元件10的自由层接触。下部线12起读出线和写入线功能,沿Y方向延伸。下部线12,例如接触MTJ元件10的固定层。并且,例如,上部线11的一端,连接选择晶体管,下部线12的一端连接读出放大器(S/A)。

写入线13沿Z轴方向延伸,配置在Z轴方向叠置的多个MTJ元件10近旁。

进而,本实施例中,在MTJ元件10的阵列1层内,对X方向邻接的2个MTJ元件对应1条写入线13。即,在MTJ元件阵列的层内,将1条写入线13夹入2个MTJ元件中间。

通过形成这样的构成,可减少Z轴方向延伸的写入线13的条数,正因此,能够实现MTJ元件的高密度。

导线13的衬底侧一端,连接选择晶体管(例如,MOS晶体管)14。该选择晶体管14配置在MTJ元件10的阵列正下方。

向MTJ元件10写入的数据(自由层的磁化方向)通过由流入下部线12沿Y轴方向流动的电流发生的磁场和由流入写入线13里沿Z轴方向流动的电流发生的磁场的合成磁场来决定。

这里,本实施例中,在写入线13向着一方向流动电流的场合,如图26所示,MTJ元件10的阵列1层内,给予存在于写入线13左侧MTJ元件的磁场方向a1与给与存在于写入线13右侧MTJ元件的磁场方向a2成为互相相反。

于是,对同一写入的动作,存在于写入线13左右的2个MTJ元件磁化状态变成互相不同。

即,这时,假如存入2个MTJ元件的数据是相同的,就需要使读出存入写入线13左侧MTJ元件的数据时的判定“1”/“0”的条件和读出存入写入线13右侧MTJ元件的数据时的判定“1”/“0”的条件互相相反。

按照这种器件构造,沿Z轴方向延伸使用于数据写入/读出的多条导线之中的至少1条(本例中,写入线13)。即,关于沿Z轴方向延伸的导线,因为可用接触工艺形成,所以能够减少MTJ元件阵列每1层的的多层布线工艺次数。

因此,即使增加MTJ元件的叠置数,也能实现提高底膜的平整度和提高MTJ元件的特性。

并且,采用三维配置数据写入/读出中所用导线的办法,增加阵列内导线布局的自由度。并且,例如,采用沿Z轴方向延伸写入专用导线的办法,可在MTJ元件近旁配置该写入专用的导线,能够抑制给与MTJ元件的磁场的离散。

进而,关于Z轴方向延伸的写入线,其一端配置在MTJ元件阵列的正下方。于是,很容易在阵列的正下方配置与该导线连接的晶体管,可以缓和阵列外围部分晶体管密集。

并且,本实施例中,MTJ元件阵列的1个层内,对X方向邻接的2个MTJ元件对应1条写入线。即,在MTJ元件阵列的1个层内,将1条写入线夹入2个MTJ元件中间。通过形成这样的构成,可以减少沿Z轴方向延伸的写入线条数,正因此,才能够实现高密度MTJ元件。

另外,本实施例中,MTJ元件阵列内配置三种类型的导线,各导线互相垂直,而且,形成互相沿不同的方向延伸这样的器件构造。这就是在衬底上分散配置与各导线连接的晶体管的原因。

但是,本发明中,Z方向延伸的导线至少有1条就足够,此外的导线存在多条的场合,至于这些导线,无论沿相同方向延伸,或,无论沿不同的方向延伸也都无妨。

④第4实施例

上述第3实施例中,表示MTJ元件阵列内配置了三种类型导线的场合。本实施例中,说明有关MTJ元件的阵列内只配置具有起读出/写入线功能的两种类型导线的磁随机存取存储器。

图24表示本发明第4实施例的磁随机存取存储器的单元阵列部分的布局。

在半导体衬底上边,把多个MTJ元件10叠置成多层(本例中,为了简单,只示出1层)。并且,各层中,MTJ元件10在X-Y平面内构成阵列。

MTJ元件10上,形成导电图形11C。用作写入线和读出线(电流总线)功能的导线13沿Z轴方向延伸,并配置在Z轴方向叠置的多个MTJ元件10近旁。并且,写入线13连到Z轴方向叠置的多个MTJ元件10的导电图形11C。

进而,本实施例中,MTJ元件10的阵列1个层内,对X方向邻接的2个MTJ元件对应1条写入线13。即,在MTJ元件阵列的1个层内,将条写入线13夹入2个MTJ元件中间。

通过形成这样的构成,可以减少沿Z轴方向延伸的写入线13条数,正因此,才能实现高密度MTJ元件。

导线13的衬底侧一端,连接选择晶体管(例如,MOS晶体管)14。该选择晶体管14配置在MTJ元件10的阵列正下方。

下部线12起写入线和读出线(电流总线)功能,沿Y方向延伸。下部线12,例如接触MTJ元件10的固定层。并且,例如,下部线12的一端连接读出放大器(S/A)。

向MTJ元件10写入的数据(自由层的磁化方向)通过由流入下部线12沿Y轴方向流动的电流发生的磁场和由流入写入线13里沿Z轴方向流动的电流发生的磁场的合成磁场来决定。

按照这种器件构造,沿Z轴方向延伸使用于数据写入/读出的多条导线之中至少1条(本例中,导线13)。关于Z轴方向延伸的导线,可用接触工艺形成,因而可以减少MTJ元件阵列每1层的多层布线工艺次数。

本实施例中,MTJ元件阵列的各层中,沿X方向或Y方向延伸的导线只有1条,所以与上述第3实施例比较,进而,可以实现提高底膜的平整度,提高MTJ元件的特性。

并且,采用三维配置数据写入/读出中所用导线的办法,增加阵列内导线布局的自由度,并且,能够抑制给与MTJ元件的磁场的离散。

进而,关于Z轴方向延伸的写入线,其一端配置在MTJ元件阵列的正下方。即,应该将与该导线连接的晶体管配置在MTJ元件阵列的正下方,可以缓和在阵列外围部分晶体管密集。

并且,本实施例中,MTJ元件阵列的1个层内,对X方向邻接的2个MTJ元件对应1条写入线。即,在MTJ元件阵列的1个层内,将1条写入线夹入2个MTJ元件中间。通过形成这样的构成,可以减少沿Z轴方向延伸的写入线条数,正因此,才能够实现高密度MTJ元件。

⑤第5实施例

上述第1到第4实施例中,说明有关沿Z轴方向延伸写入专用导线,或作为读出/写入线功能导线的场合。但是,本发明的特征是,在沿Z轴方向延伸配置于MTJ元件阵列内的多种导线至少1条。

因而,本实施例中,说明有关沿Z轴方向延伸读出专用导线场合的例子。

图25表示本发明第5实施例的磁随机存取存储器的单元阵列部分的布局。

在半导体衬底上边,将多个MTJ元件10叠置成多层(本例中,为了简单,只示出1层)。并且,各层中,MTJ元件10在X-Y平面内构成阵列。

MTJ元件10上边,形成导电图形11C。读出专用线(电流总线)11沿Z轴方向延伸,并配置在Z轴方向叠置的多个MTJ元件10近旁。并且,读出专用线1共同连到Z轴方向叠置的多个MTJ元件10的导电图形11C。

进而,本实施例中,MTJ元件10的阵列1个层内,对X方向邻接的2个MTJ元件对应1条读出专用线11。即,在MTJ元件阵列的1个层内,将读出专用线1夹入2个MTJ元件中间。

通过形成这样的构成,可以减少沿Z轴方向延伸的读出专用线条数,正因此,才能实现高密度MTJ元件。

读出专用线1的衬底侧一端,连接有选择晶体管(例如,MOS晶体管)14。该选择晶体管14被配置在MTJ元件10的阵列的正下方。

MTJ元件10的上方,配置着与MTJ元件10接近、而不与之接触的写入专用线13。写入专用线13沿X方向延伸。写入专用线13的一端或两端上,连接选择晶体管。

下部线12起读出线和写入线功能,沿Y方向延伸。下部线12,例如接触MTJ元件10的固定层。并且,下部线12的一端,连接读出放大器(S/A)。

向MTJ元件10写入的数据(自由层的磁化方向)通过由流入下部线12里沿Y轴方向流动的电流发生的磁场和由流入写入线13里沿Z轴方向流动的电流发生的磁场的合成磁场来决定。

按照这种器件构造,沿Z轴方向延伸使用于数据写入/读出的多条导线之中至少1条(本例中,读出专用线11)。即,关于Z轴方向延伸的线,可用接触工艺形成,因而可以减少MTJ元件阵列每1层的多层布线工艺次数。

因此,即使增加MTJ元件的叠置数,也能实现提高底膜的平整度,提高MTJ元件的特性。

并且,采用三维配置数据写入/读出中所用导线的办法,能够增加阵列内导线布局的自由度。并且,例如,采用沿Z轴方向延伸读出专用导线的办法,可以在MTJ元件的正上方或近旁配置沿X方向延伸的专用导线,能够抑制给与MTJ元件的磁场的离散。

进而,关于Z轴方向延伸的专用线,其一端就存在MTJ元件阵列的正下方。于是,很容易在阵列的正下方,形成与该导线连接的晶体管,可以缓和在阵列外围部分晶体管密集。

并且,本实施例中,MTJ元件阵列的1个层内,对X方向邻接的2个MTJ元件对应1条写入线。即,在MTJ元件阵列的1个层内,将1条专用线夹入2个MTJ元件中间。通过形成这样的构成,可以减少沿Z轴方向延伸的专用线条数,正因此,才能够实现高密度MTJ元件。

⑥第6实施例

图27表示本发明第6实施例的磁随机存取存储器的单元阵列部分的布局。

在半导体衬底上边,将多个MTJ元件10叠置成多层(本例中,为3层)。并且,各层中,MTJ元件10在X-Y平面内构成阵列。

上部线11起读出线功能,沿X方向延伸。上部线11,例如,与MTJ元件10的自由层接触。下部线12起读出线和写入线功能,沿Y方向延伸。下部线12,例如,接触MTJ元件10的固定层。并且,例如,上部线11的一端,连接选择晶体管,下部线12的一端连接读出放大器(S/A)。

写入线13沿Z轴方向延伸,配置在Z轴方向叠置的多个MTJ元件10近旁。向MTJ元件10写入的数据(自由层的磁化方向)通过由流入下部线12里沿Y轴方向流动的电流发生的磁场和由流入写入线13里沿Z轴方向流动的电流发生的磁场的合成磁场来决定。

至少2条写入线13互相串联连接起来。串联连接的写入线13一端或另一端上,分别连接选择晶体管14(例如,MOS晶体管)。该选择晶体管14被配置在MTJ元件10的阵列的正下方。

即使这种器件构造,数据的写入/读出中所用的多条导线中,至少1条(本例中,写入线13)沿Z轴方向延伸。因此,也能获得与第1实施例同样的效果,例如,即使增加MTJ元件的叠置数,也能实现提高底膜的平整度,提高MTJ元件特性的这种效果。

⑦第7实施例

上述第1到第6实施例中,沿Z轴方向延伸的导线,可用接触工艺来形成。但是,如果MTJ元件的叠置数非常多的话,就难以用1次蚀刻工序形成接触孔。

因而,本实施例中,提出一种不仅一次形成沿Z轴方向延伸的导线,而且分成多次形成导线的技术。

图28中,关于多层叠置MTJ元件的阵列构造,提出在每1层形成MTJ元件和沿X方向和Y方向延伸的导线,同时也形成沿Z轴方向延伸的导线。这时,沿Z轴方向延伸的导线,由多个部分1-1、1-2、1-3、1-4的集合构成。

图29的例子是改进图28的例子。

图28的例子中,沿Z轴方向延伸的导线各部分1-1、1-2、1-3、1-4中发生对准偏移的场合,发生断线、线电阻增大等问题。因而,在图29例子中,关于多层叠置的MTJ元件的阵列构造,在每1层形成沿Z轴方向延伸的导线,同时考虑其上对准的偏移,形成中间层2-1、2-2、2-3。因此,即使在沿Z轴方向延伸的导线各部分1-1、1-2、1-3、1-4中发生对准偏移,也不会发生断线、线电阻增大等问题。

(4)其它

上述第1到第6实施例中,与MTJ元件阵列内的线连接的晶体管,一般的是MOS晶体管,但也可以是双极晶体管、二极管等。

本发明只要是具有多层叠置MTJ元件的单元阵列构造的磁随机存取存储器,不管构造也能应用。

(5)结束语

以上,如说明的那样,按照本发明例的磁随机存取存储器,在纵向(MTJ元件叠置的方向),使MTJ元件阵列内配置的多种线之中的至少1条线延伸。

其结果,可以减少横向延伸的线数,就能防止底膜平整度的恶化,抑制MTJ元件特性恶化。并且,提高阵列内的布局自由度,缩小给与MTJ元件的磁场的离散。进而,因为现在已经可以在阵列下方配置晶体管,所以能够缓和在阵列外围分晶体管密集。

其它的优点和改进对本领域普通技术人员是显而易见的。因此,本发明概括起来说,并不限于这里表示和描述的具体细节和表现的各实施例。所以,在不脱离由附属权利要求书及其等同物所限定的本发明总构思的精神或范围的前提下,可以作各种各样的修改。

Claims (67)

1.一种磁随机存取存储器,包括:

由固定自旋方向的第1磁性层、存储数据的第2磁性层、和夹入该第1与第2磁性层之间的绝缘层构成的第1和第2MTJ元件;以及

配置于该第1和第2MTJ元件之间,产生作用于该第1和第2MTJ元件的磁场的第1写入线,

其特征在于:

构成该第1MTJ元件的第1磁性层、绝缘层和第2磁性层,与构成该第2MTJ元件的第1磁性层、绝缘层和第2磁性层的位置关系为,相对于该第1写入线对称。

2.根据权利要求1所述的磁随机存取存储器,其特征在于:

第1和第2MTJ元件是在半导体衬底上叠置起来的。

3.根据权利要求1所述的磁随机存取存储器,其特征在于:

从第1写入线到第1MTJ元件的距离与从第1写入线到第2MTJ元件的距离实质上是相等的。

4.根据权利要求1所述的磁随机存取存储器,其特征在于:

第2磁性层配置在比第1磁性层更靠近第1写入线的位置。

5.根据权利要求4所述的磁随机存取存储器,还包括:

与第1写入线交叉,与第1MTJ元件的第1磁性层接触,且产生作用于第1MTJ元件的磁场的第2写入线,且第1写入线与第1和第2MTJ元件是分离的。

6.根据权利要求5所述的磁随机存取存储器,还包括:

与第1MTJ元件的第2磁性层连接,用于从第1MTJ元件读出数据的第1读出线,且

第2写入线还具有用于从该第1MTJ元件读出该数据的第2读出线功能。

7.根据权利要求4所述的磁随机存取存储器,还包括:

与第1写入线交叉,与第2MTJ元件的第1磁性层接触,且产生作用于第2MTJ元件的磁场的第2写入线,且第1写入线与第1和第2MTJ元件是分离的。

8.根据权利要求7所述的磁随机存取存储器,还包括:

与第2MTJ元件的第2磁性层连接,用于从第2MTJ元件读出数据的第1读出线,且

第2写入线还具有用于从第2MTJ元件读出数据的第2读出线功能。

9.根据权利要求4所述的磁随机存取存储器,还包括:

与第1写入线交叉,与第1MTJ元件的与第1磁性层接触,且产生作用于第1MTJ元件的磁场的第2写入线,且第1写入线与第1和第2MTJ元件的第2磁性层接触。

10.根据权利要求9所述的磁随机存取存储器,其特征在于:

第1写入线还具有用于从该第1MTJ元件读出数据的第1读出线功能,第2写入线还具有用于从第1MTJ元件读出数据的第2读出线功能。

11.根据权利要求4所述的磁随机存取存储器,还包括:

与第1写入线交叉,与第2MTJ元件的第1磁性层接触,且产生作用于第2MTJ元件的磁场的第2写入线,且第1写入线接触第1和第2MTJ元件的第2磁性层。

12.根据权利要求11所述的磁随机存取存储器,其特征在于:

第1写入线还具有用于从第2MTJ元件读出数据的第1读出线功能,第2写入线还具有用于从第2MTJ元件读出数据的第2读出线功能。

13.根据权利要求1所述的磁随机存取存储器,其特征在于:

第1磁性层配置在比第2磁性层更靠近第1写入线的位置。

14.根据权利要求13所述的磁随机存取存储器,还包括:

与第1写入线交叉,与第1MTJ元件的第2磁性层接触,且产生作用于第1MTJ元件的磁场的第2写入线,且第1写入线与第1和第2MTJ元件是分离的。

15.根据权利要求14所述的磁随机存取存储器,还包括:

与第1和第2MTJ元件的第1磁性层连接,用于从第1MTJ元件读出数据的第1读出线,且

第2写入线还具有用于从第1MTJ元件读出数据的第2读出线功能。

16.根据权利要求13所述的磁随机存取存储器,还包括:

与第1写入线交叉,与第2MTJ元件的第2磁性层接触,且产生作用于第1MTJ元件的磁场的第2写入线,且

第1写入线与第1和第2MTJ元件是分离的。

17.根据权利要求16所述的磁随机存取存储器,还包括:

与第2MTJ元件的第1磁性层接触,用于从第2MTJ元件读出数据的第1读出线,且

第2写入线还具有用于从第2MTJ元件读出数据的第2读出线功能。

18.根据权利要求13所述的磁随机存取存储器,还包括:

与第1写入线交叉,与第1MTJ元件的第2磁性层接触,且产生作用于第1MTJ元件的磁场的第2写入线,且第1写入线与第1和第2MTJ元件的第1磁性层接触。

19.根据权利要求18所述的磁随机存取存储器,其特征在于:

第1写入线还具有用于从第1MTJ元件读出数据的第1读出线功能,第2写入线还具有用于从第1MTJ元件读出该数据的第2读出线功能。

20.根据权利要求13所述的磁随机存取存储器,还包括:

与第1写入线交叉,与第2MTJ元件的第2磁性层接触,且产生作用于第2MTJ元件的磁场的第2写入线,且第1写入线与第1和第2MTJ元件的第1磁性层接触。

21.根据权利要求20所述的磁随机存取存储器,其特征在于:

第1写入线还具有用于从第2MTJ元件读出数据的第1读出线功能,第2写入线还具有用于从第2MTJ元件读出该数据的第2读出线功能。

22.一种磁随机存取存储器,包括:

由固定自旋方向的第1磁性层、存储数据的第2磁性层、和夹入该第1与第2磁性层之间的绝缘层构成的第1和第2MTJ元件;

配置于该第1和第2MTJ元件之间,产生作用于该第1和第2MTJ元件的磁场的第1写入线;以及

配置于该第2和第3MTJ元件之间,产生作用于该第2和第3MTJ元件的磁场的第2写入线;

其特征在于:

构成该第1MTJ元件的第1磁性层、绝缘层和第2磁性层,与构成该第2MTJ元件的第1磁性层、绝缘层和第2磁性层的位置关系为相对于第1写入线对称,而且

构成该第2MTJ元件的第1磁性层、绝缘层和第2磁性层,与构成该第3MTJ元件的第1磁性层、绝缘层和第2磁性层的位置关系为相对于第2写入线对称。

23.根据权利要求22所述的磁随机存取存储器,其特征在于:

第1、第2和第3MTJ元件是在半导体衬底上叠置起来的。

24.根据权利要求22所述的磁随机存取存储器,其特征在于:

第1写入线与第1和第2MTJ元件的第1磁性层接触,第2写入线与第2和第3MTJ元件的第2磁性层接触,第1和第2写入线互相交叉。

25.根据权利要求22所述的磁随机存取存储器,其特征在于:

第1写入线与第1和第2MTJ元件的第2磁性层接触,第2写入线与第2和第3MTJ元件的第1磁性层接触,第1和第2写入线互相交叉。

26.一种磁随机存取存储器,包括:

具有叠置成多层的多个MTJ元件的阵列;

配置于该阵列内的第1导电线;以及

配置在该阵列内,具有与该第1导电线同样功能,且配置于该第1导电线上边的第2导电线,

其特征在于:该第1和第2导电线是串联连接的。

27.根据权利要求26所述的磁随机存取存储器,其特征在于:

第1和第2导电线是在阵列的端部互相连接的。

28.根据权利要求26所述的磁随机存取存储器,其特征在于:

第1和第2导电线整体上蛇形配置在阵列内。

29.根据权利要求26所述的磁随机存取存储器,其特征在于:

第1和第2导电线用于写入动作或读出动作。

30.根据权利要求26所述的磁随机存取存储器,其特征在于:

第1和第2导电线沿同一方向延伸。

31.根据权利要求26所述的磁随机存取存储器,还包括:

配置在阵列端部,连接到第1和第2导电线的接触塞;以及

连接到接触塞的晶体管。

32.根据权利要求31所述的磁随机存取存储器,其特征在于:

晶体管配置在阵列的正下方。

33.根据权利要求26所述的磁随机存取存储器,其特征在于:

由第1和第2导电线构成的线的一端和另一端,一起位于阵列的一端部。

34.根据权利要求26所述的磁随机存取存储器,其特征在于:

由第1和第2导电线构成的线的一端位于阵列的一端部,由该第1和第2导电线构成的线的另一端位于阵列的另一端部。

35.根据权利要求26所述的磁随机存取存储器,其特征在于:

多个MTJ元件中,相同层内配置的MTJ元件固定层的磁化方向是相同的。

36.根据权利要求26所述的磁随机存取存储器,其特征在于:

多个MTJ元件中,不同层内配置的MTJ元件固定层的磁化方向是相同的。

37.根据权利要求26所述的磁随机存取存储器,其特征在于:

多个MTJ元件中,不同层内配置的MTJ元件固定层的磁化方向是不同的。

38.根据权利要求37所述的磁随机存取存储器,其特征在于:

多个MTJ元件固定层的磁化方向,每1层都是不同的。

39.根据权利要求26所述的磁随机存取存储器,其特征在于:

阵列具有叠置的第1、第2、第3和第4MTJ元件,第1导电线配置在该第1与第2MTJ元件之间,第2导电线配置在该第3与第4MTJ元件之间。

40.一种磁随机存取存储器,包括:

具有叠置成多层的多个MTJ元件的阵列;

配置在阵列内的第1导电线;以及

配置在阵列内,具有与该第1导电线同样功能,且配置于第1导电线上边的第2导电线,

其特征在于:该第1和第2导电线是并联连接的。

41.根据权利要求40所述的磁随机存取存储器,其特征在于:

第1和第2导电线是在阵列的端部互相连接的。

42.根据权利要求40所述的磁随机存取存储器,其特征在于:

第1和第2导电线整体上具有梯子形状。

43.根据权利要求40所述的磁随机存取存储器,其特征在于:

第1和第2导电线用于写入动作或读出动作。

44.根据权利要求40所述的磁随机存取存储器,其特征在于:

第1和第2导电线沿同一方向延伸。

45.根据权利要求40所述的磁随机存取存储器,还包括:

配置在阵列端部,连接到第1和第2导电线的接触塞;以及

连接到接触塞的晶体管。

46.根据权利要求45所述的磁随机存取存储器,其特征在于:

晶体管配置在阵列的正下方。

47.根据权利要求40所述的磁随机存取存储器,其特征在于:

由第1和第2导电线构成的线的一端和另一端,一起位于阵列的一端部。

48.根据权利要求40所述的磁随机存取存储器,其特征在于:

由第1和第2导电线构成的线的一端位于阵列的一端部,由第1和第2导电线构成的线的另一端位于阵列的另一端部。

49.根据权利要求40所述的磁随机存取存储器,其特征在于:

多个MTJ元件固定层的磁化方向全部是相同的。

50.根据权利要求40所述的磁随机存取存储器,其特征在于:

阵列具有叠置的第1、第2、第3和第4MTJ元件,第1导电线配置在第1与第2MTJ元件之间,第2导电线配置在第3与第4MTJ元件之间。

51.根据权利要求40所述的磁随机存取存储器,还包括:

具有叠置成多层的多个MTJ元件的阵列;以及

沿上述多个MTJ元件叠置的方向延伸,在写入时产生磁场的第1写入线。

52.根据权利要求51所述的磁随机存取存储器,其特征在于:

第1写入线与多个MTJ元件是分离的。

53.根据权利要求51所述的磁随机存取存储器,其特征在于:

第1写入线是由多个MTJ元件共用的。

54.根据权利要求51所述的磁随机存取存储器,还包括:

与第1写入线交叉,在写入时产生磁场的第2写入线。

55.根据权利要求54所述的磁随机存取存储器,还包括:

与第1和第2写入线交叉的导电线。

56.根据权利要求51所述的磁随机存取存储器,其特征在于:

第1写入线连接到配置于该阵列正下方的开关元件上。

57.根据权利要求56所述的磁随机存取存储器,其特征在于:

开关元件是MOS晶体管。

58.根据权利要求51所述的磁随机存取存储器,其特征在于:

第1写入线是由叠置的多个接触塞构成的。

59.一种磁随机存取存储器,包括:

具有叠置成多层的多个MTJ元件的阵列;以及

沿上述多个MTJ元件叠置的方向延伸,且在读出时产生读出电流的第1写入线。

60.根据权利要求59所述的磁随机存取存储器,其特征在于:

第1写入线与多个MTJ元件相连接。

61.根据权利要求59所述的磁随机存取存储器,其特征在于:

第1写入线是由多个MTJ元件共用的。

62.根据权利要求59所述的磁随机存取存储器,还包括:

与第1写入线交叉,在读出时用来流动读出电流的第2写入线。

63.根据权利要求62所述的磁随机存取存储器,还包括:

与第1和第2写入线交叉的导电线。

64.根据权利要求59所述的磁随机存取存储器,其特征在于:

第1读出线连接到配置于该阵列正下方的开关元件上。

65.根据权利要求64所述的磁随机存取存储器,其特征在于:

开关元件是MOS晶体管。

66.根据权利要求59所述的磁随机存取存储器,其特征在于:

第1读出线是由叠置的多个接触塞构成。

67.根据权利要求59所述的磁随机存取存储器,其特征在于:

第1读出线还具有写入线功能。

Applications Claiming Priority (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP367754/2001 | 2001-11-30 | ||

| JP2001367755A JP4068337B2 (ja) | 2001-11-30 | 2001-11-30 | 磁気ランダムアクセスメモリ |

| JP2001367941A JP4091298B2 (ja) | 2001-11-30 | 2001-11-30 | 磁気ランダムアクセスメモリ |

| JP367755/2001 | 2001-11-30 | ||

| JP367941/2001 | 2001-11-30 | ||

| JP2001367754A JP2003168785A (ja) | 2001-11-30 | 2001-11-30 | 磁気ランダムアクセスメモリ |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN 200510118783 Division CN1783337B (zh) | 2001-11-30 | 2002-11-29 | 磁随机存取存储器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1431663A true CN1431663A (zh) | 2003-07-23 |

| CN100358047C CN100358047C (zh) | 2007-12-26 |

Family

ID=27347895

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB021518491A Expired - Fee Related CN100358047C (zh) | 2001-11-30 | 2002-11-29 | 磁随机存取存储器 |

Country Status (4)

| Country | Link |

|---|---|

| US (3) | US6807086B2 (zh) |

| KR (1) | KR100537116B1 (zh) |

| CN (1) | CN100358047C (zh) |

| TW (1) | TW582032B (zh) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN100452233C (zh) * | 2005-01-28 | 2009-01-14 | 株式会社东芝 | 自旋注入磁随机存取存储器及写入方法 |

| CN110910924A (zh) * | 2018-09-18 | 2020-03-24 | 联华电子股份有限公司 | 磁阻式随机存取存储器 |

Families Citing this family (28)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3906067B2 (ja) * | 2001-11-30 | 2007-04-18 | 株式会社東芝 | 磁気ランダムアクセスメモリ |

| US7042749B2 (en) * | 2002-05-16 | 2006-05-09 | Micron Technology, Inc. | Stacked 1T-nmemory cell structure |

| US6940748B2 (en) * | 2002-05-16 | 2005-09-06 | Micron Technology, Inc. | Stacked 1T-nMTJ MRAM structure |

| AU2003243244A1 (en) * | 2002-05-16 | 2003-12-02 | Micron Technology, Inc. | STACKED 1T-nMEMORY CELL STRUCTURE |

| JP4646485B2 (ja) * | 2002-06-25 | 2011-03-09 | ルネサスエレクトロニクス株式会社 | 薄膜磁性体記憶装置 |

| US6925003B2 (en) * | 2003-09-08 | 2005-08-02 | Hewlett-Packard Development Company, L.P. | Magnetic memory cell structure |

| US6847544B1 (en) * | 2003-10-20 | 2005-01-25 | Hewlett-Packard Development Company, L.P. | Magnetic memory which detects changes between first and second resistive states of memory cell |

| US7102921B2 (en) * | 2004-05-11 | 2006-09-05 | Hewlett-Packard Development Company, L.P. | Magnetic memory device |

| US7061037B2 (en) * | 2004-07-06 | 2006-06-13 | Maglabs, Inc. | Magnetic random access memory with multiple memory layers and improved memory cell selectivity |

| JP2006344281A (ja) * | 2005-06-08 | 2006-12-21 | Toshiba Corp | 磁気ランダムアクセスメモリ |

| CN101340831A (zh) * | 2005-10-21 | 2009-01-07 | 纳塔利娅·奥德尼斯·哈格 | 可拆开的鞋 |

| US7426133B2 (en) * | 2005-10-24 | 2008-09-16 | Honeywell International, Inc. | Complementary giant magneto-resistive memory with full-turn word line |

| US8120949B2 (en) * | 2006-04-27 | 2012-02-21 | Avalanche Technology, Inc. | Low-cost non-volatile flash-RAM memory |

| US7983065B2 (en) * | 2009-04-08 | 2011-07-19 | Sandisk 3D Llc | Three-dimensional array of re-programmable non-volatile memory elements having vertical bit lines |

| US8199576B2 (en) * | 2009-04-08 | 2012-06-12 | Sandisk 3D Llc | Three-dimensional array of re-programmable non-volatile memory elements having vertical bit lines and a double-global-bit-line architecture |

| US8351236B2 (en) | 2009-04-08 | 2013-01-08 | Sandisk 3D Llc | Three-dimensional array of re-programmable non-volatile memory elements having vertical bit lines and a single-sided word line architecture |

| WO2010117912A1 (en) * | 2009-04-08 | 2010-10-14 | Sandisk 3D Llc | Three-dimensional array of re-programmable non-volatile memory elements having vertical bit lines and a double-global-bit-line architecture |

| US8526237B2 (en) | 2010-06-08 | 2013-09-03 | Sandisk 3D Llc | Non-volatile memory having 3D array of read/write elements and read/write circuits and method thereof |

| US8547720B2 (en) | 2010-06-08 | 2013-10-01 | Sandisk 3D Llc | Non-volatile memory having 3D array of read/write elements with efficient decoding of vertical bit lines and word lines |

| JP5686698B2 (ja) * | 2011-08-05 | 2015-03-18 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP2013041912A (ja) * | 2011-08-12 | 2013-02-28 | Toshiba Corp | 磁気ランダムアクセスメモリ |

| CN104081463B (zh) * | 2011-12-22 | 2017-06-13 | 英特尔公司 | 带有具有两个堆叠的磁性隧道结(mtj)部件的元件的存储器 |

| EP2688103A1 (en) * | 2012-07-20 | 2014-01-22 | Crocus Technology S.A. | MRAM cell and device with improved field line for reduced power consumption |

| US9299917B2 (en) * | 2013-09-30 | 2016-03-29 | Northwestern University | Magnetic tunnel junctions with control wire |

| KR102477093B1 (ko) | 2015-10-13 | 2022-12-13 | 삼성전자주식회사 | 푸리에 변환을 수행하는 방법 및 장치 |

| JP6477752B2 (ja) * | 2017-03-13 | 2019-03-06 | Tdk株式会社 | 磁気センサ |

| US10262715B2 (en) | 2017-03-27 | 2019-04-16 | Micron Technology, Inc. | Multiple plate line architecture for multideck memory array |

| KR20210140960A (ko) | 2020-05-14 | 2021-11-23 | 삼성전자주식회사 | 메모리 소자 및 그 제조 방법 |

Family Cites Families (35)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4791604A (en) * | 1984-02-15 | 1988-12-13 | Joseph J. Bednarz | Sheet random access memory |

| US6590750B2 (en) * | 1996-03-18 | 2003-07-08 | International Business Machines Corporation | Limiting magnetoresistive electrical interaction to a preferred portion of a magnetic region in magnetic devices |

| JP3392657B2 (ja) | 1996-09-26 | 2003-03-31 | 株式会社東芝 | 半導体記憶装置 |

| JP3132437B2 (ja) * | 1997-09-26 | 2001-02-05 | 日本電気株式会社 | 半導体記憶装置 |

| US5991193A (en) * | 1997-12-02 | 1999-11-23 | International Business Machines Corporation | Voltage biasing for magnetic ram with magnetic tunnel memory cells |

| EP0959475A3 (en) * | 1998-05-18 | 2000-11-08 | Canon Kabushiki Kaisha | Magnetic thin film memory and recording and reproducing method and apparatus using such a memory |

| JP2000187976A (ja) | 1998-12-17 | 2000-07-04 | Canon Inc | 磁性薄膜メモリおよびその記録再生方法 |

| JP2000076844A (ja) | 1998-05-18 | 2000-03-14 | Canon Inc | 磁性薄膜メモリ素子およびその記録再生方法、画像録画再生装置 |

| US5969978A (en) * | 1998-09-30 | 1999-10-19 | The United States Of America As Represented By The Secretary Of The Navy | Read/write memory architecture employing closed ring elements |

| JP2000195250A (ja) | 1998-12-24 | 2000-07-14 | Toshiba Corp | 磁気メモリ装置 |

| JP2001067862A (ja) | 1999-09-01 | 2001-03-16 | Sanyo Electric Co Ltd | 磁気メモリ素子 |

| US6166948A (en) * | 1999-09-03 | 2000-12-26 | International Business Machines Corporation | Magnetic memory array with magnetic tunnel junction memory cells having flux-closed free layers |

| JP2001084758A (ja) * | 1999-09-17 | 2001-03-30 | Fujitsu Ltd | 強磁性トンネル接合ランダムアクセスメモリ、スピンバルブランダムアクセスメモリ、単一強磁性膜ランダムアクセスメモリ、およびこれらをつかったメモリセルアレイ |

| JP3913971B2 (ja) | 1999-12-16 | 2007-05-09 | 株式会社東芝 | 磁気メモリ装置 |

| JP3758933B2 (ja) | 2000-03-27 | 2006-03-22 | シャープ株式会社 | 磁気メモリおよびその記録方法 |

| US6172904B1 (en) * | 2000-01-27 | 2001-01-09 | Hewlett-Packard Company | Magnetic memory cell with symmetric switching characteristics |

| JP2001217398A (ja) | 2000-02-03 | 2001-08-10 | Rohm Co Ltd | 強磁性トンネル接合素子を用いた記憶装置 |

| DE10015193A1 (de) * | 2000-03-27 | 2001-10-25 | Infineon Technologies Ag | Hochintegrierte System-on-Chip-Systeme mit nichtflüchtigen Speichereinheiten |

| US6515897B1 (en) * | 2000-04-13 | 2003-02-04 | International Business Machines Corporation | Magnetic random access memory using a non-linear memory element select mechanism |

| JP2002025245A (ja) * | 2000-06-30 | 2002-01-25 | Nec Corp | 不揮発性半導体記憶装置及び情報記録方法 |

| US6456525B1 (en) * | 2000-09-15 | 2002-09-24 | Hewlett-Packard Company | Short-tolerant resistive cross point array |

| JP4149647B2 (ja) | 2000-09-28 | 2008-09-10 | 株式会社東芝 | 半導体記憶装置及びその製造方法 |

| DE10053965A1 (de) * | 2000-10-31 | 2002-06-20 | Infineon Technologies Ag | Verfahren zur Verhinderung unerwünschter Programmierungen in einer MRAM-Anordnung |

| DE10054520C1 (de) | 2000-11-03 | 2002-03-21 | Infineon Technologies Ag | Datenspeicher mit mehreren Bänken |

| JP4667594B2 (ja) * | 2000-12-25 | 2011-04-13 | ルネサスエレクトロニクス株式会社 | 薄膜磁性体記憶装置 |

| US6522579B2 (en) * | 2001-01-24 | 2003-02-18 | Infineon Technologies, Ag | Non-orthogonal MRAM device |

| JP2002359355A (ja) | 2001-05-28 | 2002-12-13 | Internatl Business Mach Corp <Ibm> | 多層構造の不揮発性磁気メモリ・セル及びそれを用いた記憶回路ブロック |

| JP2003016777A (ja) * | 2001-06-28 | 2003-01-17 | Mitsubishi Electric Corp | 薄膜磁性体記憶装置 |

| JP2003133528A (ja) | 2001-10-24 | 2003-05-09 | Sony Corp | 情報記憶装置、その情報書き込み方法およびその製造方法 |

| US6795334B2 (en) * | 2001-12-21 | 2004-09-21 | Kabushiki Kaisha Toshiba | Magnetic random access memory |

| DE10202903B4 (de) * | 2002-01-25 | 2009-01-22 | Qimonda Ag | Magnetoresistive Speicherzelle mit polaritätsabhängigem Widerstand und Speicherzelle |

| JP3875568B2 (ja) * | 2002-02-05 | 2007-01-31 | 株式会社東芝 | 半導体装置及びその製造方法 |

| JP3959335B2 (ja) * | 2002-07-30 | 2007-08-15 | 株式会社東芝 | 磁気記憶装置及びその製造方法 |

| JP2004146687A (ja) * | 2002-10-25 | 2004-05-20 | Toshiba Corp | 磁気記憶装置及びその製造方法 |

| US6859410B2 (en) * | 2002-11-27 | 2005-02-22 | Matrix Semiconductor, Inc. | Tree decoder structure particularly well-suited to interfacing array lines having extremely small layout pitch |

-

2002

- 2002-11-29 TW TW091134785A patent/TW582032B/zh not_active IP Right Cessation

- 2002-11-29 CN CNB021518491A patent/CN100358047C/zh not_active Expired - Fee Related

- 2002-11-29 US US10/305,988 patent/US6807086B2/en not_active Expired - Fee Related

- 2002-11-30 KR KR10-2002-0075649A patent/KR100537116B1/ko not_active IP Right Cessation

-

2004

- 2004-09-09 US US10/936,693 patent/US7151691B2/en not_active Expired - Fee Related

-

2006

- 2006-07-10 US US11/482,817 patent/US7405962B2/en not_active Expired - Fee Related

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN100452233C (zh) * | 2005-01-28 | 2009-01-14 | 株式会社东芝 | 自旋注入磁随机存取存储器及写入方法 |

| CN110910924A (zh) * | 2018-09-18 | 2020-03-24 | 联华电子股份有限公司 | 磁阻式随机存取存储器 |

Also Published As

| Publication number | Publication date |

|---|---|

| TW200304140A (en) | 2003-09-16 |

| TW582032B (en) | 2004-04-01 |

| US7151691B2 (en) | 2006-12-19 |

| US20050030813A1 (en) | 2005-02-10 |

| US7405962B2 (en) | 2008-07-29 |

| US20030103377A1 (en) | 2003-06-05 |

| US20060262595A1 (en) | 2006-11-23 |

| US6807086B2 (en) | 2004-10-19 |

| KR100537116B1 (ko) | 2005-12-16 |

| KR20030044891A (ko) | 2003-06-09 |

| CN100358047C (zh) | 2007-12-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1431663A (zh) | 磁随机存取存储器 | |

| CN1263040C (zh) | 通过磁场的施加进行数据写入的薄膜磁性体存储装置 | |

| CN1207718C (zh) | 容易控制数据写入电流的薄膜磁性体存储器 | |

| CN1490818A (zh) | 薄膜磁性体存储器及与之相关的半导体集成电路器件 | |

| CN1231917C (zh) | 可进行稳定的数据读出和数据写入的薄膜磁性体存储器 | |

| CN1294596C (zh) | 磁随机存取存储器及其读出方法、制造方法 | |

| CN1213435C (zh) | 利用电阻值的变化来存储数据的数据读出容限大的存储装置 | |

| CN1276436C (zh) | 在多个存储单元间共有存取元件的薄膜磁性体存储器 | |

| CN1186780C (zh) | 高速且稳定地进行数据读出工作的薄膜磁性体存储器 | |

| CN100338682C (zh) | 非易失性存储器和半导体集成电路器件 | |

| CN1269134C (zh) | 磁随机存取存储器及其制造方法 | |

| CN1497602A (zh) | 磁随机存取存储器 | |

| CN1172374C (zh) | 半导体存储器 | |

| CN1763985A (zh) | 可变电阻器件及包括该可变电阻器件的半导体装置 | |

| CN1402254A (zh) | 具有含磁隧道结的存储器单元的薄膜磁存储装置 | |

| CN1956207A (zh) | 自旋注入磁随机存取存储器 | |

| CN1385860A (zh) | 具有磁性隧道接合部的薄膜磁体存储装置 | |

| CN1707689A (zh) | 磁性随机存取存储器 | |

| CN1448943A (zh) | 磁存储装置 | |

| CN1669138A (zh) | 半导体器件 | |

| CN1448944A (zh) | 设有数据读出参照用伪单元的薄膜磁性体存储装置 | |

| CN1790912A (zh) | 半导体集成电路装置 | |

| CN1428787A (zh) | 磁随机存取存储器及其制造方法 | |

| CN1452175A (zh) | 磁存储器 | |

| CN1941449A (zh) | 磁阻元件及其制造方法以及磁性随机存取存储器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C17 | Cessation of patent right | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20071226 Termination date: 20121129 |