-

BEZUGNAHME AUF VERWANDTE

ANMELDUNGEN:

-

Die

vorliegende Anmeldung beansprucht die Priorität der vorläufigen US-Patentanmeldung mit

der laufenden Eingangsnummer 60/212,592, eingereicht am 19. Juni

2000, und der vorläufigen

US-Patentanmeldung mit der laufenden Eingangsnummer 60/229,305,

eingereicht am 1. September 2000.

-

HINTERGRUND

DER ERFINDUNG

-

GEBIET DER

ERFINDUNG

-

Die

vorliegende Erfindung betrifft eine Vorrichtung zur Hochleistungsvermittlung

(High Performance Switching) in lokalen Kommunikationsnetzwerken

wie z.B. Token Ring, ATM, Ethernet, Fast Ethernet und 1- und 10-Gigabit-Ethernet-Umgebungen,

die allgemein als LANs bekannt sind. Insbesondere betrifft die Erfindung

eine neue Vermittlungsarchitektur in einer integrierten, modularen

Ein-Chip-Lösung,

die auf einem Halbleitersubstrat wie etwa einem Siliziumchip implementiert

werden kann, sowie eine Switching-Fabric (Vermittlungsstelle), die

eine schnelle Kommunikation zwischen den Switches erlaubt.

-

BESCHREIBUNG

DES STANDES DER TECHNIK

-

Da

sich die Computerleistung in den letzten Jahren gesteigert hat,

sind die Anforderungen an Computernetzwerke beträchtlich gestiegen; schnellere

Computerprozessoren und höhere

Speicherfähigkeiten

erfordern Netzwerke mit hohen Bandbreitenfähigkeiten, um einen Hochgeschwindigkeitstransfer

von beträchtlichen Mengen

an Daten zu ermöglichen.

Die bekannte Ethernet-Technologie,

die auf zahlreichen IEEE-Ethernet-Standards beruht, ist ein Beispiel

für eine

Computervernetzungstechnologie, die bis heute derart modifiziert

und verbessert werden konnte, dass sie eine lebensfähige Rechentechnologie

bleibt. Eine vollständigere Diskussion

von Netzwerksystemen des Standes der Technik kann zum Beispiel in "SWITCHED AND FAST ETHERNET" von Breyer und Riley

(Ziff-Davis, 1996) und in zahlreichen IEEE-Veröffentlichungen gefunden werden,

die sich auf die IEEE-802-Standards beziehen. Auf der Grundlage

des "Open Systems

Interconnect (OSI)"-7-Schichten-Referenzmodells

sind die Netzwerkfähigkeiten

durch die Entwicklung von Verstärkern

(repeaters), Brücken

(bridges), Routern, und neuerdings "Switches" gewachsen, die mit verschiedenen Arten

von Kommunikationsmedien arbeiten. Grobdraht (thickwire), Dünndraht

(thinwire), verdrilltes Leitungspaar (twisted pair) und Glasfasern

sind Beispiele für

Medien, die bis heute für

Computernetzwerke verwendet werden. Switches sind, wenn sie die

Computervernetzung und das Ethernet betreffen, Vorrichtungen auf

Hardwarebasis, die den Fluss von Datenpaketen oder Zellen auf der

Grundlage von Zieladressinformationen steuern, die in jedem Paket

zur Verfügung

stehen. Ein richtig ausgelegter und implementierter Switch sollte

in der Lage sein, ein Paket zu empfangen und das Paket an einen

geeigneten Ausgangsport mit einer Geschwindigkeit zu vermitteln,

die als Leitungsgeschwindigkeit (wire speed, line speed) bezeichnet

wird, welches die maximale Geschwindigkeit ist, zu der das spezielle

Netzwerk fähig

ist.

-

Die

Grund-Ethernet-Leitungsgeschwindigkeit beträgt bis zu 10 Megabits pro Sekunde,

und bei dem Fast Ethernet beträgt

diese bis zu 100 Megabits pro Sekunde. Das neueste Ethernet wird

als ein 10-Gigabit-Ethernet bezeichnet, und es ist in der Lage,

Daten über

ein Netzwerk mit einer Geschwindigkeit von bis zu 1.000 Megabits

pro Sekunde zu übertragen.

Da die Geschwindigkeit höher

geworden ist, sind Entwurfsbeschränkungen und Entwurfsanforderungen,

was das Beachten von zweckdienlichen Entwurfs- und Protokollregeln

und das Bereitstellen einer kostengünstigen kommerziell lebensfähigen Lösung betrifft,

immer komplexer geworden. Zum Beispiel benötigt die Hochgeschwindigkeitsvermittlung

einen Hochgeschwindigkeitsspeicher, um ein geeignetes Puffern von

Paketdaten vorzusehen; ein herkömmliches

dynamisches RAM (Dynamic Random Access Memory (DRAM)) ist relativ

langsam und benötigt

ein Hardware-gesteuertes Auffrischen. Deshalb führt die Geschwindigkeit von

DRAMs als Pufferspeicher bei der Netzwerkvermittlung zum Verlust

von wertvoller Zeit, und es wird beinahe unmöglich, den Switch oder das

Netzwerk bei Leitungsgeschwindigkeit zu betreiben.

-

Außerdem sollte

die Einbeziehung einer externen Zentraleinheit (CPU) verhindert

werden, da die Einbeziehung einer CPU es auch beinahe unmöglich macht,

den Switch bei Leitungsgeschwindigkeit zu betreiben. Da außerdem Netz-Switches

in Bezug darauf, dass Regeltabellen und eine Speichersteuerung benötigt werden,

zusehends komplizierter geworden sind, ist eine komplexe Multichip-Lösung notwendig,

die einen logischen Schaltungsaufbau benötigt, der manchmal als Klebstoff-Logikschaltung

(glue logic circuitry) bezeichnet wird, um zu ermöglichen,

dass die verschiedenen Chips miteinander kommunizieren können. Außerdem kann

die Einrichtung, über

die die Elemente miteinander kommunizieren, die Betriebsgeschwindigkeit

des Switch begrenzen, wenn Elemente so ausgelegt sind, dass sie

auf diese Kommunikationen warten.

-

Unter

Bezugnahme auf das OSI-7-Schichten-Referenzmodell, das vorher diskutiert

worden ist, besitzen die höheren

Schichten typischerweise mehr Informationen. Verschiedene Arten

von Produkten stehen zur Durchführung

der vermittlungsbezogenen Funktionen auf den verschiedenen Schichten

des OSI-Modells

zur Verfügung.

Verteiler (hubs) oder Verstärker

(repeaters) arbeiten bei Schicht Eins, und im Wesentlichen kopieren

und "rundsenden" sie ankommende Daten

zu einer Vielzahl von Speichen des Verteilers. Vermittlungsbezogene

Vorrichtungen der Schicht 2 werden normalerweise als Multiport-Brücken bezeichnet

und sind in der Lage, zwei separate Netzwerke zu überbrücken. Brücken können eine

Tabelle von Weiterleitungsregeln auf der Grundlage dessen aufbauen,

welche MAC-(media access controller; Medienzugangskontroll)-Adressen an welchen

Ports der Brücke

existieren, und können

die Pakete übermitteln,

die für

eine Adresse bestimmt sind, die sich auf einer gegenüberliegenden

Seite der Brücke

befindet. Brücken

verwenden typischerweise das, was als "Spannbaum"-Algorithmus ("spanning tree" algorithm) bekannt ist, um potentielle

Datenschleifen zu eliminieren; eine Datenschleife ist eine Situation,

in der ein Paket endlos in einem Netzwerk Runden dreht und nach einer

bestimmten Adresse sucht. Der Spannbaum-Algorithmus definiert ein

Protokoll zur Verhinderung von Datenschleifen. Schicht-Drei-Switches,

die manchmal als Router bezeichnet werden, können Pakete auf der Grundlage

der Zielnetzadresse weiterleiten. Schicht-Drei-Switches sind in

der Lage, Adressen zu lernen und Tabellen davon zu verwalten, die

den Port-Mappings entsprechen. Die Verarbeitungsgeschwindigkeit

für die Schicht-Drei-Switches

kann verbessert werden, indem eine spezialisierte Hochleistungs-Hardware

verwendet wird, und indem die Host-CPU ausgeschaltet wird (off loading),

so dass die Befehlsentscheidungen nicht das Weiterleiten des Pakets

verzögern.

-

Außerdem spielt

auch die Switch Fabric eine wichtige Rolle bei den Betriebsgeschwindigkeiten

eines Netzwerks. Bei der Verwendung mit Netz- Switches erlaubt es die Fabric, dass

Vermittlungseinheiten mit skalierbaren Portdichten aufgebaut werden

können.

Die Fabric empfängt

vermittelte Daten von den Netz-Switches und muss verschiedene Typen

von Daten (d.h. Multicast, Unicast, Broadcast, etc.) an andere angeschlossene Netz-Switches

weiterleiten. Aber Switch Fabrics aus dem Stand der Technik stellen

nicht den benötigten Durchsatz

bereit und können

die Gesamtverarbeitungsfähigkeiten

der angeschlossenen Netz-Switches beschränken.

-

Die

US 4,872,159 offenbart eine

Paketnetzwerkarchitektur zur Bereitstellung einer schnellen Ansprechzeit

in Form eines Stadtbereichsnetzwerks (MAN; metropolitan area network)

mit hoher Kapazität.

Datenverkehr von Benutzern wird mit Datenkonzentratoren an dem Rand

des Netzwerks verbunden und wird über Glasfaserdatenverknüpfungen

zu einem Verteiler übertragen,

bei dem die Daten vermittelt werden. Der Verteiler umfasst eine

Vielzahl von Datenvermittlungsmodulen, die jeweils eine Steuereinrichtung

aufweisen und jeweils mit einem Raumvielfachschalter (space division

switch) mit verteilter Steuerung verbunden sind. Vorteilhafterweise

führen

die Datenvermittlungsmodule, deren Eingänge mit den Konzentratoren

verbunden sind, alle Prüf- und Routing-Funktionen

durch, während

der maximal 1024 × 1024

große

Raumvielfachschalter, dessen Ausgänge mit den Konzentratoren

verbunden sind, ein großes

Fan-Out-Verteilnetz zum Erreichen vieler Konzentratoren von jedem

Datenvermittlungsmodul aus bereitstellt. Die verteilte Steuerung

des Raummultiplex erlaubt mehrere Millionen Verbindungs- und Trennungsaktionen,

die jede Sekunde durchgeführt

werden können,

während

die dem Pipelining unterzogene und parallele Operation innerhalb

der Steuereinrichtung es jedem der 256 Vermittlungsmodule erlaubt,

wenigstens 50.000 Transaktionen pro Sekunde zu verarbeiten. Die Datenvermittlungsmodule

verketten Gruppen der ankommenden Pakete, die für einen gemeinsamen Auslass des

Raumvielfachschalters bestimmt sind, so dass nur eine Verbindung

in diesem Schalter für

die Übertragung jeder

Gruppe von verketteten Paketen von einem Datenvermittlungsmodul

zu einem Konzentrator benötigt wird.

Das MAN stellt Sicherheitsmerkmale bereit, die eine Portidentifikation,

die von den Datenkonzentratoren geliefert wird, und eine Kontrolle

umfassen, dass jedes Paket von einem autorisierten Ursprungsbenutzer stammt,

der auf einem Port, der mit dem Benutzer assoziiert ist, zu einem

autorisierten Zielbenutzer überträgt, der

sich in der gleichen Gruppe (virtuelles Netz) wie der Ursprungsbenutzer

befin det. Jedes Paket weist eine assoziierte Angabe einer hohen

oder niedrigen Priorität

auf. Anforderungen für

Verbindungen in dem Raumvielfachschalter für eine verkettete Gruppe von

Paketen, deren erstes Paket eine Angabe einer hohen Priorität aufweist,

erhalten den Vorrang.

-

Die

WO 99/56432 offenbart ein Verfahren zum gemeinsamen Gruppieren,

wobei ein Internet-Router mehrere Ausgangsports mit einem gemeinsamen

Ziel als einen gemeinsamen Port behandelt. Eine Routingtabelle verwendet

die IP-Adresse, um einen zusammengesetzten Trunk zu bestimmen, zu

dem das Paket weitergeleitet werden soll. Eine Weiterleitungstabelle

identifiziert eine Route entlang einer Routing-Fabric innerhalb

des Routers zu einem spezifischen Ausgangsport des zusammengesetzten

Ports. Ausgangsports und Routen in der Fabric werden so ausgewählt, dass

die Reihenfolge innerhalb eines Flusses aufrechterhalten wird, indem

der Fluss entlang einer einzigen Fabric-Route zu einem einzigen

Ausgangs-Trunk geroutet wird. Die Weiterleitungstabelle kann Ausgangsports

bevorzugen, die am nächsten

zu einem Paketeingangsport liegen, und die Weiterleitungstabelle

kann so modifiziert werden, dass sie dynamisch die Belastung quer

durch die Trunks eines zusammengesetzten Trunk ausgleicht.

-

ZUSAMMENFASSUNG

DER ERFINDUNG

-

Die

vorliegende Erfindung ist auf eine Switch-auf-Chip-Lösung für eine selbstroutende

Fabric ausgerichtet, die in der Lage ist, das Ethernet, Fast Ethernet

sowie 1- und 10-Gigabit-Ethernet-Systeme zu verwenden, wobei die

gesamte Hardware auf einem einzigen Mikrochip angeordnet ist. Die

vorliegende Erfindung ist auch auf Verfahren gerichtet, die verwendet

werden, um die gewünschte

Verarbeitung und das Weiterleiten der Daten zu erzielen. Die vorliegende

Erfindung ist so konfiguriert, dass sie die Fähigkeit des Paketweiterleitens

bei Leitungsgeschwindigkeit maximiert, und auch dass sie eine modulare

Konfiguration bereitstellt, in der eine Vielzahl von separaten Modulen

auf einem gemeinsamen Chip konfiguriert sind, und wobei individuelle Entwurfsänderungen

bei bestimmten Modulen nicht die Beziehung dieses bestimmten Moduls

zu anderen Modulen in dem System beeinträchtigen.

-

Die

vorliegende Erfindung ist auf ein Verfahren zum Steuern eines Flusses

von Paketdaten in einer Speicherverwaltungseinheit einer Netz-Switch

Fabric ausgerichtet. Ein erster Abschnitt eines Datenpakets wird

an einem Port in einem Eingangsbusring der Netz-Switch Fabric empfangen.

Eine Dienstklasse für

das Datenpaket wird auf der Grundlage des ersten Abschnitts bestimmt,

und der Abschnitt wird in einem Packer-RAM des Ports auf der Grundlage

der Dienstklasse gespeichert. Nachfolgende Abschnitte des Datenpakets

werden in dem Packer-RAM gespeichert. Wenn die vorbestimmte Anzahl

an Abschnitten empfangen worden ist, wird die vorbestimmte Anzahl

an Abschnitten zu einem Paketpool-RAM gesendet. Ein Referenzzeiger zu

einer ersten vorbestimmten Anzahl von Abschnitten wird zu einer

Transaktions-Warteschlange gesendet, wenn ein Ende des Pakets erfasst

wird und ein Ausgangs-Scheduler ein Vorhandensein eines fertigen

Pakets in der Transaktions-Warteschlange erfasst und einen Entpacker

von dem fertigen Paket informiert. Der Entpacker stellt das fertige

Paket in einen FIFO, und das fertige Paket wird zu einem Eingangs-/Ausgangsmodul gesendet.

-

Das

Verfahren kann auch die Schritte des Wartens auf die vorbestimmte

Anzahl von Abschnitten, die empfangen werden sollen, das Zugreifen

auf einen Zeiger zu einem aktuellen freien Abschnitt des Paketpool-RAM

durch eine Linklisten-Array, das Schreiben der vorbestimmten Anzahl

an Abschnitten in das Paketpool-RAM durch eine Linklisten-Array

unter Verwendung des Zeigers, das Setzen oder Aktualisieren einer Linkliste

für das

Datenpaket und den Zeiger, und das Wiederholen der oben genannten

Prozessschritte für nachfolgende

Abschnitte des Datenpakets umfassen. Die Benachrichtigung des Entpackers

von dem fertigen Paket kann das Bestimmen eines nächsten Pakets,

das das fertige Paket sein soll, aus einer Vielzahl von Paketen,

die von einer Vielzahl von Ports empfangen worden sind und in dem

Paketpool-Speicher gemäß vorbestimmten

Prioritätsregeln

gespeichert worden sind, umfassen. Die vorausbestimmten Prioritätsregeln,

die verwendet werden, können

ein Defizit-Round-Robin-Scheduling-Algorithmus

und ein gewichteter Round-Robin-Scheduling-Algorithmus sein.

-

Außerdem kann

der Schritt des Erfassens des Vorhandenseins des fertigen Pakets

das Überwachen eines

Alters von Paketdaten in der Transaktions-Warteschlange und das Löschen der

Paketdaten umfassen, wenn das Alter grö ßer als ein vorbestimmter Wert

ist. Auch kann der Schritt des Sendens eines Referenzzeigers das

Bestimmen, ob eine Dienstklasse in der Transaktions-Warteschlange ein

Limit erreicht hat, und das Löschen

des Datenpakets umfassen, wenn die Transaktions-Warteschlange das

Limit erreicht hat.

-

KURZE BESCHREIBUNG

DER ZEICHNUNGEN

-

Die

Aufgaben und Merkmale der Erfindung werden unter Bezugnahme auf

die nachfolgende Beschreibung und die beigefügten Zeichnungen besser verständlich,

in denen:

-

1 ein

Blockdiagramm ist, das ein Ausführungsbeispiel

der vorliegenden Erfindung veranschaulicht, das mit Netz-Switches

verwendet wird, um eine 64-Port-Gigabit-Lösung zu erzielen;

-

2 eine

schematische Darstellung ist, die Elemente der Fabric der vorliegenden

Erfindung zeigt;

-

3 eine

schematische Darstellung ist, die die interne Blockstruktur eines

Ausführungsbeispiels zeigt;

-

4 ein

Ablaufdiagramm für

die Eingangslogik für

die vorliegende Erfindung ist;

-

5 ein

Unterablaufdiagramm für

die Eingangslogik für

die vorliegende Erfindung ist;

-

6 ein

Unterablaufdiagramm für

die Eingangslogik für

die vorliegende Erfindung ist;

-

7 ein

anderes Ablaufdiagramm für

die Eingangslogik für

ein Ausführungsbeispiel

der vorliegenden Erfindung ist;

-

8 die

Topologie des Eingangsbusrings veranschaulicht;

-

9 eine

Abbildung des kürzesten

Weges von Port zu Port veranschaulicht;

-

10 eine

schematische Darstellung ist, die die Speicherverwaltungseinheit-Warteschlangenbildungsarchitektur

veranschaulicht;

-

11 ein

Kontoführungsblock-Pausenverhalten

veranschaulicht;

-

12 eine

schematische detaillierte Darstellung einer Station des Eingangsbusrings

ist;

-

13 eine

schematische Darstellung der Ringkonnektivität des Eingangsbusrings ist;

-

14 eine

schematische Darstellung ist, die die verschiedenen Paketbegrenzungsfälle in einer

Zelle des Speichers veranschaulicht;

-

15 ein

Ablaufdiagramm ist, das das Wiederherstellungsschema der vorliegenden

Erfindung bei Speicherfehlern veranschaulicht;

-

16 ein

Blockdiagramm für

den Entpacker (unpacker) der vorliegenden Erfindung ist.

-

AUSFÜHRLICHE

BESCHREIBUNG DER BEVORZUGTEN AUSFÜHRUNGSBEISPIELE

-

Die

vorliegende Erfindung ist auf eine selbstroutende Fabric mit 4/8

10 Gigabit-Schnittstellen gerichtet. Die externe Bandbreite der

Fabric gemäß einem

Ausführungsbeispiel

der vorliegenden Erfindung beträgt 80/160

Gbps. Die vorliegende Erfindung erlaubt den Aufbau von skalierbaren

Gigabit-Portdichten zusammen mit anderen Netzwerkvermittlungsvorrichtungen.

-

Die

vorliegende Erfindung sieht eine Fabric mit einer Ein-Chip-Lösung vor,

die einen Durchsatz von bis zu 160 Gbps unterstützt. Die vorliegende Erfindung

unterstützt

8 Ports bei 10 Gbps Vollduplex und erlaubt das Weiterleiten mit

voller Leitungsgeschwindigkeit an jedem Port. Die Fabric unterstützt auch

acht IEEE 802.1p Prioritätsklassen

sowie eine Warteschlangenbildung nach strenger Priorität und nach

gewichtetem Round-Robin-Verfahren. Die Fabric der vorliegenden Erfindung

unterstützt

4096 VLANs für

unbekannte Unicasts/Broadcasts und unterstützt die IEEE 802.3x Flusskontrolle

an jedem Port. Die vorliegende Erfindung unterstützt auch einen Mechanismus

zur Verhinderung der Leitungskopfblockierung (Head of Line (HOL)

blocking) an einem Übertragungsport

und bietet auch Unterstützung

für das

Gruppieren (Trunking) und das Spiegeln sowie auch für die Redundanz.

Schließlich

stellt die vorliegende Erfindung in einem Ausführungsbeispiel eine 66 MHz

32-Bit-PCIX-Erweiterungsschnittstelle

für die

CPU und andere PCI-konforme Vorrichtungen bereit.

-

1 veranschaulicht

ein Beispiel der Fabric der vorliegenden Erfindung in einem bestimmten

Anwendungsfall. 1 veranschaulicht ein Beispiel

einer 64-Port-Gigabit-Lösung

(blockierungsfrei), die die Fabric der vorliegenden Erfindung und

Netz-Switches verwendet. Die allgemeine Konfiguration der Fabric

der vorliegenden Erfindung ist in 2 veranschaulicht.

Ein bevorzugtes Ausführungsbeispiel

der Fabric besitzt 8 Port-Schnittstellen mit Datenübertragungsgeschwindigkeiten

von 10 Gbps und einen internen Ring, der den Transfer von Informationen

und Paketdaten zwischen den Port-Schnittstellen erlaubt.

-

Die

vorliegende Erfindung ist eine Fabric mit einer sehr hohen Geschwindigkeit,

die im Sinne der Logik für

die Datenrahmenweiterleitentscheidungen einfach ist. Jedes Paket,

das die Fabric betritt, muss einen Modul-Zellkopf (module header) aufweisen,

der Informationen für

Unicast-Pakete über

das/die Zielmodule) enthält,

zu dem/denen ein Rahmen weitergeleitet werden muss. Der Modul-Zellkopf

wird an dem Ausgang von dem Netz-Switch vorne angehängt.

-

In

einem bevorzugten Ausführungsbeispiel

besteht die Fabric aus 8 Ports, von denen jeder bei einer Geschwindigkeit

von 10 Gigabit arbeitet. An jedem Port wird der Modul-Zellkopf geprüft und die

Ausgangsport-Bitmap wird auf der Grundlage davon bestimmt, ob das

Paket ein bekanntes Unicast, unbekanntes Unicast, Broadcast, Multicast

oder ein IP Multicast ist. Die oben genannten Pakettypen werden

unten besprochen.

-

UNICAST-PAKET

-

Wenn

ein Rahmen (Frame) von dem Fabric-Eingang (fabric ingress) empfangen

wird, zeigt der Opcode-Wert von 1 in dem Zellkopf (header) an, dass

das Paket ein Unicast-Paket ist und die Ausgangsport- und Zielmodul-id-(DST_MODID)-Informationen

in dem Modul-Zellkopf gültig

sind. Die Fabric wird das Paket zu dem Ausgangsport (egress port)

in der Fabric weiterleiten, welches der Pfad zu dem Zielmodul ist.

Alternativ dazu kann es in einigen Konfigurationen mehr als einen

Pfad zu dem Zielmodul in der Fabric geben. Deshalb kann es sein,

dass die Fabric einen Ausgangsport auf der Grundlage des Fabric-Eingangsports

und der Zielmodul-id auswählen

muss. In Konfigurationen, in denen die Zielmodule direkt mit der

Fabric verbunden sind, basiert die Auswahl des Fabric-Ausgangsports

(fabric egress port) auf dem Zielmodul und ist unabhängig von dem

Fabric-Eingangsport (fabric ingress port).

-

Zur

Unterstützung

der Datenrahmenweiterleitung eines Unicast-Pakets in der Fabric

in jeglichem Typ von Konfiguration ist eine einfache Routingtabelle

vorgesehen. Das Format dieser Tabelle ist folgendermaßen:

Tabelle

1

-

Diese

Tabelle ist 32 Einträge

tief, und wenn ein bekanntes Unicast-Paket an dem Fabric-Eingang ankommt,

wird das DST_MODID aus dem Modul-Zellkopf extrahiert und in der

obigen Tabelle nachgesehen. Die sich ergebende Bitmap wird dazu

verwendet, um die Weiterleitung zu den passenden Ports, die den

Bitfeldern entsprechen, durchzuführen.

-

BROADCAST-PAKET/DLF-WEITERLEITUNG

-

Wenn

ein Paket an dem Fabric-Eingang mit dem Opcode-Wert 2 ankommt, zeigt

dies an, dass das Paket entweder ein Broadcast oder ein unbekanntes

(Domain Lookup Failure; Domänenanfragefehler)

Unicast ist. In diesem Fall wird die VLAN-ID dazu verwendet, um

alle die Ports anzuzeigen, zu denen das Paket geliefert werden soll.

Eine Tabelle ist an jedem Port vorgesehen:

Tabelle

2

-

Die

Tabelle ist 4096 Einträge

tief und erlaubt alle Werte der VLAN-Klassifikation.

-

MULTICAST-PAKET-WEITERLEITUNG

-

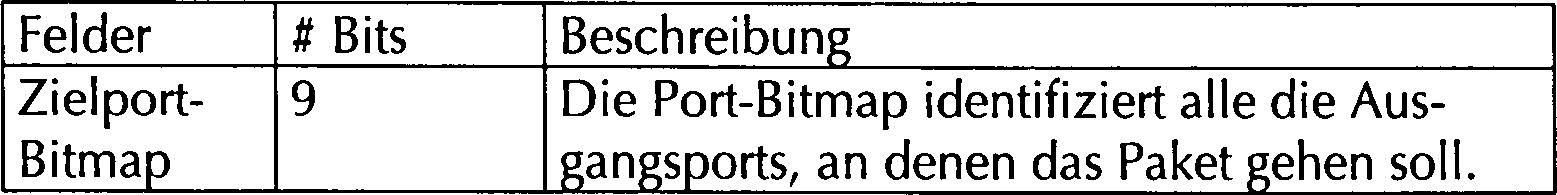

Wenn

ein Paket an dem Fabric-Eingang mit dem Opcode-Wert 3 oder 4 ankommt,

handelt es sich jeweils entweder um ein Multicast (MC) oder ein

IP MC. Eine Tabelle ist implementiert, um diese Pakete weiterzuleiten.

Der Index zu dieser Tabelle ist die Kombination aus der Zielport-ID

(DST_PORTID) und der Zielmodul-ID (DST_MODID), die aus dem Modul-Zellkopf

extrahiert werden.

-

-

Es

gibt 8 Kopien von allen oben genannten Tabellen bzw. eine pro Port.

Die Konfiguration der Fabric der vorliegenden Erfindung umfasst

ein Ausgangsmaskenregister (EGRESS_MASK). Dieses Register identifiziert

den Satz von Ports, aus denen das Paket von einem Eingangsport aus

nicht gesendet werden darf. Dieses Register ist 9 Bits breit, und

es gibt ein Register pro Port.

-

Jeder

Eingangs-Port besitzt die folgenden Blöcke: einen Kern für die physikalische Übertragung

(SerDes), einen 10-Gigabit-Ethernet-Vollduplex-MAC und einen Eingangslogik-Block, der

das Datenrahmenweiterleiten (ING) bestimmt. Jeder Ausgangsport besitzt

die folgenden Blöcke:

einen Eingangsbusringknoten (IBR); eine Speicherverwaltungseinheit

(MMU), und ein Paketpool-RAM.

-

Die

vorliegende Erfindung unterstützt

auch viele spezielle Merkmale. Die Fabric unterstützt die

Linkgruppierung (Trunking) ihrer acht 10-Gbps-Ports. Bis zu 4 Trunk

Groups (Leitungsbündel)

können

unterstützt werden,

jeweils bis zu einem Maximum von vier Mitgliedern. Die Trunk-Group-Tabelle

wird verwendet, um den Ausgangsport abzuleiten, wenn ein Paket auf

einem Trunk Port herausgehen muss. Der RTAG wird von der Trunk-Group-Tabelle

durch die Trunk-Verteilungslogik aufgenommen, um den Verteilungsalgorithmus

zu bestimmen.

Tabelle

4

-

Es

gibt vier Kopien der obigen Tabelle, die vier Trunk Groups erlauben.

-

Die

Fabric der vorliegenden Erfindung unterstützt auch das dynamische Ausschalten

(shutting down) der Ports in dem Falle, dass der Link (Verbindung)

schlechter wird. Die Fabric unterbricht die CPU in so einem Fall.

Dann ist die CPU dafür

verantwortlich, das EPC-Link-Register so zu programmieren, dass

es das Austreten von Paketen aus dem deaktivierten Port nicht mehr

zulässt.

Das EPC_Link-Register ist eine Bitmap, die Ports repräsentiert,

die ein Link-Valid-Signal

besitzen. Außerdem

wird auch das Spiegeln (mirroring) unterstützt. Das Spiegelung-zum-Port-Register

zeigt das Spiegeln zum Port in der Vorrichtung an und spezifiziert das

Weiterleiten der Pakete, die gespiegelt werden sollen. Die Spiegelungsinformation

wird aus dem Modul-Zellkopf extrahiert. Ein CPU-zum-Port-Register wird ebenfalls unterstützt.

-

Ein

Priorität-zu-Dienstklasse-Warteschlangen-Mapping-Register

(Priority to COS Queue Mapping Register) (COS_SEL) wird verwendet,

um die ankommende Paketpriorität

oder die abgeleitete Paketpriorität (nach der Adressauflösung und

dem Filterungsmechanismus) der Ausgang-Dienstklasse-Warteschlange zuzuordnen.

Das Priorität-zu-Dienstklasse-Warteschlangen-Mapping wird ausgeführt, nachdem

das Paket durch die Adressauflösung

und den Filterungsmechanismus gegangen ist, gerade bevor das Paket

auf dem CP-Kanal

gesendet wird. Dieses Mapping ändert

nicht das Prioritätsfeld

in dem Tag-Zellkopf (tag header) des Pakets, es entscheidet nur,

aus welcher Dienst klasse-Warteschlange das Paket an dem Ausgangsport

herausgehen soll. Der Bedarf an diesem Register ergibt sich aufgrund

der empfohlenen Benutzer-Priorität-zu-Verkehrsklasse-Mappings

(User Priority to Traffic Class Mappings), die in dem 802.1p-Standard

definiert sind.

-

Außerdem stehen

in der Fabric Konfigurationsregister zur Verfügung. Jedes der folgenden besitzt

8 Kopien dieser Register, d.h. 1 pro Port. Ein MODUS-Register wird

gesetzt, wenn alle Ports in der Fabric im HiGig-Modus arbeiten,

sonst wird die Vorrichtung in einem Modus mit einer niedrigen Bitrate

arbeiten. Es werden auch Register unterstützt, um Auslöser für sowohl

die hohen als auch die niedrigen Flutmarken für die Eingangs-Rückstau-Flusskontrolle bereitzustellen.

Ein anderes Register spezifiziert auch den Prioritätswarteschlangenbildungsalgorithmus,

einschließlich

eines strengen Prioritätsmodus,

eines gewichteten Round-Robin-Modus und eines Defizit-Round-Robin-Modus. Es sind

auch Register vorgesehen, die die Prioritätswertungen für die Dienstklassen

und das jeweilige HOL-Blockierungslimit speichern.

-

Die

folgenden Zähler

sind ebenfalls auf einer pro Port Basis auf der Übertragungs- und der Empfangsseite

vorgesehen. Eine Eingangswortzählung

(ingress word count) liefert die Anzahl an Worten, die von dem MAC

empfangen werden, und eine Ausgangswortzählung (egress word count) liefert

die in dem Ausgang gespeicherte Anzahl an Worten auf einer Basis

der Dienstklasse (COS; Class of Service). Zählungen für fallen gelassene Pakete werden

für die

Anzahl an Paketen bestimmt, die von der Eingangslogik fallen gelassen

werden, und eine Paketzählung

der aufgrund von HOL fallengelassenen Pakete liefert die Anzahl

an Paketen, die pro COS fallen gelassen werden. Es wird auch eine

Zählung

im Hinblick auf die Anzahl an Paketen verwaltet, die aufgrund von

Alterung fallen gelassen werden.

-

Außerdem stellt

die Fabric der vorliegenden Erfindung eine gesicherte Weiterleitungsunterstützung (assured

forwarding support) bereit. Dieses Merkmal stellt ein bevorzugtes

Fallenlassen von Paketen in der Fabric bereit, wenn ein bestimmtes

Bit in dem Modul-Zellkopf gesetzt ist. Dieses Bit in dem Modul-Zellkopf wird von

dem Netz-Switch gesetzt, wenn ein gewisser Vorrang für das Fallenlassen

(drop precedence) gesetzt wird. Wenn ein Paket in der Fabric-MMU ankommt und das

Bit gesetzt ist, dann wird die Anzahl an Paketzeigern für die COS-Warteschlange,

die dem Paket zugeordnet ist, gegenüber einem CNGTHRESHOLD-Register überprüft. Wenn

die Anzahl an Einträgen

in der COS-Warteschlange für

den Port den Wert in dem CNGTHRESHOLD-Register überschreitet, wird das Paket

fallen gelassen.

-

Anderenfalls

wird das Paket in die COS-Warteschlange in der MMU aufgenommen.

Wenn das Paket fallen gelassen wird, wird ein CNGDROPCOUNT-Zähler aktualisiert.

Wenn das bestimmte Bit nicht in dem Modul-Zellkopf gesetzt ist,

werden alle Pakete in die COS-Warteschlange aufgenommen, bis der

COS-Warteschlangen-Schwellwert (COS Queue Threshold) erreicht ist.

-

LOGISCHER

FLUSS AM EINGANG

-

Der

logische Fluss am Eingang in die Fabric wird im Folgenden diskutiert. 4 zeigt

ein Ablaufdiagramm, das einen Teil der Logik vorsieht. In dem ersten

Schritt wird die Port-Bitmap initialisiert und die COS wird von

dem Modul-Zellkopf bezogen. Ein Opcode wird ebenfalls aus dem Modul-Zellkopf

ausgelesen. Wenn das Paket nur gespiegelt wird, dann wird keine

weitere Auswertung des Zellkopfs benötigt. Anderenfalls wird der

Typ des Pakets aus dem Opcode bestimmt, wobei die Port-Bitmap oder

eine andere Bitmap gesetzt ist. Die unterstützten Typen umfassen ein CPU-Paket,

das zu der CPU gesendet wird, Unicast, Broadcast, Schicht-2-Multicast

und IP-Multicast. Wenn die richtigen Variablen gesetzt sind, geht

der logische Fluss zum Unterablaufdiagramm M, es sei denn, dass

die Logik diktiert, dass das Paket fallen gelassen werden soll.

Im letzteren Fall wird ein Eingangszähler inkrementiert.

-

Der

logische Fluss setzt sich bei M, 5, fort,

wobei dann, wenn das Paket nur gespiegelt wird, ein Register überprüft wird,

und wenn das Paket noch nicht gespiegelt ist, dann wird das Spiegeln-zum-Port-Register

gesetzt und die Port-Bitmap wird gesetzt, um das Paket zu spiegeln.

Als nächstes

wird dann, wenn der Eingangsport ein Mitglied einer Trunk Group

ist, die Port-Bitmap

entsprechend gesetzt. Die Verarbeitung von Ports in einer Trunking

Group wird genauer in 6 behandelt.

-

7 veranschaulicht

einen anderen Betriebsmodus für

die Evaluierung der Pakete. Das alternative Verfahren untersucht

Bits der Quell- und Zielports. In diesem Fall wird eine Vorrichtungs-Port-Mapping-Tabelle verwendet,

um den Switch-Ausgangsport zu bestimmen. Es sei angemerkt, dass

die Betriebsmodi nicht gemischt werden sollten, wobei der letztgenannte

Modus alle Broadcast, Multicast und unbekannten Unicast zu allen

Ports sendet und das Spiegeln in dem letztgenannten Modus nicht

unterstützt

wird.

-

AUFBAU DER

SPEICHERVERWALTUNGSEINHEIT

-

Als

nächstes

werden der Aufbau und die Funktion der Speicherverwaltungseinheit

der Fabric genauer besprochen.

-

Die

Hauptfunktionen der Fabric der vorliegenden Erfindung können in

mehrere Bereiche gruppiert werden. Erstens, und das betrifft die

Switch Fabric-Bandbreite,

absorbiert die Fabric Paketströme

von acht Eingangsports mit einer Gesamtrate von maximal 80 Gbps.

Die Fabric erlaubt es den Paketen, an einem geeigneten Ausgang für Unicast

und Multicast mit einer Gesamtrate von 80 Gbps auszutreten und berücksichtigt

die Kapazitätsverwendung

durch den Eingang/Ausgang. Die Fabric verwaltet effektiv den Multicast-Verkehr

und verarbeitet den zusätzlichen

Modul-Zellkopf, der mit jedem Paket hereinkommt. Auch kann ein CPU-Verkehr von

oder zu einem Port kommen und hat eine maximale Burstrate von ~

2 Gbps.

-

Die

Fabric unterstützt

auch die 802.1p Warteschlangenbildung. Die Fabric priorisiert Pakete

durch COS und unterstützt

bis zu 8 Warteschlangen. Die Fabric unterstützt auch die Warteschlangenbildung

nach strenger Priorität

und das Fair Queuing (faire Warteschlangenbildung) mit gewichteter

Zuordnung durch die Paketzählung.

Die Fabric stellt auch eine geeignete Flusskontrolle und ein geeignetes

Kapazitätsmanagement bereit.

Wenn ein gegebener Eingang einen Kapazitätsschwellwert überschreitet,

erhält

der Anstoß gebende Eingangsport

eine Benachrichtigung. Der MAC sollte einen PAUSEN-Rahmen an seinen

Link-Partner schicken, um den Fluss der Pakete zu stoppen. Wenn

ein gegebener Ausgang einen Zellenkapazitätsschwellwert überschreitet,

existiert eine HOL-(Leitungskopfl-Blockierung. Wenn ein gegebener

Ausgang in dem HOL-Zustand ist, wird jedes Paket von einem Port,

das für

diesen Ausgang bestimmt ist, fallen gelassen. Wenn eine Transaktions-Warteschlange

für eine

gegebene COS für

einen gegebenen Ausgang voll wird, tritt sie in einen HOL-(Leitungskopf)-Blockierungs-Zustand.

Jedes neue Paket von irgendeinem Port, das für dieses COS-/Ausgangs-Paar

bestimmt ist, wird verworfen.

-

Zusätzlich sind

die folgenden Merkmale weiterentwickelte Merkmale, die in bestimmten

bevorzugten Ausführungsbeispielen

integriert werden können.

Die Fabric unterstützt

das Fair Queuing mit gewichteter Zuordnung durch eine Bytezählung und

stellt ein Speicherfehler-Wiederherstellungsschema bereit.

-

EINGANGSBUSRING

-

Die

Architektur der Fabric umfasst bestimmte Abschnitte, die die Fähigkeit

der Fabric, Pakete weiterzuleiten, verbessern. Ein erster Abschnitt

ist ein Eingangsbus-"Ring". Zum Beispiel kann

die Architektur für

die MMU ein verteiltes feststehendes Kapazitätsschema sein, bei dem eine

lokale Kopie des RAM (128K Bytes) für jeden Port reserviert ist.

Jeder Port ist mit den benachbarten Ports über eine Ansammlung von unidirektionalen

Bussen verbunden, die effektiv einen Ring bilden, der alle neun

(8 + CPU) Ports verbindet. Dieser Bus wird nachfolgend der Eingangsbusring

(IBR; Ingress Bus Ring) genannt. Die Busse sind 64 Bits breit, und

es gibt einen Bus für

jeden Eingang (folglich insgesamt 64·8 = 512 Bits). Diese Busse

sind verkettet und jeder hat seinen Ursprung von dem Ausgang eines

Flops eines Ports und endet an dem Eingang eines Flops an seinem benachbarten

Port. Dies ist in 3 veranschaulicht. Dieses Punkt-zu-Punkt-Schema

spricht viele physikalischen Designaufgaben an, die vorliegen, wenn

anderenfalls ein gemeinsamer globaler Speicher mit breiten (512

Bits) Datenleitungen verwendet wird. Dieses Schema macht auch jeden

Port zu einer separaten logischen Entität, was für die Prüfbarkeit von Wert ist.

-

Der

IBR übermittelt

den Paketverkehr, der von dem Port-Eingangs-/Ausgangsblock (PIE)

weitergereicht worden ist, und tritt bei jedem Taktzyklus bei einer

64-Bit-Breite auf. Die Daten werden sofort auf die lokalen Flops

auf dem Bus zwischengespeichert (latched). Und bei jedem Takt wird

dieses Wort in die Flops des/der benachbarten Port(s) zwischengespeichert.

Dann überwacht

die MMU an jedem Port die Wortströme auf dem Ring und erfasst

das Paket, wenn sie eine Zielportübereinstimmung feststellt.

Die Zielportinformation wird über

ein Steuerwort kommuniziert, das mit dem Paket über einen Seitenbandbus synchronisiert

ist.

-

Eine

Leistungsoptimierung, die durchgeführt werden kann, ist, die Datenfortpflanzung

zu deaktivieren, wenn keiner der Ports abwärts auf dem Ring der Empfänger dieses

Paketes ist. Auch leitet in einem Ausführungsbeispiel jeder Buskanal

das Wort in einer Richtung weiter, was eine maximale Latenzzeit

von 8 Takten (oder 8 Sprüngen)

ergibt, um den am entferntesten gelegenen Port zu erreichen. Dies

kann verbessert werden, wenn die Worte in entgegengesetzten Richtungen

weitergeleitet werden (im Uhrzeigersinn und im Gegenuhrzeigersinn),

so dass der maximale Sprung bis runter auf 4 geht. Das folgende

Diagramm, das in 8 vorgesehen ist, trifft auf

jeden Port zu.

-

Effektiverweise

gibt es 9 Busse in dem Fabric-Chip (9 = 8 Ports + CPU-Port). Aber wenn

ein Querschnitt zwischen irgendwelchen zwei Ports genommen wird,

wird ein Bereich für

nur 8 Busse benötigt,

weil für jeden

Port n seine Nachbarn n + 4 und n – 4 nicht verknüpft sind.

Kein Bus ist eine tatsächlich

geschlossene Schleife. Eine Abbildung für die kürzesten Wege von einem Port

zu einem anderen Port in diesem Schema ist in 9 veranschaulicht.

-

PORT-COS-PAARE

-

Ein

anderer Abschnitt der Fabric spricht die Port-COS-Paare an. Pakete

kommen als 8-Byte-Worte an, aber die RAM-Breite beträgt 80-Byte-Zellen.

Diese Inkongruenz birgt in sich einige Verwendungsprobleme, und

zwar vor allem dann, wenn die Paketlängen pathologische Fälle wie

etwa ein CELLSIZE (Zellengröße) + 1

(d.h. 65-Bytes-Pakete) sind. Wenn eine solche Bedingung fortdauert,

wird die RAM-Bandbreite beträchtlich gefährdet und

ergibt eine schwierige Anforderung von 3,6 Lese-/Schreibvorgängen pro

Takt.

-

Um

dieses Problem zu lösen,

werden Pakete zwischen RAM-Grenzen gepackt und entpackt. Worte werden

in einem Registerdatei-(oder SRAM)-FIFO gesammelt, bis eine Zellgröße vor dem

Schreibvorgang fertig ist. Die Zellen werden aus einem Speicher,

der in einem FIFO platziert ist, ausgelesen und dann langsam an

den PIE als Worte gegeben.

-

Dies

wirft aber ein weiteres Problem auf, da, um das SAP-zu-SAP-Sequentialisieren

aufrechtzuerhalten, die Pakete an sehr spezifischen Stellen in dem

RAM platziert werden müssen,

damit ihr Eingang-zum-Ausgang-Pfad nicht von Paketen von anderen

Ports und Dienstklassen korrumpiert wird. Folglich wird die Verwendung

eines "Port-COS"-Paares eingeführt. Ein

Port-COS-Paar besteht aus zwei Zahlen P:C. P bezeichnet, von welchem

Port das Paket kam, und C bezeichnet, zu welcher Dienstklasse dieses

Paket gehört.

Jedes Paket, das das Fabric-System betritt, wird mit einer P:C-Bezeichnung

versehen (obwohl dies nicht von irgendwelchen Speicherelementen

repräsentiert

sein muss), und sie müssen

einem bestimmten P:C-Strom in dem System folgen.

-

Im

Hinblick auf dieses System ist P = 9 – 1 = 8, da keine Pakete für seinen

eigenen Port bestimmt sein werden, und C = 4 und P·C – 32. Folglich

können

in der Fabric bis zu 32 Ströme

bestehen. Für

jeden Port existieren logischerweise 8 Pack-FIFOs, 8 Warteschlangen

im Speicher und 8 Entpack-FIFOs.

-

NACHRICHTENRING

-

Ein

anderer Abschnitt der Fabric ist ein Nachrichtenring (MR; Message

Ring). Um alles Stationen für die

Steuerung zu verknüpfen,

wird ein anderer Ring verwendet, der unidirektional ist und an jeder

Station gefloppt (flopped) ist und eine geschlossene Schleife ist.

Dieser Ring stellt eine generische Art der Übermittlung von Nachrichten

zwischen Stationen bereit (einschließlich der CPU). Augenblicklich

dient er zwei Hauptzwecken: CPU-Register-/Speicherbild-Zugriff zwischen allen

Stationen und Kontoführung

zwischen Eingangs- und Ausgangsstationen.

-

Das

Nachrichtenprotokoll auf dem MR kann analog zu dem eines IEEE 802.5

Token-Ring-Netzes oder eines ISO-8802.7 Slotted-Ring-Netzes sein.

Register-/Zähler-Lesevorgänge/Schreibvorgänge sowie

auch Speicheranforderungen und -gewährungen auf dem MR werden unter

Verwendung dieses Protokolls übermittelt.

Es gibt zwei Bedingungen bei der Auswahl eines Protokolls, es muss

1) die benötigte

Bandbreite für

den ungünstigsten

Betriebsfall zufrieden stellen, und 2) das Protokoll selber muss

robust und deterministisch (prüfbar)

sein und darf niemals eine gegenseitige Blockierung (deadlock) hervorrufen.

-

Die

Bandbreite für

den ungünstigsten

Betriebsfall ist im Augenblick durch die interstationäre Kontoführung (inter-station

accounting) begrenzt. Die interstationäre Kontoführung ist ein Verfahren, mit

dem für

den Eingang berechnet werden kann, wie viele Bytes von jedem Ausgang

für alle

Pakete, die den Port betreten haben, ausgesendet wurden. Wenn nicht

genug Bytes gutgeschrieben (credited) werden, wird es in den RÜCKSTAU-Zustand

eintreten, nachdem der Zähler

eine programmierte Flutmarke erreicht.

-

Bei

diesem Mechanismus verwaltet jeder Ausgang einen Zähler, der

verfolgt, wie viele Bytes er für

Pakete ausgesendet hat, die von anderen Ports kamen. Folglich muss

er 8 Zähler

verwalten. Nach einem programmierten Schwellwert muss jeder Ausgang

diesen Zählerwert

zurück

an den entsprechenden Ursprungseingang berichten. Der MR besitzt

auf sich 9 Stationen, und es wird ein Takt pro Station benötigt. Der

ungünstigste

Betriebsfall ist 9·8

= 72 Takte, bevor ein Ausgang alle seine Gutschriften (credits)

auf Null stellen kann.

-

ADAPTIVER

ERWEITERTER SPEICHER

-

Die

obige Speicherarchitektur hat aber einen Nachteil. Wenn nur 3 Ports

aktiviert sind, stehen nur 3·256

KB oder 768 KB für

die Paketspeicherung zur Verfügung.

Tatsächlich

können

nur 256 KB verwendet werden, wenn der einzige Verkehr darin besteht,

dass zwei dieser Ports an den dritten Port senden. Die RAMs in dem

Rest des Chips sind vergeudet.

-

Die

adaptive erweiterte Speicherarchitektur ist so erweitert, dass sie

ein adaptives Protokoll umfasst, um eine Flexibilität bei der

Speicherbenutzung vorzusehen. Zur automatischen Einstellung auf

die Anpassung wird ein Nachrichtenprotokoll verwendet (über den

MR). Ein Port tritt in den PANIK-Modus ein, wenn seine Anzahl an

freien Zellen eine untere Flutmarke erreicht. In diesem Zustand

wird der Port von dem nächsten

verfügbaren

Slot auf dem MR Besitz ergreifen und sendet eine Speicheranforderungsnachricht.

Nur deaktivierte Ports können

an der Gewährung

von Speicherverwendung an in Panik ausbrechende Ports teilnehmen.

Wenn die Originalanforderung zu dem Requester zurückkehrt,

nachdem sie die Schleife durchquert hat, zeigt sie an, dass ent weder

kein Port deaktiviert ist oder dass alle deaktivierten Ports bereits

jemand anderem helfen.

-

Wenn

die Anforderungsnachricht verarbeitet wird und eine Speichergewährungsnachricht

zurückschickt,

wird der anfordernde Port aufhören,

Pakete zu akzeptieren, die an ihn selber gerichtet sind. Der gewährende Port

wird damit beginnen, die Pakete in dessen Namen anzunehmen. Da alle

Pakete allen Ports sichtbar sind, kann dieser Austausch von Paketeigentumsrechten

durchgeführt

werden, aber nicht ohne Vorsichtsmaßnahmen zu treffen. Es gibt

verschiedene Übertragungs-

und Übergabe-Timing-Schwierigkeiten,

die berücksichtigt

werden müssen.

-

Beispielshalber

nimmt man drei aktive Ports an: mit den Nummern 0, 4 und 8, und

fünf nicht

benutzte Ports mit den Nummern 1–3 und 5–7. Jeder aktive Port verwendet

einen erweiterten Speicher von mehr als 256 KB Speicher. Helfer-MMUs

wie z.B. in Ports 5, 6 und 7 nehmen Pakete in Vertretung von Port

4 entgegen und speichern Pakete in Vertretung von Port 4, wobei

sie Port 4 eine effektive Speicherbenutzung von 1 MByte geben. Jede

Helfer-MMU muss Paar-COS-Ströme

aufrechterhalten sowie auch den Prioritätsalgorithmen folgen, die in

dem System vorhanden sind.

-

Pakete

werden sich aus Port 4 entleeren, und wenn dessen Zählung der

freien Zellen eine untere Flutmarke erreicht, wird er eine Ablöseanforderungsnachricht

(detach request message) für

seinen Helferport aktivieren. Dann wird der Port 5, der nächste Helferport

in der Leitung, "langsam" seine Ströme im Speicher

zu Port 4 entleeren. Dieser Effekt pflanzt sich die Leitung der

Helfer hinunter fort. Bis der Speicher von Port 7 vollständig geleert

ist, wird Port 7 eine Ablöseversuchsnachricht

und eine Ablösebestätigungsnachricht

ausgeben. Wenn sie abgelöst

ist, wird die MMU 7 zur Verfügung

stehen, um Speicheranforderungen von irgendeinem anderen Port zu

gewähren,

einschließlich

Port 4. Eine Helfer-MMU kann, wenn sie sich festgelegt hat, nicht

mehr als einem einzigen anderen Port dienen. Jede MMU kann Daten

vom IBR bei 80 Gbps abgreifen. Jede MMU kann Daten bei 10 Gbps entleeren.

-

Die

Absicht der Architektur ist Flexibilität beim Anschließen und

Ablösen

jeglicher Anzahl von "Helfer"-MMUs an bzw. von

jedem Port. Dadurch wird eine dynamische Zuordnung eines eingebetteten

Speichers erlaubt. Die Speicherarchitektur erlaubt eine höhere momentane

Speicherkapazität

pro Port und ein besseres Puffern.

-

MMU-OPERATIONSTHEORIE

-

Es

wird nun die Operationstheorie der MMU besprochen. Mit der beschriebenen

MMU-Warteschlangenbildungsarchitektur wird jedes Paket, das an der

Switch Fabric ankommt, global an jeden Port über den IBR rundgesendet. Die

Architektur ist in 10 veranschaulicht. Eine Kopie

des Pakets wird nur gespeichert, wenn die lokale MMU dies so entscheidet.

Im Folgenden werden die lokalen Datenstrukturen beschrieben, wenn

Pakete gespeichert und weitergeleitet werden.

-

Der

Pack-FIFO besteht aus 8 einzelnen RAMs, die für acht Eingangsports reserviert

sind und folglich das parallele Ankommen von Paketen erlauben. Jedes

RAM enthält

einen Speicherplatz, der zwei Zellen tief ist. Zwei Zellen erlauben

eine Speicherung von 20 Worten oder 160 Bytes. Jeder FIFO wird verwendet,

um Pakete von dem gleichen Port zu speichern. Worte werden in dem

FIFO gesammelt, bis sich eine Zelle angehäuft hat, und diese wird dann

in den Speicher geschrieben. Der Vorgang des Packens von Worten

in Zellen ist unabhängig

von Paketgrößen. Dies

dient dazu, das Problem der vergeudeten "Löcher" im Speicher abzumildern,

wenn sich Paketgrößen von

Zellgrenzen unterscheiden. Es gibt insgesamt 32 logische FIFOs,

wobei jeder zu einem eindeutigen Port-COS-Paar gehört. Dies

garantiert eine Paketzustellung in der richtigen Reihenfolge und

die korrekte Reassemblierung von Zellen an dem Ausgang des Speichers.

-

Der

Paketpool-Schiedsrichter arbitriert die 8 Packer-FIFOs für den Schreibzugriff

auf den Hauptspeicher (Paketpool) auf eine Round-Robin-Weise. Nur

FIFOs mit einer bereitstehenden vollständigen Zelle oder ein FIFO,

der abgelaufen ist (timed out) (siehe Abschnitt zum Zeitüberwachungsmechanismus)

dürfen

den Zugriff beenden.

-

Ein

FreeQ ist ein Zeiger auf die im Augenblick freie Zelle (oder Block,

was später

noch diskutiert wird), in die eine neue Zelle geschrieben werden kann.

Eine freie Warteschlange (free queue) für alle zur Verfügung stehenden

Speicherzellen wird von dem LLA verwaltet.

-

Transaktions-Warteschlangen

(XQ) stellen ein Array dar, das 8 Warteschlangen enthält, eine

für jede COS.

Die Größe jeder

Warteschlange ist programmierbar. Jeder Warteschlangeneintrag zeigt

auf den Kopf eines Pakets in dem Speicher, und der Rest des Pakets

wird durch eine Linkliste (link list; Verbindungsangabenliste) in

dem LLA verwaltet. Die XQ verwaltet einen Zeitstempel, der jedem

Paket in dem Speicher einen Alterswert zuordnet. Pakete, die gemäß einem

programmierbaren Wert zu "alt" sind, werden fallen

gelassen. Die XQ hat ein Limit von 2048 Einträgen. Folglich kann jeder Ausgang

nur bis zu 2048 Pakete speichern (siehe PP).

-

Das

Linklisten-Array (LLA) ist ein Array, das ein 1-zu-1-Mapping zu

dem Paketpool-Speicher aufweist. Jeder Offset in dem Array entspricht

einer Zellenposition in dem Paketpool. In dem LLA sind Zeiger auf

andere Zellen gespeichert. Das LLA sieht ein praktisches Verfahren

für einen

Adressumweg (address indirection) vor, wenn Datenstrukturen manipuliert

werden. Das LLA verwaltet n + 2 Linklisten, wobei "n" für

die Anzahl an Paketen steht, die augenblicklich gespeichert werden,

und 2 die freie Warteschlange plus eine "Mülldeponie"-Warteschlange (graveyard queue) ist.

Das LLA verwaltet auch einen Referenzzähler für jede Zelle. Dies ist notwendig,

da die Zelle aktiv bleiben muss und nicht in die freie Liste zurückkehren

darf, bis alle, die sich auf die Zelle beziehen, nicht mehr länger die

Zelle benützen

müssen.

-

Der

Paketpool (PP) ist ein 128 KByte SRAM, das für die Hauptspeicherung der

Ausgangspakete für diesen

Port benutzt wird. Bei einer Breite von 640 Bits besitzt er 1600

Einträge.

Die Größe dieses

RAM bestimmt letztendlich, wie viel gespeichert werden kann. Zum

Beispiel kann es aufgrund der XQ-Limits bis zu 2048 Pakete in Minimalgröße speichern,

aber es kann nur bis zu 82 Pakete in Maximalgröße (1518 Bytes) und nur 14

Pakete in Riesengröße (9 KBytes)

speichern.

-

Der

Ausgangs-Scheduler (EGS) bestimmt das Paket, das als nächstes aus

dem PIE übertragen

werden soll. Er befolgt die Prioritätsregeln, die in dem Sys tem

programmiert sind, und ruft ein Paket Zelle für Zelle gemäß den Informationen ab, die

von XQ und LLA geliefert werden.

-

Der

Entpacker (UPK; unpacker) ist ein Zwilling zu dem Pack-FIFO dahingehend,

dass er die Inkongruenzen zwischen Wort und Zelle in diesem System

auf dem Weg nach draußen

glättet.

Aber er unterscheidet sich, weil zu einem Zeitpunkt nur ein Port

bei 1/8 der Geschwindigkeit aus ihm lesen muss, so dass nur ein RAM

benutzt wird.

-

Das

MMU-Design ist eine reine Paket-Speicher-Weiterleitungs-Maschine. Die Notwendigkeit,

in das Paket hineinzuspähen,

ist beseitigt worden, um die Unterstützung von verschiedenen Protokollen

zu erleichtern. Die MMU unterstützt

die folgenden Paketformate: Minimalgröße-Pakete von 64 Bytes, Maximalgröße-Pakete

von 9 KBytes, einen Modul-Zellkopf und einen Präambel-Zellkopf. Außerdem ist

die Unterstützung

des Trunking und des Spiegelns nahtlos, da die MMU nur auf ein Port-Bitmap-Seitenbandsignal

reagiert, das auf dem IBR transferiert wird.

-

Der

Grundfluss eines Paketes ist folgendermaßen: das erste Wort des Pakets

wird auf dem IBR für den

Port m gesehen, angezeigt durch RXSTART für Port m, und die COS (Dienstklasse)

des Pakets wird festgestellt, was von dem Feld in dem Wort-Header-Bereich

angezeigt wird. Dieses Wort wird in das Packer-RAM des Ports m in

einem logischen FIFO gemäß der COS

gespeichert. Nachfolgende Worte werden in dem gleichen COS-FIFO

gespeichert, bis RXEND für

Port m erfasst wird.

-

Wenn

sich inzwischen in einem der COS-FIFOs für Port m eine Zelle (10 Worte)

angesammelt hat, ist die Zelle bereit, in das Paketpool-RAM zu gehen.

Es sei angemerkt, dass alle anderen Ports das Gleiche tun. Folglich

können

potentiell alle acht Ports zur gleichen Zeit eine Zelle haben, die

bereit ist, in den Speicher geschrieben zu werden. Der Paketpool-Schiedsrichter

gewährt

unter allen acht Ports bei jedem Takt Schreibzugriffe auf das RAM

in einer Round-Robin-Weise, und da acht Takte notwendig sind, um

eine Zelle anzuhäufen, ist

die Bandbreite ausreichend. Wenn eine Zelle bereit ist zu gehen,

verwendet der Paketpool-Schiedsrichter den FreeQ-Zeiger und schreibt

die Zelle in den Speicher. Eine Linkliste wird für das Paket aufgebaut (wenn dies nicht

schon bereits geschehen ist). Dann wird das LLA mit der neuen freien

Warteschlange und der neuen Paket-Linkliste aktualisiert. Dieser

Vorgang wird für

jede neue Zelle wiederholt.

-

Ein

RXEND wird erfasst und der Zeiger zu der Kopfzelle dieses Pakets

wird auf die XQ geschoben, zu der er gehört. Der Ausgangs-Scheduler

bemerkt, dass ein Paket in der XQ ist, das gemäß seinem Prioritätsalgorithmus

versorgt werden muss. Es teilt dies dem UPK mit, wobei er ihm die

COS-Nummer gibt.

Der UPK urteilt, dass es für

die Übertragung

bereit ist, holt den Zeiger von der Spitze der gegebenen COS aus

dem XQ und verwendet ihn, um die erste Zelle aus dem Speicher aus

dem LLA zu lesen. Der UPK legt die Zelle in dem FIFO gemäß dem Port-COS-Paar

ab, zu dem sie gehört.

TXSTART wird dem PIE bestätigt,

und im Falle von TXREADY werden die Worte auf den PIE für die Übertragung

getaktet.

-

Alle

Zellen von dem RAM werden für

das Paket abgerufen, bis EOP erscheint (was durch das Größenfeld

von der XQ angezeigt wird). Die Zeiger für jede Zelle werden von dem

LLA bereitgestellt, das gleichzeitig die Referenzzählung für diese

Zelle dekrementiert. Wenn die erneute Zählung Null erreicht, wird die

Zelle zurück

in die freie Warteschlange gestellt. TXEND wird bei dem letzten

Wort bestätigt.

Der Entpack-FIFO stellt die Zelle gemäß dem Port-COS-Paar, zu dem sie

gehört,

in den FIFO.

-

Es

sind mehrere Szenarien möglich.

Ein Szenarium ist auf mehrere Pakete gerichtet, die an Nichtzellgrenzen

enden. Es sei zum Beispiel angenommen, dass für die gleiche Port-COS ein

weiteres Paket, z.B. B, direkt nach dem obigen Beispiel ankommt.

Es beträgt

81 Bytes. Sofort danach kommen zwei weitere Pakete an, z.B. C und

D, die ebenfalls jeweils sowohl 81 Bytes als auch N Bytes aufweisen.

-

Nach

81 Bytes (oder 10 Worten) beim Empfangen von B wird ihm eine Zelle

in dem PP gegeben, und ein Eintrag dafür wird in dem LLA erstellt.

Nach 1 Byte von B und 72 Bytes von C wird eine weitere Zelle gewährt und

zusammen werden sie in den Speicher geschrieben. Ein entsprechender

Eintrag in dem LLA wird modifiziert, um die Verknüpfung zu

der Zelle herzustellen, die in 1 verwendet ist. Da RXEND für das Paket

B empfangen worden ist, wird für dieses

ein Eintrag in einer COS-Warteschlange in der XQ erstellt. Der EGS entscheidet,

dass das Paket B übertragen

wird. Er ruft die erste Zelle aus dem Speicher ab und der UPK platziert

diese in seinem FIFO. Wenn 81 Bytes von B übertragen sind, ruft der EGS

die nächste

Zelle für

das Paket B ab und platziert diese in dem gleichen Port-COS-Entpack-FIFO.

-

Dann

wird 1 Byte von B übertragen.

Während

dieses Vorgangs beendet auch das Paket C sein Ankommen. C wird als

Zellen in dem Speicher gespeichert und Einträge werden in dem XQ mit einem

Offset-Wert von 1 erstellt. Die Referenzzählung für die Zellen, in denen B+D

und C+D gespeichert sind, wird 2 sein. Da er den neuen Eintrag für C in der

XQ bemerkt, kann der EGS/UPK den Rest von C (da ein Teil davon bereits über B ausgelesen

wurde) in den Entpack-FIFO holen, wenn der Übertragungsvorgang den FIFO

auf einen vorbestimmten Schwellwert entleert. Nun kann C ausgesendet

werden. Schließlich

werden Teile von D in dem Entpack-FIFO, in dem PP RAM und in dem

Pack-FIFO zurückgelassen.

-

Ein

zweites Szenarium ist auf Zeitüberwachungsmechanismen

(time out mechanisms) ausgerichtet. Nun wird angenommen, dass das

Paket D das letzte für

diese Port-COS ist und nicht an einer sauberen 80-Byte-Grenze endet.

Einige Bytes davon sitzen in dem Pack-FIFO, mehrere Zellen in dem

PP und 64 Bytes davon sitzen in dem Entpack-FIFO. Wenn an dieser

Port-COS nach der Zeit TLeeren (Tflush) kein Paket ankommt, wird dem Inhalt

des Pack-FIFO grünes

Licht signalisiert, um in das RAM zu gehen. Und es wird aufs Geratewohl

eine Zelle in dem Speicher mit den restlichen Bytes einnehmen. Und

ein Eintrag wird für

D in der XQ erstellt. Dieser "Entleerungs"-Timer-Mechanismus

("flush" timer mechanism)

wird dazu verwendet, stagnierende FIFO-Daten zu verhindern. Der

XQ-Eintrag für

D wird einen Offset von 2 haben, und wenn einmal ein Eintrag in

der XQ für

D erstellt ist, dann wird der EGS in der Lage sein, das Paket aus

dem RAM gemäß den oben beschriebenen

Schritten abzurufen.

-

Wenn

der Ausgangs-MAC überlastet

ist, (d.h. einige Ströme

mit hoher Bandbreite reißen

den Port an sich, oder TXREADY wird nie beobachtet), kann das Paket

D im Speicher gefangen sein. Es gibt zwei Handlungsweisen: 1) Im

Falle einer Überlastung

des Pack-FIFO wird TLeeren eine spezielle

Bedingung auslösen

und es den restlichen Bytes des Pakets D erlauben, dass sie in den Speicher

geschrieben werden können.

2) Wenn der Port untätig

ist, wird das Paket nach der Zeit TFallenlassen (Tdrop) als zu alt betrachtet und wird fallen

gelassen, und zwar sowohl von dem PP als auch möglicherweise von dem Entpack-FIFO, wenn es teilweise

auch dort gespeichert ist. Das Alter des Pakets wird von seinem

Zeit-Tick-Feld in der XQ bestimmt.

-

Ein

drittes Szenarium umfasst das Verhungern oder die Überindizierung

(over-subscription) der Ports. Im Falle der Überindizierung oder einer schlechten

Verbindung werden sich die Pakete schnell in dem PP ansammeln, und

wenn ein Schwellwert in der XQ erreicht ist, wird der Rückstau an

alle Anstoß gebenden

Ports bestätigt,

um einen RÜCKSTAU-Zustand

anzuzeigen. Dies erfolgt durch ein Kreditierungssystem (crediting system)

auf dem MR. Wenn die Pakete in der XQ für über die Zeit TFallenlassen hinaus

bleiben, werden sie fallen gelassen.

-

Im

Allgemeinen wird keinem Paket ein Eintrag in der XQ erlaubt, wenn

es unvollständig

ist, aufgrund von Verfall fallen gelassen wird oder aufgrund von

Mangel an Pufferung fallen gelassen wird. Ein Paket verlässt, wenn

es einmal einer Port-COS zugewiesen ist, niemals diesen Port-COS-Strom.

Dies gilt für

das Leben des Pakets in dem System, ungeachtet dessen, in welchem

physikalischen RAM es gespeichert ist. Da jedes Paket einer Port-COS

zugewiesen wird und jedes Schreiben in den Speicher nur von einer

Port-COS erfolgt, wird keine Zelle in dem Speicher zwei Pakete von

unterschiedlichen Port-COSs enthalten. Da die Pakete eine Minimalgröße von nicht

weniger als 64 Bytes haben müssen,

können

bei einer gegebenen Zellengröße von 80 Byte

nie mehr als drei Pakete in der gleichen Zelle gespeichert sein.

Hierbei ist TFallenlassen > TLeeren und

deshalb wird kein Ereignis, bei dem ein Paket fallen gelassen wird,

das Löschen

der Entpack-FIFOs benötigen.

-

NACHRICHTENRINGPROTOKOLL

-

Der

Nachrichtenring wird ein Token-Passing-Protokoll mit einigen Einschränkungen

bezüglich

der Token-Haltezeit (token holding time) verwenden, um eine Fairness

bei der Bandbreitenzuweisung zu garantieren und um die maximale

Zeit einer Station, für

die diese ein Token gewährt

bekommt, wenn sie eines benötigt,

zu bestimmen. Der Ring selber ist ein 33-Bit-Bus. Die Bits [31:0]

enthalten ein 32-Bit-Nachrichtenwort, und das Bit [32] ist das Token.

Jeweils zu einer Zeit ist entweder eine Null oder ein Token auf

dem Ring. Nachrichten bestehen aus einem Wort bis drei Worten; das

erste Wort der Nachricht beschreibt den Nachrichtentyp, der auch

die Nachrichtenlänge

impliziert. Ein Token-Bit ist nur immer an dem letzten Wort einer

Nachricht angehängt.

-

Alle

Nachrichten beginnen mit einem gemeinsamen Format, das ein erstes

Wort einer MR-Nachricht besitzt. Der Sechs-Bit-Opcode spezifiziert

den Nachrichtentyp und spezifiziert implizit die Nachrichtenlänge. Die

Fünf-Bit-Zielstation kommt

als nächstes,

dann die Fünf-Bit-Quellenstation

(diejenige, von der die Nachricht stammt), und schließlich ein

16-Bit-Nachrichtenabhängiger

Abschnitt. Einige Nachrichten haben ein zweites und eventuell ein

drittes 32b Datenwort, das Dinge wie Speicheradressen, Lesedaten

und Schreibdaten enthält.

-

Bestimmte

Nachrichten werden als eine geteilte Transaktion behandelt; dies

bedeutet, dass eine Anforderung von einer Station generiert wird,

und einige Zeit später,

vielleicht nachdem viele andere Nachrichten durch den Ring gewandert

sind, schickt die antwortende Station eine Bestätigungsmeldung zurück.

-

KONTOFÜHRUNGSBLOCK

-

Ein

anderer Abschnitt des MMU ist ein Kontoführungsblock (ACT; accounting

block). Diese Logik akzeptiert einen Strom von 64b Worten bei der

Kerntaktfrequenz von dem MAC, zusammen mit gewissen Seitenbandinformationen,

die von dem PIE generiert werden. Es gibt keine direkte Fähigkeit,

den Strom an Worten, der von dem MAC kommt, anzuhalten. Alle Pakete

müssen

angenommen werden (obwohl sie vielleicht später aus Mangel an Kapazität fallen

gelassen werden). Der Block ist auch dafür verantwortlich, Ressourcen zu

verfolgen, die von Paketen verwendet werden, die an diesem Eingang

angekommen sind, und anzufordern, dass der MAC in einen PAUSEN-Zustand

eintritt oder aus diesem austritt, je nachdem, wie dies angemessen ist.

-

Der

ACT verwaltet einen 16-Bit-Zähler,

der die Anzahl an OktByte-Worten

anzeigt, die ein gegebener Eingang in die MMU abgefeuert hat und

voraussichtlich Ressourcen erschöpfen

wird. Der Name des Registers ist MMU_REG_IngressWord Count. Es wird

auf Null zurückgesetzt

und jedes Mal dann inkrementiert, wenn PIE ein gültiges Word auf dem IBR sendet

(wie von dem PIE_mmu_vf-Bit angezeigt ist). Da Okt-Worte aus welchen

Gründen

auch immer austreten oder fallen gelassen werden, wird die Zählung dieser

OktByte-Worte gelegentlich über die

MR-IngressCredit-Nachricht zurück

zu dem Eingang geschickt und von der Zählung der ausstehenden Worte

subtrahiert.

-

Somit

geht diese Zählung

im Laufe der Zeit hoch und runter. Wenn die Zählung zu hoch ist, wird der Eingang

den MAC bitten, eine PAUSE an seine Verknüpfungspartner zu schicken,

um den Verkehr zu verlangsamen, der in den Chip eintritt. Wenn die

Eingaberate fällt

und sich wieder in vernünftigeren

Grenzen bewegt, wird der ACT den MAC bitten, den PAUSEN-Zustand

zu verlassen. Das Verhalten ist in 11 gezeigt.

Obwohl der MAC das Anfordern eines jeden PAUSEN-Timer-Wertes von

0x0000 bis 0xFFFF erlaubt, benutzt der ACT-Block immer nur die beiden

Werte 0x0000 oder 0xFFFF. 0xFFFF wird verwendet, wenn die PAUSE

angefordert wird, und 0x0000 wird verwendet, um anzufordern, dass

die PAUSE aufgehoben wird. Es ist möglich, dass der PAUSEN-Zustand,

in den er für

die niedrigere Hysteresegrenze eingetreten ist, trotzdem 64K Zyklen lang

nicht erhalten wird. In diesem Fall wird die ACT-Einheit den MAC bitten, eine weitere

PAUSEN-Anforderung zu senden, um zu gewährleisten, dass der PAUSEN-Zustand

aufrechterhalten wird. Dies ist ebenfalls in 11 gezeigt.

-

EINGANGSBUSRING

-

Das

Eingangsbusring-(IBR)-Modul ist relativ einfach und besitzt nur

ein paar Zwecke. Erstens werden die Eingangsbusse getaktet, bevor

die Daten zu der nächsten

Station weitergeleitet werden. Dies vereinfacht das Top-Level-Timing, da der Pfad

von Punkt zu Punkt ausgehend von benachbarten Stationen auf dem

Ring geht. Zweitens ist der IBR dort, wo das Port-Umordnen stattfindet.

Das heißt,

die Eingangsbusse werden eine Position weitergeschoben, bevor sie

auf den Ausgangsbussen hinausgesendet werden. Dies erlaubt es den Stationen,

eine einheitliche, sich nicht überlappende

Busverdrahtung zu besit zen, und dennoch immer noch eine aneinander

angrenzende Platzierung auf dem höchsten Level zu haben. Drittens

implementiert der IBR eine Leistungsoptimierungsstrategie. Während jedes

Wort an einem Eingangsbus ankommt, wird seine Ausgangs-Map inspiziert.

Wenn keine stromabwärtige

Station dieses Wort benötigt,

wird der Ausgangsbus konstant gehalten, mit Ausnahme des gültigen Bit

(valid bit), das falsch gesetzt wird.

-

Jedes

der Bits der acht Stränge

auf dem IBR besitzt eine fest zugewiesene Bedeutung. Obwohl es neun

Stationen auf dem IBR gibt, gibt es aufgrund der "Flügel"-Topologie des "Rings" nur acht Stränge im Querschnitt.

Im Hinblick auf alle Stationen befinden sich vier Stationen stromaufwärts und

vier stromabwärts. Jede

Station registriert ihre eigenen Ausgaben, wodurch verhindert wird,

dass so viele Signale den ganzen Weg um den Chip herum in einem

Zyklus gesendet werden müssen.

Stattdessen wird dies ersetzt durch die Komplexität, von einer

Station zu jedem anderen Paar von Stationen eine andere Latenzzeit

zu haben. Die unterschiedlichen Bits jeder Leitung sind exakt die

gleichen Informationen, die von dem PIE-Block generiert werden.

Als eine Leistungsoptimierung kann eine Station alle Bits eines

Busses konstant halten und ein FALSCHES "gültiges" Bit fortpflanzen,

wenn entweder das ankommende Wort nicht gültig ist oder wenn die Station feststellt,

dass die Ausgangsport-Map

keine stromabwärtigen

Ziele aufweist. Jede Station auf dem Ring besitzt acht Eingangsbusse

und acht Ausgangsbusse; vier laufen im Uhrzeigersinn, vier laufen

im Gegenuhrzeigersinn.

-

12 zeigt,

wie eine Station aussieht, während 13 zeigt,

wie die Ports jeder Station miteinander in Verbindung stehen. Es

sei angemerkt, dass sich zwar das logische Mapping von Ports zu

Eingangsbussen an jeder Station ändert,

aber die Topologie von Eingängen

zu Ausgängen

konstant bleibt. Dies bedeutet, dass nur ein Layout benötigt wird.

-

Die

Fähigkeit,

ein einziges Layout zu verwenden, ist wichtig für die Erfindung. Diese Topologie

bedeutet, dass Stationen, die sich auf dem Ring nebeneinander befinden,

auf dem physikalischen Chip benachbart sein können und ohne irgendeinen verschwendeten

Raum zwischen ihnen aneinander anliegen können, um sie miteinander zu

verbinden. Jede andere Topologie würde das Verschwenden von Raum

zwischen physikalischen Blöcken

erfordern, um die Ausgänge

eines Blocks mit den entsprechenden Eingängen des benachbarten Blocks

zu verbinden. Dies erleichtert auch das Testen, da jede "Kachel" des IBR gleich ist.

Es sei auch angemerkt, dass der Port 0 in 13 in

beide Richtungen läuft,

während

die anderen Ports alle durch die Station hindurchwandern oder an

dieser enden. Dies liegt daran, dass Station 0 die Quelle für die Eingang-O-Daten

ist. Ein 4-Bit-Identifizierer ist jeder Station auf dem Ring gegeben,

damit sie ihre Identität

kennt.

-

NACHRICHTENRING

-

Der

Nachrichtenring (MR) beruht auf dem folgenden Protokoll. Zu anfangs

bei der Rücksetzung

gibt es kein Token. Nachdem ein paar Zyklen vergangen sind, wird

die Station 0 ein Token prägen

und dieses auf den Ring schicken. Dieses Token-Wort wird weiterhin

zirkulieren, bis eine Station Bedarf hat, eine Nachricht zu senden.

Solch eine Station wird warten, bis sie an ihrem Eingangsbus ein

Token ankommen sieht. Da dieses Token mit dem letzten Wort der ankommenden

Nachricht verknüpft

ist, wird die Station die Bits [31:0] an ihren MR-Ausgangsport weiterreichen,

aber sie wird das Token-Bit entfernen. In dem nächsten Zyklus wird die Station,

die sich gerade das Token gegriffen hat, damit beginnen, irgendwelche

Nachrichten ausströmen

zu lassen, die sie ausströmen

lassen möchte,

was den unten aufgeführten

Bedingungen unterliegt. Wenn die Station das Aussenden von Nachrichten

beendet hat, setzt sie das Token-Bit ihres Ausgangsbusses bei dem

letzten Wort der letzten Nachricht auf "1".

-

Es

gibt drei Klassen von Nachrichten: 1) ReadRegister (Register lesen),

WriteRegister (Register schreiben), ReadMemory (Speicher lesen),

WriteMemory (Speicher schreiben); 2) ReadRegisterACK (Bestätigung für Register

lesen), WriteRegisterACK (Bestätigung

für Register

schreiben), ReadMemoryACK (Bestätigung

für Speicher

lesen), WriteMemoryACK (Bestätigung

für Speicher

schreiben); und 3) IngressCredit (Eingangsgutschrift). Nur die Station,

die mit der Verbindung zu einer CPU verknüpft ist, kann Nachrichten des Typs

(1) senden. Außerdem

kann nur eine solche Nachricht zu jeweils einem Zeitpunkt ausstehen. "Ausstehen" bedeutet, dass die

Nachricht des Typs (2), die eine Nachricht des Typs (1) vervollständigt, von

dem Sender der Nachricht des Typs (1) noch nicht empfangen worden

ist. Eine Station sendet eine Nachricht des Typs (2) nur in Reaktion

auf eine Nachricht des Typs (1).

-

Während einer

Token-Besitzzeit kann nur jeweils eine Nachricht von jeder der drei

Klassen gesendet werden. Das hat die folgenden Konsequenzen. Die

mit der CPU verbundene Station kann das Token für höchstens vier Zyklen halten,

da sie einen WriteMemory-Befehl in drei Zyklen und eine IngressCredit-Nachricht

in einem Zyklus senden kann. Obwohl sie eine Nachricht des Typs

(2) in Reaktion auf eine Anforderung des Typs (1) generieren kann,

wird dies nicht in der gleichen Token-Haltezeit passieren. Andere

Stationen werden das Token ebenfalls für höchstens vier Zyklen halten,

da sie eine ReadRegisterACK-Nachricht in drei Zyklen und eine IngressCredit-Nachricht

in einem Zyklus senden können.

Mit neun Stationen auf dem Ring (die mit der CPU verbundene Station

plus acht XAUI-Ports) wird ein Token höchstens 15 Takte brauchen,

bis es einen kompletten Kreislauf durchlaufen hat. Dies liegt daran,

weil während

eines Zyklus des Token immer nur eine Typ-(1)- und eine Typ-(2)-Nachricht erzeugt

werden kann, und deshalb benutzen zwei Stationen jeweils vier Zyklen

und sieben Stationen benutzen jeweils einen Zyklus.

-

PACKER

-

Der

Zweck des Packer-(PK)-Blocks bzw. der Packer-Einheit liegt darin,

einen Strom von 64-Bit-Worten von jeder der acht anderen Stationen

anzunehmen. Die Ausgangsport-Map, die jedem Paket zugeordnet ist, wird

dazu verwendet, zu bestimmen, welche Pakete von dem Ring durch eine

gegebene Station abgelesen werden sollen. Da die Datenworte von

einem gegebenen Eingang über

den IBR ankommen, wird jeder Strom in 640b "Zellen" assembliert. Wenn eine Zelle vollständig ist,

wird sie innerhalb von 8 Taktzyklen zu dem PP (Paketpool) transferiert.

Die acht Packungseinheiten (eine entsprechend jedem Eingang) führen untereinander selber

unter Verwendung einer strengen Priorität die Arbitrierung durch, um

Zugriff auf den PP zu bekommen. Da jede Zelle zehn Worte enthält und ein

Paket in einer Minimalgröße aus nur

acht Worten bestehen kann, ist es möglich, mehrere Paketfragmente

in einer Zelle zu haben.

-

14 zeigt

einige mögliche

Fälle,

wie Pakete in einer Zelle gruppiert sein können. Jedes kleine Kästchen in

der Zelle repräsentiert

ein 8-Byte-Wort. Die Pfeile mit der Bezeichnung "A", "B" oder "C" oberhalb

davon zeigen Pakete. Die grau hinterlegten Kästchen zeigen unbenutzte Abschnitte

von Zellen; die Gründe

dafür werden

weiter unten noch aufgeführt.

Die halbfetten Balken zeigen die Grenzen eines Pakets. Es sei angemerkt,

dass eine Zelle Fragmente von bis zu drei verschiedenen Paketen

enthalten kann, und dass eine Zelle höchstens zwei Grenzen zwischen

Zellen enthalten kann. Pakete sind aufgrund der toten Worte in den

grau hinterlegten Kästchen

nicht notwendigerweise in einer Zelle zusammenhängend.

-

Die

grau hinterlegten Kästchen

in 14 können

aus etlichen Gründen

entstehen: ein Fall wie #2 kann entstehen, wenn ein Eingang das

Senden von Paketen für

eine Weile stoppt; schließlich

wird die PK-Einheit trotzdem die unvollendete Zelle einfach an die

PP-Einheit senden, um das Stranden des Pakets "A" in

der PK-Einheit zu verhindern. Andere graue Kästchen können auftreten, wenn die MAC-Einheit

eine Löschanforderung

signalisiert, nachdem das Paket bereits gestartet ist. Statt all

die Zeiger zurückzusetzen

und dergleichen, signalisiert die PK-Einheit einfach, dass die damit

verbundenen Worte tot sind. Ein letzter Grund für grau hinterlegte Kästchen ereignet

sich, wenn die PK-Einheit

versucht, ein Paket in das LLA zu schreiben und ein oder mehrere

Fragmente aufgrund von irgendeiner Art von Ressourcenbeschränkung nicht

erfolgreich geschrieben werden können.

-

Die

Funktion des Packens ist, Bandbreite zu sparen und die engen IGB-Bahnen geschwindigkeitsmäßig an die

breite PP-Schnittstelle anzupassen. Wenn die PK-Einheit nicht mehrere

Paketfragmente in einer Zelle erlauben würde, könnte es zu einer unglaublichen

Insuffizienz bei der Speicherbenutzung und der Bandbreite kommen.

Wenn zum Beispiel der Verkehr gänzlich

aus 88-Byte-Paketen besteht, würde

ein Paket zwei ganze Zellen benötigen,

von denen nur 11 der 20 Worte belegt wären (55% Ausnutzung).

-

LINKLISTEN-ARRAY

-

Der

Linklisten-Array-Block ist das Linklistengehirn der MMU. Es führt die

folgenden Funktionen durch: es akzeptiert Schreibanforderungen von

dem PK für

jedes Paket, erstellt eine Linkliste für jedes Paket und regelt dessen

XQ-Eintragseinfügung, und

akzeptiert Leseanforderungen von dem UPK, befreit Zellen, die nicht mehr

länger

von Paketen benötigt

werden. Das LLA verwaltet auch eine 'freie Warteschlangen'-Linkliste, verwaltet Referenzzähler für jede Zelle

und führt

das Löschen

von Paketen aufgrund von expliziten oder impliziten Bedingungen

durch, gibt die gelöschten

Linklisten zurück

an die freie Warteschlange.

-

Zusammenfassend

gibt es 8 unterschiedliche Fälle,

in denen Pakete (A, B und C) in einer 80-Byte-Zelle gespeichert

werden können

(siehe 14).

-

-

Die

acht Fälle

sind entsprechend mit den 4 Signalen (sof0, sof1, eof0, eof1) von

dem PK codiert. Indem es diese decodiert, führt das LLA eine spezielle

Transaktion für

jeden Befehl durch.

-

Es

gibt zwei Lösch-Typen

in dem LLA: Explizit und implizit.

-

Explizites

Löschen:

Der PK bestätigt

das "Lösch"-Bit bei EOF, um

ein schlechtes Paket anzuzeigen. Demgemäß wird das LLA das Löschen durchführen.

-

Implizites

Löschen:

Der PK macht Schreibversuche, aber da der vorherige Schreibvorgang

verarbeitet wird, wird "voll" zutreffend. Somit

hat das LLA nicht mehr länger

den Platz, das Paket zu speichern und wird das Paket fallen lassen.

Im nächsten

Zyklus muss der PK realisieren, was geschehen ist. Er sollte die

restlichen Bytes PLUS die Bytes, die gerade dem LLA gegeben wurden,

verwerfen und zurückgutschreiben.