Beschreibung

Schaltungsanordnung zur Ansteuerung eines Umrichters

Die Erfindung bezieht sich auf eine im Oberbegriff des Patentanspruchs 1 angegebenen Schaltungsanordnung- insbeson¬ dere auf eine Schaltungsanordnung zur Steuerung einer Folge- freguenz und Einschaltdauer eines getakteten Schaltumrich- ters.

Eine Schaltungsanordnung zur Steuerung der Folgefrequenz und

Einschaltdauer wurde bereits in der Offenlegungsschrift

DE 41 05 464 AI vorgeschlagen.

Derartige Schaltungsanordnungen stoßen bei höheren Frequenzen an ihre Anwendbarkeitsgrenzen.

Aufgabe der Erfindung ist es, einen Steuerbaustein so auszu¬ bilden, das er für hohe Steuerfrequenzen bei einer ver¬ gleichsweisen geringen Eigenstromaufnahme geeignet ist.

Gemäß der Erfindung wird ein Umrichter nach dem Oberbegriff des Patentanspruchs zur Lösung dieser Aufgabe in der im kenn¬ zeichnenden Teil des Patentanspruchs 1 angegebenen Weise aus¬ gebildet.

Die Erfindung weist neben dem Vorteil, daß für die Schal¬ tungsanordnung ein geringer Platzbedarf benötigt wird, die weiteren Vorteile auf, daß in einem großen Stellbereich, ins¬ besondere für hohe Frequenzen ein geringer Strombedarf sowie eine kontinuierliche Strombegrenzung realisiert werden kann. Die Schaltungsanordnung bringt desweiteren den Vorteil mit sich, daß eine exakte umgekehrte Proportionalität zwischen der EingangsSpannung und den Impulsbreiten des Ausgangs- Signals gegeben ist. Die Schaltungsanordnung weist den Vorteil auf, daß die Fre¬ quenz und das Impuls/Pause Verhältnis des Ausgangssignals in sehr weiten Bereichen unabhängig voneinander variierbar sind.

Ein weiterer Vorteil der Schaltungsanordnung ist, daß mit Verringerung der Folgefrequenz der Stromverbrauch der angege¬ benen Schaltungsanordnung abnimmt und sich ein günstiger Wir- kungsgrad bei geringer Leistungsanforderung der Sekundärseite ergibt.

Eine weitere Ausgestaltung der Schaltungsanordnung ist, daß diese in einem integrierten Schaltkreis ausführbar ist und sehr wenig externe Komponenten benötigt.

Eine weitere Ausgestaltung der Schaltungsanordnung ist, daß diese temperaturkompensiert ist und im ungesättigten Betrieb arbeitet, wodurch sich ein Betrieb bei hohen Frequenzen mit geringer Verlustleistung und guter Temperaturstabilität ergibt.

Eine weitere Ausgestaltung der Schaltungsanordnung besteht darin, daß ein wirkungsvoller Schutz der Schaltungsanordnung während einer Leitphase über einen Eingangssensor vorhanden ist, der die Einschaltzeit umgekehrt proportional zur Ein¬ gangsspannung verkürzt.

Vorteilhafte Ausbildungen der Erfindung sind in den Unteran- Sprüchen angegeben.

Weitere Besonderheiten der Erfindung werden aus der nachfol¬ genden näheren Erläuterung eines Ausführungsbeispiels anhand von Zeichnungen ersichtlich. Es zeigen :

Fig. 1 einen bekannten Umrichter, Fig. 2 dazugehörige Pulsdiagramme,

Fig. 3 eine schematische Darstellung einer Schaltungsanord¬ nung zur Ansteuerung eines Umrichters, Fig. 4 dazugehörige Pulsdiagramme,

Fig. 5 eine weitere schematische Darstellung,

Fig. 6, 7, 8, 9 eine Detaildarstellung der in Fig. 3 abgebil¬ deten schematischen Darstellung der Schaltungsanord¬ nung, Fig. 10 einen Spannungsverlauf am Ausgang der Schaltungsan- Ordnung ohne Impulsverkürzung,

Fig. 11 einen Spannungsverlauf am Ausgang der Schaltungan¬ ordnung, Fig. 12 einen Spannungsverlauf am Ausgang der Schaltungsan¬ ordnung und Fig. 13 einen weiteren Spannungsverlauf am Ausgang der Schal¬ tungsanordnung.

Zum besseren Verständnis der Erfindung wird anhand der

Fig. 1 sowie der Fig. 2 die Funktionsweise eines Durchflußum- richters erläutert. Bei dem in Fig. 1 gezeigten Durchflußum¬ richter liegt die EingangsSpannung UE am Kondensator 1 und die AusgangsSpannung UA am Kondensator 9. Parallel zum Kon¬ densator 1 liegt eine aus der Primärwicklung 51 des Transfor¬ mators 5, der Drain-Source-Strecke des Feldeffekttransistors 4 und dem Meßwiderstand 2 gebildete Serienschaltung. Parallel zur Serienschaltung aus Meßwiderstand 2 und Drain-Source- Strecke des Feldeffekttransistors 4 liegt die Anordnung 3 zur RCD-Beschaltung. Zwischen der Sekundärwicklung 52 des Über¬ tragers 5 und dem Kondensator 9 liegt die Gleichrichterdiode 6. In einem auf die Gleichrichterdiode 6 folgenden Querzweig ist die Freilaufdiode 7 angeordnet. In einem Längszweig zwi¬ schen Freilaufdiode 7 und Kondensator 9 liegt die Drossel 8. Die Steuerelektrode des Feldeffekttransistors 4 ist an einen Treiber 11 angeschlossen. Der Meßwiderstand 2 liegt an einem Stromregler 10, am Ausgang des Umrichters befindet sich ein Spannungsregler 15 sowie ein Optokoppler 20. Der Stromregler 10 und der Optokoppler 20 sind über je eine Diode 16 bzw. 17 an den Eingang eines Oszillators 19 angeschlossen. Der Puls¬ generator 18 liegt mit einem Eingang am Eingang des Umrich- ters, d.h. an der EingangsSpannung UE. Ein weiterer Eingang ist mit dem spannungsgesteuerten Oszillator 19 verbunden. Über diesen Eingang erhält der Pulsgenerator 18 eine Takt-

Spannung UT mit variabler Frequenz. Der Pulsgenerator 18 erzeugt eine Folge von Impulsen Up, deren Folgefrequenz durch den spannungsgesteuerten Oszillator 19 vorgegeben ist und deren Einsehaltdauer umgekehrt proportional zur Eingangs- Spannung UE ist. Im allgemeinen liefert der Pulsgenerator 18 Pulse Up bestimmter Einschaltdauer tE. Die Wiederholfrequenz wird von dem spannungsgesteuerten Oszillator 19 entsprechend dem Arbeitspunkt des I-Reglers 10 oder des U-Reglers 15 über den Optokoppler 20 eingestellt. Im Grenzfall kann die der minimalen Periodendauer Tmin entsprechende maximale Frequenz durch die minimal realisierbare Einschaltdauer und den gewünschten Tastgrad bestimmt werden: f= γ/tE (3)

Dabei ist f die Wiederholfrequenz des Einschal i pulses, γ der Tastgrad und tE die Dauer der Einschaltpulse.

Bei einem Einschaltpuls mit einer Dauer tE = 0,5 μs und dem Tastgrad γ=0,5 ergibt sich eine Frequenz von 1 MHz. Die Dauer des Einschaltpulses hängt von der Eingangsspannung UE ab. Sie ist umgekehrt proportional der EingangsSpannung tE - 1/UE (4)

Die Änderung der Eingangsspannung UE ist bei dem Durchflußum¬ richter die dominante Störgröße. Beim idealisierten verlust¬ losen Umrichter gilt die Beziehung:

UA = UE-γ (5) Bleibt nach Einführung der Bezeichnung (4) das Produkt UE.tE konstant, so braucht bei einer Eingangsspannungsänderung die Frequenz nicht geändert zu werden, um die AusgangsSpannung UA konstant zu halten.

Die in Fig. 2 dargestellten Impulsdiagramme zeigen das prin¬ zipielle Verhalten des Umrichters bei verschiedenen Betriebs- zuständen.

a) In der Anlaufphase bzw. bei zu geringer AusgangsSpannung stellt der spannungsgesteuerte Oszillator VCO (19) die maxi¬ male Frequenz ein. Dies entspricht der minimalen Perioden¬ dauer Tj-^n der Taktpulse Uφ.

b) Bei der minimalen EingangsSpannung liefert der Pulsgenera¬ tor 18 den Einschaltimpuls Up mit maximaler Dauer ts^^.

c) Eine Erhöhung der EingangsSpannung hat eine Verkürzung der Einschaltzeit auf einen neuen Wert tgx zur Folge, ohne das sich dabei die Frequenz verändert.

d/e) Die beiden Diagramme zeigen die Frequenzreduzierung bei starker Entlastung oder bei Überlast und unveränderter Ein¬ gangsspannung UE. Es stellt sich die längere Periodendauer Tv bei gleichbleibender Einschaltzeit t£χ ein.

Fig. 3 zeigt eine schematische Darstellung einer Ausgestal¬ tung der erfindungsgemäßen Schaltungsanordnung. Diese Schaltungsanordnung ANSS zur Ansteuerung eines Umrich¬ ters setzt sich im wesentlichen aus den in einem Funktions¬ block VCO, einen spannungsgesteuerten Oszillator, und den in einem Funktionsblock PWM, einen Pulsweitenmodulator, angeord¬ neten Schaltkreisen zusammen.

Im einzelnen sind im Funktionsblock VCO folgende Schalt¬ kreise: FCI: Frequency Control Input, VCOS: VCO-Switch, CSVCO: Current Source VCO,

TCCS: Temperature Compensated Current Source, VIC: Voltage to Current Converter sowie CFFVCO: Komparator CO, ECL-Flip-Flop ECL-FF1.

Im Funktionsblock PWM sind es die Schaltkreise: CSPG: Current Source Pulsgenerator, PWMT: Pulsweitenmodulator Trigger, PWMS: Pulsweitenmodulator Switch, HLR: High-Low Referenz und einen Schaltkreis für

FFPWM: ECL-Flip-Flop ECL-FF2, Pulsweitenmodulation PWM.

Einzelne Schaltkreise sind mit Steueranschlüssen versehen. Über diese Steueranschlüsse ist die Frequenz sowie das Impuls/Pause Verhältnis des Ausgangssignals

(Durchschaltesignals) Up beeinflußbar. Das Ausgangssignal Up weist die Spannungspegel MOSL, MOSH auf. Über den Steueran¬ schluß CVCO, IREG, OPTO, I/F kann einerseits auf die Frequenz des Ausgangssignals Up und andererseits über die Steueran- Schlüsse CPG und PG auf das Impuls/Päüse Verhältnis des Aus¬ gangssignals Up Einfluß genommen werden. Über den Eingang I/F kann der Gesamtstromverbrauch der Schaltungsanordnung ANSS variiert werden.

Über die an den einzelnen Schaltkreisen VCOS, FCI, VIC sowie PWMS, CSPG angedeuteten Anschlüsse kann auf das Ausgangs- signal Up der Schaltungsanordnung ANSS wie nachfolgend zusam¬ mengefaßt Einfluß genommen werden:

CVCO: Kondensatoranschluß zur Bestimmung der maximalen Taktfrequenz, IREG: Stelleingang zur Reduzierung der Frequenz mit eingestellter interner Schwelle durch die mit VA bezeichnete Referenzspannung. OPTO: Stromstelleingang zur Reduzierung der Frequenz.

I/F: Einstellung der Maximalfrequenz in Verbindung von CVCO. PG: Vorsteuerung/Reduzierung der "On-Zeit" des

Ausgangssignals Up, CPG: Kondensatoranschluß zur Bestimmung des maximalen Impuls/Pause Verhältnisses.

Die in Fig. 3 gezeigte schematische Schaltungsanordnung ANSS ist bei einem geringen Leistungsverbrauch mit hohen Frequen¬ zen steuerbar, wobei über weite Bereiche die Frequenz und das Tas Verhältnis (Impuls/Pause Verhältnis) veränderbar sind. Um den Leistungsverbrauch beispielsweise bei schnellen Tran¬ sistoren mit einer Transitfrequenz von 6 GHz gering zu

-_

WO 96/13893

7 halten, arbeiten die Transistoren in der Schaltungsanordnung im ungesättigtem Betrieb. Um die Frequenz und das Impuls/Pause Verhältnis des Ausgangssignals Up, gebildet durch die differenziellen Spannungspegel MOSL und MOSH, in einem weiten Bereich zu ändern und temperaturunabhängig zu machen, wird mit über mehrere Dekaden veränderbaren, tempera¬ turkompensierten Strömen gearbeitet. Zur Ausführung von Speicher- und Steuerfunktionen werden Kontrollschaltungsteile CFFVCO, FFPWM benutzt die Komparator und Flip-Flop Eigen- Schäften besitzen und konstante differenzielle ECL-Ausgangs- pegel liefern.

Um bei Verringerung der Frequenz eine Anpassung der Eingangs- ströme des Kontrollschaltungsteiles zu erreichen, wird dessen Eingangsimpedanz ständig angepaßt.

Das Prinzip der in Fig. 3 dargestellten Schaltungsanordnung ist nachfolgend beschrieben. Verweise auf die in Fig.4 sche¬ matisch dargestellten Spannungsverlaufe verdeutlichen zusätz¬ lich das Zusammenwirken der einzelnen Schaltkreise. Eine Triggerung des Pulsweitenmodulators PWM erfolgt über den Schaltkreis CFFVCO im VCO, d.h. die Frequenz des Ausgangs¬ signals Up am Ausgang der Schaltungsanordnung ANSS wird vom spannungsgesteuerten Oszillator VCO angegeben. Eine Variation des Impuls/Pause Verhältnisses wird vom Pulsweitenmodulator PWM bewirkt.

Liegt beispielsweise keine Stellanforderung über die Anschlüsse OPTO, IREG am Schaltkreis FCI des spannungsgesteu¬ erten Oszillators VCO und keine Stellanforderung am Anschluß PG des Schaltkreises CSPG im Pulsweitenmodulator PWM vor, so weist das Ausgangssignal Up, der Schaltungsanordnung ANSS eine maximale Frequenz VCOfmax auf. Diese maximale Frequenz VCOfmax ist über den Stelleingang I/F des Schaltkreises VIC sowie über den Stelleingang CVCO an der Schaltungsanordnung VCOS einstellbar. Mit einem Widerstand R, der am Anschluß I/F angeordnet ist, ist über den Stromfluß durch den Widerstand R die Frequenz des spannungsgesteuerten Oszillators VCO eben¬ falls einstellbar.

Im Pulsweitenmodulator PWM wird durch Änderung der über einen Widerstand am Anschluß PG angelegten Spannung Ue das Impuls/Pause Verhältnis des Ausgangssignals Up beeinflußt. Eingeleitet wird die Variation des Impuls/Pause Verhältnisses des PWM bei Erreichen einer oberen Referenzspannung VF durch den am Anschluß CVCO angeordneten Kondensator (Fig. 4a, Punkt 1) . Mit einem am Anschluß CVCO angeordneten Kondensator Cl wird eine erste Zeitvariable Tl bestimmt. Der spannungsge¬ steuerte Oszillator VCO leitet über eine Triggerung des Schaltkreises FFPWM eine Entladung des am CPG Anschluß ange¬ schlossenen zweiten Kondensators C2 (Fig.4b, Punkt 4) ein. Mit der Entladung des Kondensators C2 wird eine zweite Zeit¬ variable T2 bestimmt. Dieser Entladevorgang, gesteuert durch die Schaltkreise PWMS und PWMT ist durch die Wahl der Stellgröße C2 am Anschluß CPG am Schaltkreis PWMS so bemessen, daß die maximal gewünschte Impulsweite vorgegeben ist. Bei Erreichen einer unteren Refe¬ renzspannung VG (Fig.4b, Punkt 5), die einen unteren Umschaltpunkt festlegt, leitet der Pulsweitenmodulator PWM die Impuls-Pause des Ausgangssignals Up der Ansteuerschaltung ANSS ein. Die Entladung des die zweite Zeitvariable T2 beein¬ flußenden Kondensators am Anschluß CPG ist so bemessen, daß diese schneller abläuft als die Entladezeit des die erste Zeitvariable Tl beeinflussenden Kondensators durch den span- nungsgesteuerten Oszillator VCO (Fig.4a, Punkte 1, 2 und Fig.4b, Punkte 4, 5). Die Spannung am Anschluß CPG des PWM verweilt an der oberen Umschalteschwelle VF (FIG.4b, Punkt 6, 1 ) bis der VCO durch einen Triggerimpuls ausgehend vom Schaltkreis CFFVCO eine erneute Entladung der die erste sowie zweite Zeitvariable Tl, T2 bestimmenden Kondensatoren Cl, C2 an den Eingängen CVCO und CPG einleitet. Der Kondensator C2 kann beschleunigt entladen werden und damit die zweite Zeitvariable T2 verkürzt werden, d.h. die "On-Zeit" des Ausgangssignals Up der Ansteuerschaltung ANSS verkürzt sich entsprechend der Höhe des an PG anliegenden

Potentials (Fig.4b, Punkt 4, 5; 8, 9; 15, 16) . Da das Signal der PWM-Schaltung an der oberen Schwelle der Referenzspannung

VF verharrt (Fig.4b, Punkt 6, 7; 13, 14), ist eine unabhän¬ gige Stellung der Pulsweite von der Frequenz des spannungsge¬ steuerten Oszillators VCO realisiert und eine Verkürzung jeweils über den Anschluß PG möglich. Die Anschlüsse IREG/OPTO ermöglichen eine Frequenzvariation des Ausgangssignales des spannungsgesteuerten Oszillators VCO (Fig. 4f) . Eine Stellanforderungen über beide Eingänge führt, beispielsweise zu einer linearen Reduzierung der Frequenz des Ausgangssignales Up, wobei die Pulseinschaltzeit dieser Fre- quenz erhalten bleibt (Fig. 4g) .

Da die Entladezeit der zweiten Zeitvariablen (PWM) nur ver¬ kürzt werden kann (durch Anschluß PG) , ergibt sich bei einer Stellanforderung über die Anschlüsse IREG und OPTO für das Puls-Pause Verhältnis eine weitere Reduzierung. Die Ablaufsteuerung mit variabler Frequenzeinstellung sowie variabler Einstellung der Pulsdauer ermöglicht eine Anpassung der Leistungsanforderung (Sekundärseite) am Ausgang des Umrichters. Die Kontrolle des Einschaltimpulses für einen zu steuernden Schalttransistor in Abhängigkeit von der EingangsSpannung Ue des Umrichters erfolgt über den Stelleingang PG. Der Stell- Vorgang über den Anschluß PG des Schaltkreises CSPG ist so bemessen, daß für die kleinste Eingangsspannung ein Schutz des Schalttransistors gewährleistet ist. Durch beispielsweise eine umgekehrt proportionale Verkürzung des Einschaltimpulses im Verhältnis zur EingangsSpannung ist dieser Schutz in einem weiten Bereich für größere EingangsSpannungen^ gegeben. Die EingangsSpannung des Umrichters und die Pulsdauer des Schalttransistors verhalten sich umgekehrt Proportional, wobei durch den sich am Anschluß CPG angeordneten Kondensator C2, der die Zeitvariable T2 des PWM bestimmt, ein integraler Verlauf der EingangsSpannung (Ue) des Umrichters berücksich¬ tigt wird (Feed-Forward-Regelung des Schalttransistors) . Die in Fig.4c und 4e gezeigten Spannungsverläufe geben das Impuls/Pause Verhältnis des AusgangsSignals Up bei maximaler Frequenz (VCO fmax, Fig.4a) wieder. Die Impulsdauer wird jeweils durch das Erreichen einer "unteren" Referenzspannung

VG bestimmt. Die Zeitvariable T2 ist kleiner (<)der minimalen Zeitvariablen Tl. Ausgelöst wird die Zeitvariable T2 jeweils bei Erreichen einer "oberen" Referenzspannung VF (FIG 4b, 4d, Punkt 7, 14) . Die in den Figuren 4f bis 4j wiedergegebenen Spannungsverläufe geben das Impuls/Pause Verhältnis des Aus¬ gangssignals Up bei einer verringerten Frequenz VCOfx des spannungsgesteuerten Oszillators VCO wieder. Fig 4h, 4j zeigt ein geringeres Impuls/Pause Verhältnis bei gleicher Stellan¬ forderung (vergleiche Fig 4b, 4g; 4d, 4i) am Stelleingang PG (PGV ax, PGV in) . Die Frequenz VCOfmax (Fig. 4a) kann über einen der Stelleingänge IREG oder OPTO am Schaltkreis FCI des VCO reduziert werden (Fig. 4f) .

In Fig. 5 ist eine schematische Darstellung der Schaltungsan- Ordnung zur Ansteuerung eines Umrichters abgebildet. Über einen dynamischen Triggereingang am Schaltkreis FFPWM wird ein in diesem angeordnetes ECL Flip-Flop ECL-FF2 gesetzt. Ein am Ausgang der Schaltungsanordnung FFPWM anliegendes Signal, schaltet die E ittter-Kollektor Strecke des in der Differenz- stufe Q28, Q29 des Schaltkreises PWMS angeordneten Tran¬ sistors Q28; Q25 übernimmt den Strom der Stromquelle SQ3. Der Kondensator C2 wird über die Stromquelle SQ3 , die am Emitter der Differenzstufe Q28, Q29 angeordnet ist entladen (siehe Fig.4 Punkt 4, 7, 14) . Die Entladung des Kondensators C2 erfolgt linear. Die Entladung kann entsprechend einer

Ansteuerung des sich am Emitter der Differenzstufe Q28, Q29 angeordneten Stromspiegels, gebildet aus den Transistoren Q32, Q31, variiert werden. Die Linearität der Entladung des Kondensators C2 bleibt dabei erhalten. Eine, die Entladung des Kondensators C2 beeinflußende Stellgröße Ue liegt dabei an einem Widerstand RUe, der an der Anode des als Diode betriebenen Transistors Q32 des Stromspiegels angeordnet ist. Die Zeit der Entladung des Kondensators ist dabei umgekehrt proportional der an dem Widerstand Rue anliegenden Stellgröße Ue (siehe Fig 4, Zeitvariable T2 zwischen den Punkten 4-5, 11-12). Die Entladung des Kondensators C2 wird beendet, wenn ein dem Spannungspotential entsprechendes Potential VG

W096/13893

11 erreicht ist (PWMT; Q21, Q24) . Über die in der Schaltungsein¬ heit PWMT angeordnete Differenzstufe Q21, Q24 erfolgt über den Kollektor des Transistors Q24 ein Resetsignal, das an die Schaltungseinheit FFPWM weitergeleitet wird. Das in der Schaltungsanordnung FFPWM angeordnetes Flip-Flop ECL-FF2 bewirkt ein Potentialwechsel des Ausgangssignals. Ein Pegel- Wechsel des ECL-Ausgangssignals bewirkt bei der in der Schal¬ tungseinheit PWMS angeordneten Differenzstufe Q28, Q29 ein Sperren des Transistors Q28. Eine weitere Entladung des Kon- densators C2 wird dadurch verhindert. Der Kondensator C2 wird jetzt auf eine "obere" Referenzspannung VF aufgeladen. Wäh¬ rend der Aufladephase des Kondensators C2 ist nur die an Basis/Kollektor des als Diode geschalteten Transistors Q19 angeschlossene Stromquelle SQ1 aktiv. Erreicht das Potential am Kondensator C2, das Potential der Referenzspannung VF, so wird wegen der größer dimensionierten Stromquelle SQ2 am Emitter von Q19 der Aufladevorgang beendet. Über den Emitter des als Diode betriebenen Transistors Q19 wird der Strom, der die Aufladung des Kondensators C2 bewirkt hat, nach Masse abgeleitet. Der Kondensator C2 befindet sich nunmehr in War¬ testellung, bis ein erneuter Triggerimpuls, der beispielswei¬ se von dem spannungsgesteuerten Oszillator VCO an den Funktionsblock PWM über E2 weitergereicht wird, eine erneute Entladung des Kondensators C2 einleitet.

In Fig. 6, 7, 8, 9 ist eine detaillierte Schaltungsanordnung der in Fig. 3 gezeigten schematischen Darstellung wiedergege¬ ben. Die Funktionsweise der Schaltungsanordnung ist nachfol¬ gend beschrieben: Am Anschluß I/F der Schaltkomponente VIC wird über die Tran¬ sistoren Q70, Q71 eine Spannungs-Stromwandlung vorgenommen. Durch eine Bufferschaltung gebildet durch die Transistoren Q65 ... Q71, Q215 ... Q217 und die Spannungsquelle VD, die als Band-Gap ausgebildet ist, wird erreicht, daß der durch die Transistoren Q70, Q71 extrahierte Strom, temperaturunab¬ hängig ist und sich dadurch die Frequenz über den Temperatur¬ bereich nicht ändert.

Der Strom, der im Kollektor von Q71 des Schaltkreises VIC fließt, wird dem Schaltkreis CSPG zugeführt. Der Strom, der im Kollektor von Q70 fließt wird dem Stromspiegel CSVCO Q200 ... Q204 zugeführt. Q200 ... Q204 bilden mit Q3 ... Qll den Stromgenerator für den frequenzvariablen Betrieb.

Über den VCOS, der durch die Transistoren Ql, Q2 gebildet ist, erfolgt die Umladung von CSVCO. An den Basen der Tran- sistoren Ql, Q2 liegt eine differenzielle Spannung an. Je nach Aussteuerung der Basen wird CSVCO über Q200 aufgeladen oder über Q3, Q4 entladen, da der Entladestrom, der in Q 204 generiert wird, im Verhältnis 2 : 1 gespiegelt wird (Transistoren Q9, Q10, Q3, Q4) . Die Transistoren Q8, Q7, Q6, Q5, Q201 dienen einer gewünschten Anpassung des Puls-Pause- Verhältnis von 56,37%. Der Verlauf der Spannung des CSVCO ist dreieckförmig und das Impuls-Pause-Verhältnis vollkommen unabhängig von der Größe des Stromes CSVCO, da die Strom¬ quellen im festen Verhältnis zueinander stehen. Die Größe der Dreiecksamplitude, die sich im CSVCO ergibt, wird durch die

Referenzspannungen VF und VG festgelegt, welche über die Transistoren Q124, Q122, Q80 bzw. Q125, Q123, Q81 dem PWMT und dem CFFVCO (Komparator/ECL-Flip-Flop-Frequenz) zugeführt werden. Über Q33 und Q35 liegen die Referenzspannungen an dem Komparator CO, ECL-Flip-Flop/Frequenz, welcher über Q42 die Spannung am VCO mit diesen Referenzspannungen vergleicht. Erreicht VCOS den oberen oder unteren Wert der Referenzspan¬ nung, erfolgt über Q41 bei Erreichen von VF-Reset oder bei Erreichen von VG über Q38-Set an dem Flip-Flop Q43, Q44. An den Flip-Flop Transistoren Q43, Q44 ergibt sich durch die

Wahl des Stromes in den Stromquellen Q51, Q52, Q53, Q54 und den Kollektorwiderständen von 3,3 K ein differentielles Signal von 320mV, welches über Q45 ... Q50 den Schalter Ql, Q2 umschaltet. Die Besonderheit der bisher beschriebenen Schaltkreise ergibt sich aus dem Aufbau der Eingangsschaltung, die über Q36, Q37, Q40 den Strom aus Spannungsquelle Q9, Q10 in die Eingangs-

stufen des Komparators spiegelt. Hier ergibt sich erfindungs¬ gemäß der Vorteil, daß der Eingangsstrom an der Basis von Q42 vom Strom im VCO-Umschalter Ql, Q2 abhängig gemacht wird und somit bei einer Frequenzvariation am Anschluß VCO im Verhält¬ nis 1:100 sich dieser Basisstrom um das gleiche Verhältnis verändert, wodurch die Darlingtonstufe Q42, Q39, Q41 in der Geschwindigkeit der VCO-Frequenz angepaßt wird und der sich ergebende Frequenzfehler durch den Basisstrom in Q42 gering gehalten wird.

Da die Stromquellen Q51 ... Q56 mit dem fest eingestellten Strom arbeiten, ist durch die Darlington-Eingangstransistoren Q33/Q34, Q35/Q38, Q42/Q41, Q42/Q39 die Impedanzanpassung an den VCO-Strom und die Umsetzung in konstante ECL-Pegel in den Kollektoren Q43, Q44 möglich.

Die Frequenzeinstellung erfolgt dabei durch folgende Schal- tungsausprägung: Bei den im Schaltungsbeispiel ausgeführten Spiegelverhältnis der Transistoren, ist die Maximalfrequenz des VCO durch den eingestellten Strom am Anschluß I/F, der Größe der Amplitude, VF - VG und die Größe des Kondensators am Anschluß VCO bestimmbar. Die Zeiten tl, t2, die Frequenz des VCO und das Puls-Pause-Verhältnis können wie folgt bestimmt werden:

0. 458 die Frequenz des VCO: • VCO [Hz] (8 ) tl + t2 Cv VcCoO ' R * : F

t2 das Impuls-Pause-Verhältnis: F = = 56.37% (9)

^ tl + t2

VF - VG = 0,6V Dreiecksspannungshub

VD = 1,26V (Band-Gap Spannung) Rj/p: Widerstand am Anschluß I/F fyco: Frequenz des spannungsgesteuerten Oszillators DR :Impuls- Pause Verhältnis

Eine Einstellung der Frequenz ist über die Anschlüsse IREG und OPTO am Schaltkreis FCI durchführbar, wobei die Frequenz des VCO verringert wird. Der Stromspiegel Q208, Q209 spiegelt im Kollektor von Q208 den aus den Anschlüssen IREG oder OPTO fließenden Strom so in den Stromspiegel Q200 ... Q204, daß sich der Strom von Kollektor Q208 und Q70 subtraktiv überlagern. Erreicht der Wert des Stromes von Kollektor Q208 im Betrag den Wert des Stromes von Kollektor Q70, wird der Stromspiegel Q200 ... Q204 stromlos und die Frequenz am Anschluß VCO ist Null. Folgender Zusammenhang ist dabei gegeben:

t -opto/ireg = 1. 26 ^ S^ ( 10 )

R T) J-opto J-opto IF ' ~

-vcoopco/irβg [Hz] (12)

C -1-opto/ireg -£-opto/ireg

tl0pto/ireg: Entladezeit des Kondensators CVCO am Anschluß

VCO bei Stellung an den Anschlüssen OPTO oder IREG

t^opto/ireg: Aufladezeit des Kondensators CVCO am Anschluß VCO bei Stellung an den Anschlüssen OPTO oder IREG

fVCO opto/ireg: Frequenz des VCO bei aktiven Anschlüssen

OPTO ODER IREG

Durch diese Art der Frequenzeinstellung ist ein großer Bereich der Frequenzvariation gegeben. In Figur 4 sowie Figur 10 bis 13 ist diesbezüglich der Zusammenhang grafisch darge¬ stellt. An einem integrierten Ausführungsbeispiel ist eine Frequenzvariation von mehr als 1 : 700 realisierbar.

Die Eingänge OPTO und IREG werden am Kollektor Q209 (FCI) zusammengeführt und wirken auf die FrequenzStellung als ODER- Schaltung. Somit kann beispielsweise OPTO eine Kontrollfunk¬ tion der Sekundärseite des Wandlers über einen Optokoppler vornehmen und IREG eine Kontrolle des MaximalStromes des pri- märseitigen Leistungstransistors ermöglichen.

Eine Pulsweitenmodulation erfolgt bei der in Fig. 6, 7, 8, 9 dargestellten Schaltungsanordnung wie nachfolgend erläutert: Über den PWMS Q28, Q29 wird der am Anschluß CPG angeordnete Kondensator gesteuert. Bei gleicher Größe der Kondensatoren CVCO und CPG wird, falls keine Einstellung an den Anschlüssen OPTO und IREG erfolgt durch die Einstellung der Stromquelle Q206, Q15/Q16, Q30, Q75 gegenüber den Stromquellen Q200, Q3/Q4, sich der Kondensator am Anschluß VCO geringfügig (ohne Korrektur von Q17, Q18, Q19) schneller entladen und die untere Schwelle, die mit VG vorgegeben ist, erreichen.

Dadurch wird über Q35, Q38 ... Q43, Q44 am ECL-Flip-Flop Q43, Q45 ein Set ausgeführt. Über die Level-shift-Anordnung Q45 ... Q50 gelangt das differenzielle Signal an Q84, Q98 und führt hier über Q98 ein Set im ECL-Flip-Flop Q87, Q88 aus. Durch die Schaltungsausgestaltung der Ansteuerschaltung des ECL-Flip-Flop/PWM (PWM) wird eine stromsparende Triggerung mit einem geringen Komponentenaufwand und geringen Laufzeiten

erreicht. Nur positive Flanken an den Emittern von Q50, Q48 sind in der Lage ein Set oder Reset auszuüben. Ein Set erfolgt mit Q98, der den Set-Strom aus C2 entnimmt. Ein Reset erfolgt mit Q85, der den Reset-Strom aus Cl entnimmt. Die Zeitkonstanten Cl, C2, R (10K Ohm), sind so bemessen, daß bezüglich der höchsten VCO-Frequenz VCOfmax ein Set oder Reset sicher in der halben Periodendauer abgeklungen ist.

Über die Level-Shift-Anordnung Q89 ... Q94 wird nach erfolg- te Set der Schalter Q28, Q29 im PWMS umgeschaltet. Der Kon¬ densator C2 am Anschluß CPG lädt sich über Q206 auf. Der Strom im Kollektor Q206 ist wiederum so eingestellt, daß die Aufladung früher als am Kondensator C2 am Anschluß CVCO abge¬ schlossen ist. Erreicht das Potential am Kondensator C2 die Spannungspegel VF, verharrt er an diesem Spannungspegel, Fig. 7 und Fig. 8, wegen der Differenzstufe Q17/Q18, Q19, dem Gleichgewicht der Ströme Q206/Kollektor Q19/Kollektor/Basis und der Ausführung von Q19 als Diode. Die unsymmetrische Aus¬ bildung der Differenzstufe Q17 ... Q19 mit der Fläche 2 :1 ergibt eine gewünschte Korrektur des Spannungspegels um +18 mV auf den sich der Kondensator C2 gegenüber VF auflädt, weil bei Entladung nicht sofort der volle Strom im Kollektor von Q15, Q16 von Q17, Q18 übernommen wird (siehe Fig. 6) .

Ausgehend von diesen Voreinstellungen erfolgt die Stellung der Pulsbreite durch RUe am Anschluß PG. Über den Kollektor Q79 wird zunächst ein Strom I vom Stromspiegel Q32, Q31 nach GND abgeleitet. RUe ist so bemessen, daß bei der unteren Ein¬ gangsspannung Ue ein Stromgleichgewicht zwischen dem Entlade- ström von Kollektor Q79 und dem Strom in RUe vorhanden ist. Vergrößert sich die Spannung an RUe so wird der Stromspiegel Q32, Q31 aktiv und trägt in der Entladephase des Kondensators CPG zu dessen schnelleren Entladung bei. Über die Differenz¬ stufe Q20 ... Q27, die durch die Basis von Q25 und dem Buffer Q125, Q81 mit der unteren Referenzspannung VG verbunden ist, wird bei Entladung des Kondensators CPG auf VG über den Kol¬ lektor von Q24 am Flip-Flop Q87, Q88 ein Set ausgeführt,

wodurch über den Level-shift Q89 ... Q84 die Differenzstufe Q28, Q29 umgeschaltet wird und der Aufladevorgang am Konden¬ sator C2 beginnt.

Betrachtet man diesen Vorgang unter der Annahme, daß die Ent¬ ladung des Kondensators C2 schneller stattgefunden hat als die Entladung des Kondensators CVCO, so ist festzustellen, daß am ECL-Flip-Flop/PWM ein Set ausgeübt wurde, ohne daß eine Beeinflußung vom Komparator, ECL-Flip-Flop/Frequenz VCO vorhanden war.

Ein Set, durch das Flip-Flop Q43, Q44 bleibt wirkungslos, weil Q87, Q88 bereits gesetzt ist. Da jedoch der Kondensator C2 bei Erreichen der Spannung VF verharrt und nur ein Reset an Q87, Q88 durch Q43, Q44 ausgeführt werden kann, ist nun folgender Zusammenhang für die ECL-Signale an MOSL/MOSH her¬ gestellt: Die Frequenz ist durch die Zeitvariable Tl, Rj/p und den Hub VF-VG festgelegt. Die Pulsbreite kann über die Spannung Ue kontinuierlich verringert werden. Die Pulsbreite verhält sich durch die Ausführung der Schaltung umgekehrt proportional zur EingangsSpannung Ue; eine Verdopplung der Eingangsspannung führt zur Halbierung der Pulsbreite.

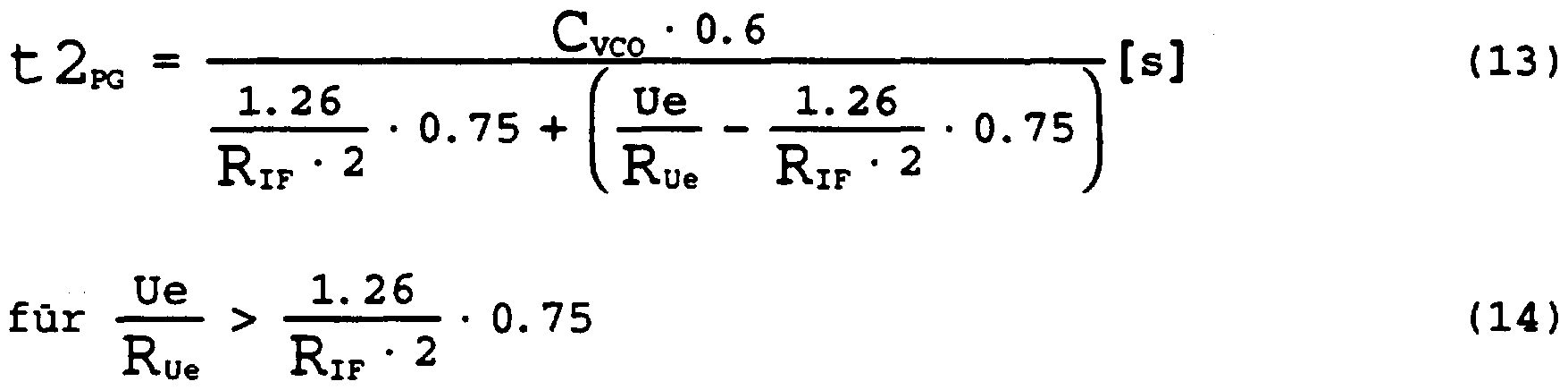

Folgender Zusammenhang ist mit den vorhandenen Spiegelver- hältnissen der Transistoren des Ausführungsbeispiels gegeben:

Einsatzschwelle für On-Zeit-Verkürzung

Ue 1.26

0.75 (15)

Rue RlF ' ^

t2pg: ON-Zeit bei Pulsweitenstellung Ue/Rτje:Strom für On-Zei -Verkürzung

Die Diodenflußspannung Q23 ist hier nicht berücksichtigt, kann aber für genauere Betrachtungen von Ue subtrahiert wer¬ den.

Die Figuren 10, 11 und 12 zeigen Spannungsverläufe am Anschluß MOSH in Abhängigkeit von Ue. Da die EingangsSpannung Ue über den Strom in Rue direkt auf den Kondensator CPG wirkt, kann die Pulsbreite ohne Verzöge¬ rung variiert werden. Durch den Anschluß von RUe an die Ein¬ gangsspannung und Wirkung auf die Pulsbreite bei Überschrei¬ tung der Schwellenspannung Ue ist eine weitere Bedingungen abgesichert, die darin besteht, daß falls über IREG oder OPTO die Frequenz am CSVCO verringert wird, sich die Periodendauer erhöht, die Pulsdauer sich aber nicht verändern kann, da durch die Voreinstellung der Spannungsverläufe an VCO und CPG in der Art, daß der Spannungsverlauf für die Maximalfrequenz bei Entladung an CPG um weniger als 1% langsamer verläuft als an CVCO, der. Set Impuls für das Flip-Flop Q87, Q88 bei Fre¬ quenzverringerung sofort durch Q24 erfolgt. Die Schaltung ermöglicht somit eine unabhängige Stellung von Pulsbreite und Frequenz. Nur bei der eingestellten Maximalfrequenz und mini¬ maler Eingangsspannung Ue wird das größte Puls-Pause erreicht.

Fig. 10 zeigt den Spannungsverlauf am Anschluß MOSH ohne PulsVerkürzung über den Anschluß PG.

Fig. 11 zeigt den Spannungsverlauf am Anschluß MOSH mit Puls¬ verkürzung von 0.4 Tma MOSH über den Anschluß PG:

Fig. 12 zeigt den Spannungsverlauf an MOSH mit PulsVerkürzung von O.OδTmax Mostjüber n Anschluß PG.

Fig. 13 zeigt einen Spannungsverlauf an MOSH durch Frequenz¬ stellung mit Stromeinprägung an den Anschlüssen OPTO oder IREG. PG ist nicht aktiv.