# PLL1700

# **MULTI-CLOCK GENERATOR**

### **FEATURES**

- 27MHZ MASTER CLOCK INPUT

- GENERATED AUDIO SYSTEM CLOCK: SCKO1: 33.8688MHz (Fixed) SCKO2: 256f<sub>S</sub> SCKO3: 384f<sub>S</sub> SCKO4: 768f<sub>S</sub>

- ZERO PPM ERROR OUTPUT CLOCKS

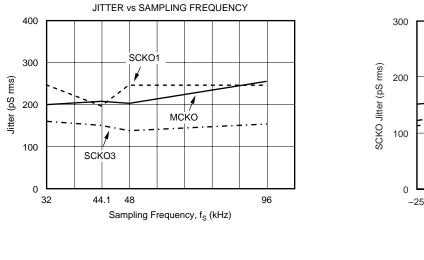

- LOW CLOCK JITTER: 150ps at SCKO3

- MULTIPLE SAMPLING FREQUENCIES: f<sub>S</sub> = 32kHz, 44.1kHz, 48kHz, 64kHz, 88.2kHz, 96kHz

- +3.3V CMOS LOGIC INTERFACE

- DUAL POWER SUPPLIES: +5V and +3.3V

- SMALL PACKAGE: 20-Lead SSOP

# DESCRIPTION

The PLL1700 is a low cost, multi-clock generator Phase Lock Loop (PLL).

The PLL1700 can generate four systems clocks from a 27MHz reference input frequency.

The device gives customers both cost and space savings by eliminating external components and enables customers to achive the very low jitter performance needed for high performance audio digital-to-analog converters (DAC) and/or analog-to-digital converters (ADC).

The PLL1700 is ideal for MPEG-2 applications which use a 27MHz master clock such as DVD players, DVD add-on cards for multimedia PCs, digital HDTV systems, and set-top boxes.

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 • Twx: 910-952-1111 Internet: http://www.burr-brown.com/ • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

# **SPECIFICATIONS**

All specifications at  $T_A = +25^{\circ}C$ ,  $V_{DD} = V_{DDP} = +5V$ ,  $V_{DDB} = +3.3V$ ,  $f_M = 27MHz$  crystal oscillation and  $f_S = 48kHz$ , unless otherwise noted.

|                                                       |                                      |                  | PLL1700E       |          |         |  |  |

|-------------------------------------------------------|--------------------------------------|------------------|----------------|----------|---------|--|--|

| PARAMETER                                             | CONDITIONS                           | MIN              | TYP            | MAX      | UNITS   |  |  |

| DIGITAL INPUT/OUTPUT                                  |                                      |                  |                |          |         |  |  |

| Input Logic Level:                                    |                                      |                  | TTL-Compatible | 9        |         |  |  |

| V <sub>IH</sub>                                       |                                      | 2.0              |                |          | VDC     |  |  |

| V <sub>IL</sub>                                       |                                      |                  |                | 0.8      | VDC     |  |  |

| Input Logic Current:                                  |                                      |                  |                |          |         |  |  |

| I <sub>IH</sub> (1)                                   | $V_{IN} = V_{DD}$                    |                  |                | 200      | μA      |  |  |

| I <sub>II</sub> <sup>(1)</sup>                        | $V_{IN} = 0V$                        |                  |                | -1       | μA      |  |  |

| I <sub>IH</sub> <sup>(2)</sup>                        | $V_{IN} = V_{DD}$                    |                  |                | 4        | mA      |  |  |

| I <sub>IL</sub> <sup>(2)</sup>                        | $V_{IN} = 0V$                        |                  |                | -800     | μA      |  |  |

| Output Logic Level:                                   |                                      |                  | CMOS           |          |         |  |  |

| V <sub>OH</sub> <sup>(3)</sup>                        | $I_{OH} = 4mA$                       | $V_{DDB} - 0.4V$ |                |          | VDC     |  |  |

| V <sub>OL</sub> <sup>(3)</sup>                        | $I_{OL} = 4mA$                       | 000              |                | 0.4      | VDC     |  |  |

| Sampling Frequency (f <sub>S</sub> )                  | Standard f <sub>S</sub>              | 32               | 44.1           | 48       | kHz     |  |  |

|                                                       | Double f <sub>S</sub>                | 64               | 88.2           | 96       | kHz     |  |  |

| MASTER CLOCK (MCKO, MCKO)                             |                                      |                  |                |          |         |  |  |

|                                                       | $f_{M} = 27MHz, C_{L} = 20pF$        | 26.72            | 27             | 27.27    | MHz     |  |  |

| Master Clock Frequency<br>Clock Jitter <sup>(4)</sup> |                                      | 26.73            | 300            | 21.21    |         |  |  |

|                                                       |                                      | 40               | 50             | 60       | ps<br>% |  |  |

|                                                       |                                      | 40               | 50             | 60<br>60 | %       |  |  |

|                                                       |                                      | 40               | 50<br>40       | 60       | %       |  |  |

|                                                       |                                      |                  | 40<br>60       |          | %       |  |  |

|                                                       |                                      | _                | 60             |          | %       |  |  |

| PHASE LOCK LOOP (PLL)                                 | $f_M = 27MHz, C_L = 20pF$            |                  |                |          |         |  |  |

| Generated System Clock Frequency                      |                                      |                  |                |          |         |  |  |

| SCKO1                                                 | Fixed                                |                  | 33.8688        |          | MHz     |  |  |

| SCKO2                                                 | 256f <sub>S</sub>                    | 8.192            |                | 24.576   | MHz     |  |  |

| SCKO3                                                 | 384f <sub>S</sub>                    | 12.288           |                | 36.864   | MHz     |  |  |

| SCKO4                                                 | 768f <sub>S</sub>                    | 24.576           |                | 36.864   | MHz     |  |  |

| Generated Clock Rise Time <sup>(3)</sup>              | 20% to 80% V <sub>DDB</sub>          |                  | 5              |          | ns      |  |  |

| Generated Clock Fall Time <sup>(3)</sup>              | 80% to 20% V <sub>DDB</sub>          |                  | 5              |          | ns      |  |  |

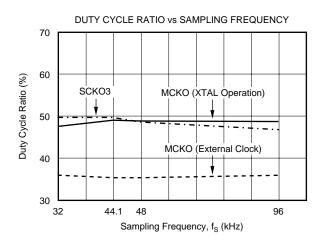

| Generated Clock Duty Cycle                            | SCKO1, SCKO3, SCKO4                  | 40               | 50             | 60       | %       |  |  |

|                                                       | SCKO2 (standard)                     | 40               | 50             | 60       | %       |  |  |

|                                                       | SCKO2 (double) <sup>(5)</sup>        | 25               | 33             | 40       | %       |  |  |

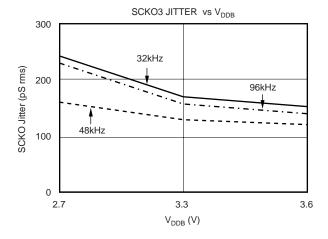

| Generated Clock Jitter <sup>(4)</sup>                 | SCKO1, SCKO2 (standard), SCKO4       |                  | 300            |          | ps      |  |  |

|                                                       | SCKO3                                |                  | 150            |          | ps      |  |  |

|                                                       | SCKO2 (double)                       |                  | 450            |          | ps      |  |  |

| Settling Time                                         | To Programmed Frequency              |                  |                | 20       | ms      |  |  |

| Power-Up Time                                         | To Programmed Frequency              |                  | 15             | 30       | ms      |  |  |

| POWER SUPPLY REQUIREMENTS                             |                                      |                  |                |          |         |  |  |

| Voltage Range                                         | V <sub>DD</sub> , V <sub>DDP</sub>   | +4.5             | +5             | +5.5     | VDC     |  |  |

|                                                       | V <sub>DDB</sub>                     | +2.7             | +3.3           | +3.6     | VDC     |  |  |

| Supply Current <sup>(6)</sup> :                       |                                      |                  |                |          |         |  |  |

| I <sub>DD</sub> + I <sub>DDP</sub>                    | $V_{DD} = V_{DDP} = 5V, f_S = 48kHz$ |                  | 11             | 16       | mA      |  |  |

| I <sub>DDB</sub>                                      | $V_{DDB} = +3.3V, f_{S} = 48kHz$     |                  | 6              | 9        | mA      |  |  |

| Power Dissipation                                     | $f_{S} = 48 \text{kHz}$              |                  | 75             | 110      | mW      |  |  |

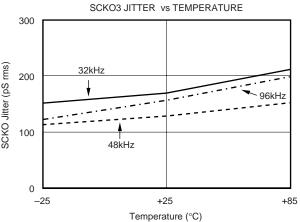

| TEMPERATURE RANGE                                     | -                                    |                  |                |          |         |  |  |

| Operation                                             |                                      | -25              |                | +85      | °C      |  |  |

| Storage                                               |                                      | -55              |                | +125     | °Č      |  |  |

NOTES: (1) ML, MC, MD, MODE,  $\overrightarrow{RST}$  (Schmitt-trigger input with internal pull-down resistor). (2) XT1, when an external 27MHz clock is used, the buffer ICs, such as 74HC04, are recommended to interface to XT1. (3) MCKO,  $\overrightarrow{MCKO}$ , SCKO4, SCKO3, SCKO2, and SCKO1. (4) Jitter performance is specified as standard deviation of jitter under 27MHz crystal oscillation. (5) When SCKO2 is set to double rate clock output, its duty cycle is 33%. (6)  $f_M$  = 27MHz crystal oscillation, no load on MCKO,  $\overrightarrow{MCKO}$ , SCKO4, SCKO1.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

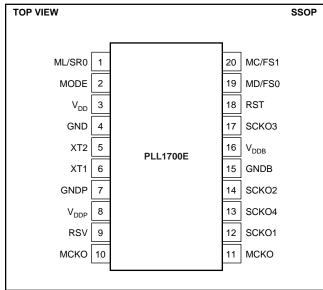

### **PIN CONFIGURATION**

### **PACKAGE INFORMATION**

| PRODUCT  | PACKAGE      | TEMPERATURE<br>RANGE | PACKAGE<br>DRAWING<br>NUMBER <sup>(1)</sup> |  |  |

|----------|--------------|----------------------|---------------------------------------------|--|--|

| PLL1700E | 20-Lead SSOP | –25°C to +85°C       | 334-1                                       |  |  |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book.

### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage (+V <sub>DD</sub> , +V <sub>DDP</sub> , +V <sub>DDB</sub> ) |                                    |

|----------------------------------------------------------------------------|------------------------------------|

| Supply Voltage Differences (+V <sub>DD</sub> , +V <sub>DDP</sub> )         | ±0.1V                              |

| GND Voltage Differences: GND, GNDP, GNDB                                   | ±0.1V                              |

| Digital Input Voltage                                                      | –0.3V to (V <sub>DD</sub> + 0.3V)  |

| Digital Output Voltage                                                     | –0.3V to (V <sub>DDB</sub> + 0.3V) |

| Input Current (any pins except supply pins)                                | ±10mA                              |

| Power Dissipation                                                          | 300mW                              |

| Operating Temperature Range                                                | –25°C to +85°C                     |

| Storage Temperature                                                        | –55°C to +125°C                    |

| Lead Temperature (soldering, 5s)                                           | +260°C                             |

| Package Temperature (IR reflow, 10s)                                       | +235°C                             |

|                                                                            |                                    |

### **PIN ASSIGNMENTS**

| PIN | NAME             | I/O | FUNCTION                                                                                                                                                                                                                                                                                          |

|-----|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | ML/SR0           | IN  | Latch Enable for Software Mode/Sampling Rate Selection for Hardware Mode. When MODE pin is LOW, ML is selected. <sup>(1)</sup>                                                                                                                                                                    |

| 2   | MODE             | IN  | Mode Control Select. When this pin is HIGH,<br>device is operated in hardware mode using SR0<br>(pin 1), FS0 (pin 19), and FS1 (pin 20). When<br>this pin is LOW, device is operated in software<br>mode by three-wire interface using ML (pin 1),<br>MD (pin 19) and MC (pin 20). <sup>(1)</sup> |

| 3   | V <sub>DD</sub>  | —   | Digital Power Supply, +5V.                                                                                                                                                                                                                                                                        |

| 4   | GND              | —   | Digital Ground.                                                                                                                                                                                                                                                                                   |

| 5   | XT2              | _   | 27MHz Crystal. When an external 27MHz clock<br>is applied to XT1 (pin 6), this pin must be<br>connected to GND.                                                                                                                                                                                   |

| 6   | XT1              | IN  | 27MHz Oscillator Input/External 27MHz Input.                                                                                                                                                                                                                                                      |

| 7   | GNDP             | —   | Ground for PLL.                                                                                                                                                                                                                                                                                   |

| 8   | V <sub>DDP</sub> | —   | Power Supply for PLL, +5V.                                                                                                                                                                                                                                                                        |

| 9   | RSV              | —   | Reserved. Must be left open.                                                                                                                                                                                                                                                                      |

| 10  | мско             | OUT | 27MHz Output.                                                                                                                                                                                                                                                                                     |

| 11  | мско             | OUT | Inverted 27MHz Output.                                                                                                                                                                                                                                                                            |

| 12  | SCKO1            | OUT | Fixed 33.8688MHz Clock Output.                                                                                                                                                                                                                                                                    |

| 13  | SCKO4            | OUT | 768f <sub>S</sub> Clock Output.                                                                                                                                                                                                                                                                   |

| 14  | SCKO2            | OUT | 256f <sub>S</sub> Clock Output.                                                                                                                                                                                                                                                                   |

| 15  | GNDB             | —   | Digital Ground for V <sub>DDB</sub> .                                                                                                                                                                                                                                                             |

| 16  | V <sub>DDB</sub> | —   | Digital Power Supply for Clock Output Buffers, +3.3V.                                                                                                                                                                                                                                             |

| 17  | SCKO3            | OUT | $384f_{\rm S}$ Output. This output has been optimized for the lowest jitter and should be connected to the audio DAC(s).                                                                                                                                                                          |

| 18  | RST              | IN  | Reset. When this pin is LOW, device is held in $\ensuremath{reset}.^{(1)}$                                                                                                                                                                                                                        |

| 19  | MD/FS0           | IN  | Serial Data Input for Software Mode/Sampling<br>Frequency Selection for Hardware Mode. When<br>MODE pin is LOW, MD is selected. <sup>(1)</sup>                                                                                                                                                    |

| 20  | MC/FS1           | IN  | Shift Clock Input for Software Mode/Sampling<br>Frequency Selection for Hardware Mode. When<br>MODE pin is LOW, MC is selected. <sup>(1)</sup>                                                                                                                                                    |

NOTE: (1) Schmitt-trigger input with internal pull-down resistors.

## ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

**PLL1700**

3

# **TYPICAL PERFORMANCE CURVES**

At T<sub>A</sub> = +25°C, V<sub>DD</sub> = V<sub>DDP</sub> = +5V, V<sub>DDB</sub> = +3.3V, C<sub>L</sub> = 20pF, unless otherwise noted.

# THEORY OF OPERATION

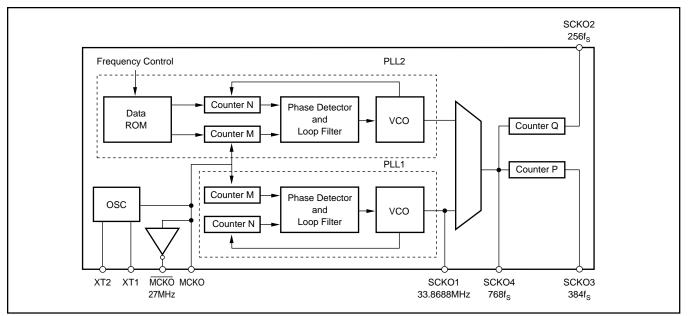

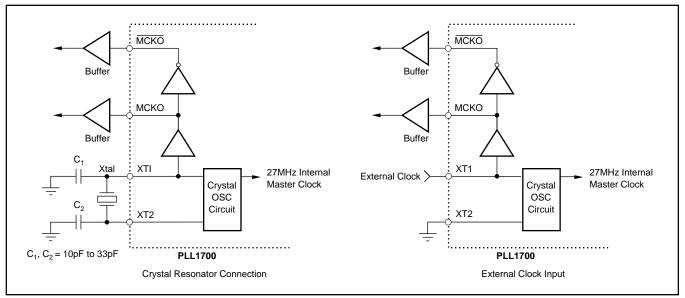

### MASTER CLOCK AND SYSTEM CLOCK OUTPUT

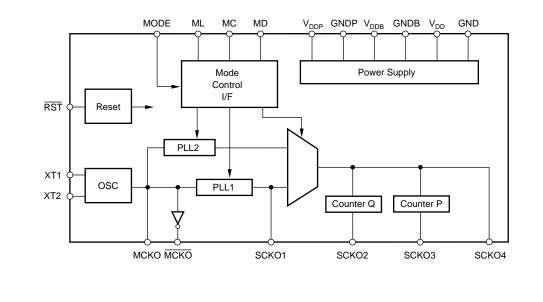

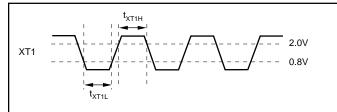

The PLL1700 consists of a dual PLL clock and master clock generator which generates four system clocks and two buffered 27MHz clocks from a 27MHz master clock. Figure 1 shows the block diagram of the PLL1700. The PLL is designed to accept a 27MHz master clock or crystal oscillator. The master clock can be either a crystal oscillator placed between XT1 (pin 6) and XT2 (pin 5), or an external input to XT1. If an external master clock is used, XT2 should be connected to ground. Figure 2 illustrates possible system clock connection options, and Figure 3 illustrates the 27MHz master clock timing requirements.

FIGURE 1. Block Diagram of PLL1700.

FIGURE 2. Master Clock Generator Connection Diagram.

| DESCRIPTION                                                   | SYMBOL                                 | MIN      | ТҮР | MAX | UNITS    |

|---------------------------------------------------------------|----------------------------------------|----------|-----|-----|----------|

| System Clock Pulse Width HIGH<br>System Clock Pulse Width LOW | t <sub>XT1H</sub><br>t <sub>XT1L</sub> | 15<br>15 |     |     | ns<br>ns |

FIGURE 3. External Master Clock Timing Requirement.

The PLL1700 provides a very low jitter, high accuracy clock. SCKO1 is a fixed frequency clock which is 33.8688MHz (768 x 44.1kHz) for a CD-DA DSP. The output frequency of the remaining clocks is determined by the sampling frequency ( $f_S$ ) by software or hardware control. SCKO2 and SCKO3 output 256 $f_S$  and 384 $f_S$  systems clocks, respectively. SCKO4 output is 768 $f_S$  if the sampling frequency is 32kHz, 44.1kHz, 48kHz, or the output is 384 $f_S$  if the sampling frequency is 64kHz, 88.2kHz, or 96kHz. Table I shows each sampling frequency. The system clock output frequencies are generated by a 27MHz master clock and programmed sampling frequencies are shown in Table II.

| SAMPLING RATE                           | SAMPLING<br>FREQUENCY (kHz) |      |    |  |  |

|-----------------------------------------|-----------------------------|------|----|--|--|

| Standard Sampling Frequencies           | 32                          | 44.1 | 48 |  |  |

| Double of Standard Sampling Frequencies | 64                          | 88.2 | 96 |  |  |

TABLE I. Sampling Frequencies.

| SAMPLING<br>FREQUENCY<br>(kHz) | SAMPLING<br>RATE | SKCO2<br>(MHz) | SCKO3<br>(MHz) | SCKO4<br>(MHz) |

|--------------------------------|------------------|----------------|----------------|----------------|

| 32                             | Standard         | 8.192          | 12.288         | 24.576         |

| 44.1                           | Standard         | 11.2896        | 16.9344        | 33.8688        |

| 48                             | Standard         | 12.288         | 18.4320        | 36.8640        |

| 64                             | Double           | 16.384         | 24.576         | 24.576         |

| 88.2                           | Double           | 22.5792        | 33.8688        | 33.8688        |

| 96                             | Double           | 24.576         | 36.8640        | 36.8640        |

TABLE II. Sampling Frequencies and Master Clock Output Frequencies.

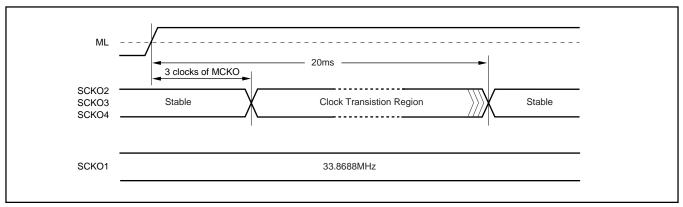

Response time from power-on (or applying the clock to XT1) to SCKO settling time is typically 15ms. Delay time from sampling frequency change to SCKO settling time is 20ms maximum. Figure 4 illustrates SCKO transient timing. External buffers are recommended on all output clocks in order to avoid degrading the jitter performance of the PLL1700.

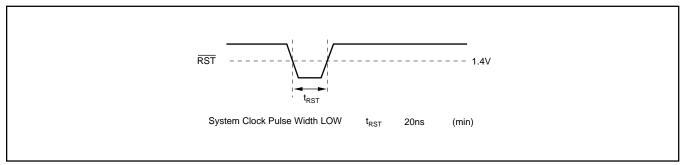

### RESET

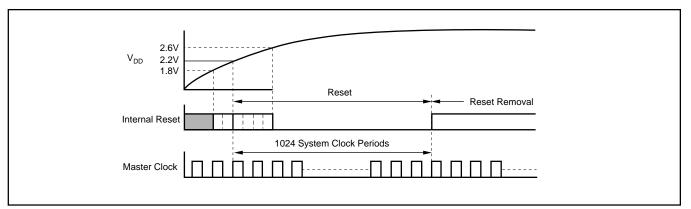

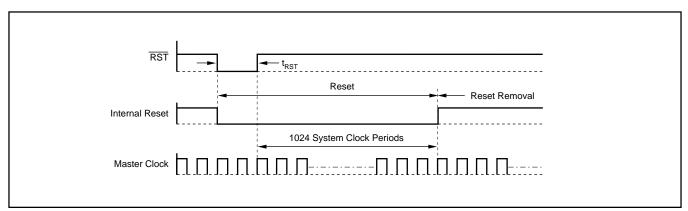

The PLL1700 has an internal power-on reset circuit, as well as an external forced reset (RST, pin 18). Both resets have the same effect on the PLL1700's functions. The mode register's default settings for software mode are initialized by reset. Throughout the reset period, all clock outputs are enabled with the default settings. Initialization for the internal power-on reset is done automatically during 1024 master clocks at  $V_{DD} \ge 2.2V$  (1.8V to 2.6V). When using the internal power-on reset, RST should be HIGH. Power-on reset timing is shown in Figure 5. RST (pin 18) accepts an external forced reset by RST = L. Initialization (reset) is done when RST = L and 1024 master clocks after RST = H. External reset timing is shown in Figures 6 and 7.

### **FUNCTION CONTROL**

The built-in function of the PLL1700 can be controlled in the software mode (serial mode), which uses a three-wire interface by ML (pin 1), MC (pin 20), and MD (pin 19), when MODE (pin 2) = L. They can also be controlled in the hardware mode (parallel mode) which uses SR0 (pin 1), FS1 (pin 20) and FS0 (pin 19), when MODE (pin 2) = H. The selectable functions are shown in Table III.

| FUNCTION                                             | HARDWARE<br>MODE<br>(MODE = H) | SOFTWARE<br>MODE<br>(MODE = L) |

|------------------------------------------------------|--------------------------------|--------------------------------|

| Sampling Frequency Select<br>(32kHz, 44.1kHz, 48kHz) | Yes                            | Yes                            |

| Sampling Rate Select (Standard/Double)               | Yes                            | Yes                            |

| Each Clock Output Enable/Disable                     | No                             | Yes                            |

TABLE III. Selectable Functions.

### HARDWARE MODE (MODE = H)

In the hardware mode, the following functions can be selected:

### Sampling Group Select

The sampling frequency group can be selected by FS1 (pin 20) and FS0 (pin 19).

| FS1 (Pin 20) | FS0 (Pin 19) | SAMPLING GROUP |

|--------------|--------------|----------------|

| L            | L            | 48kHz          |

| L            | н            | 44.1kHz        |

| н            | L            | 32kHz          |

| Н            | Н            | Reserved       |

### Sampling Rate Select

The sampling rate can be selected by SR0 (pin 1)

| SR0 (Pin 1) | SAMPLING RATE SELECT |

|-------------|----------------------|

| L           | Standard             |

| н           | Double               |

### SOFTWARE MODE (MODE = L)

The PLL1700's special function in software mode is shown in Table IV. These functions are controlled using ML, MC, and MD serial control signal.

| FUNCTION                                          | DEFAULT     |

|---------------------------------------------------|-------------|

| Sampling Frequency Select (32kHz, 44.1kHz, 48kHz) | 48kHz Group |

| Sampling Rate Select (Standard/Double)            | Standard    |

| Each Clock Output Enable/Disable                  | Enable      |

TABLE IV. Selectable Functions.

FIGURE 4. System Clock Transient Timing Chart.

FIGURE 5. Power-On Reset Timing.

FIGURE 6. External Reset Timing.

FIGURE 7. Reset Pulse Timing Requirement.

### **PROGRAM REGISTER BIT-MAPPING**

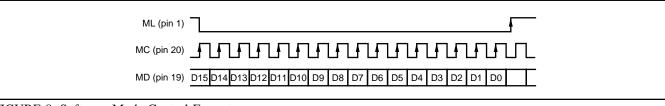

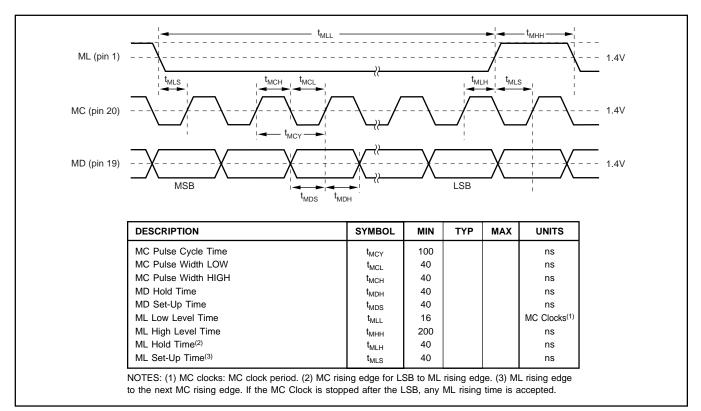

The built-in functions of the PLL1700 are controlled through a 16-bit program register. This register is loaded using MD. After the 16 data bits are clocked in using the rising edge of MC, ML is used to latch the data into the register. Table V shows the bit-mapping of the registers. The software mode control format and control data input timing is shown in Figures 8 and 9, respectively.

#### Mode Register

|   | - · · |   |   | - · · |   |     |     |     |     |     |     |     |     |     | D0  |

|---|-------|---|---|-------|---|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0 | 1     | 1 | 1 | 0     | 0 | CE6 | CE5 | CE4 | CE3 | CE2 | CE1 | SR1 | SR0 | FS1 | FS0 |

| REGISTER | BIT NAME | DESCRIPTION                 |

|----------|----------|-----------------------------|

| MODE     | CE6      | MCKO Output Enable/Disable  |

|          | CE5      | MCKO Output Enable/Disable  |

|          | CE4      | SCKO4 Output Enable/Disable |

|          | CE3      | SCKO3 OUtput Enable/Disable |

|          | CE2      | SCKO2 Output Enable/Disable |

|          | CE1      | SCKO1 Output Enable/Disable |

|          | SR [1:0] | Sampling Rate Select        |

|          | FS [1:0] | Sampling Frequency Select   |

TABLE V. Register Mapping.

### Mode Register

FS [1:0]: Sampling Frequency Group Select

| FS1 | FS0 | SAMPLING FREQUENCY | DEFAULT |

|-----|-----|--------------------|---------|

| 0   | 0   | 48kHz              | 0       |

| 0   | 1   | 44.1kHz            |         |

| 1   | 0   | 32kHz              |         |

| 1   | 1   | Reserved           |         |

SR [1:0]: Sample Rate Select

| SR1 | SR0 | SAMPLING RATE | DEFAULT |

|-----|-----|---------------|---------|

| 0   | 0   | Standard      | 0       |

| 0   | 1   | Double        |         |

| 1   | 0   | Reserved      |         |

| 1   | 1   | Reserved      |         |

CE [1:6]: Clock Output Control

| CE1 - CE6 | CLOCK OUTPUT CONTROL | DEFAULT |

|-----------|----------------------|---------|

| 0         | Clock Output Disable |         |

| 1         | Clock Output Enable  | 0       |

FIGURE 8. Software Mode Control Format.

FIGURE 9. Control Data Input Timing.

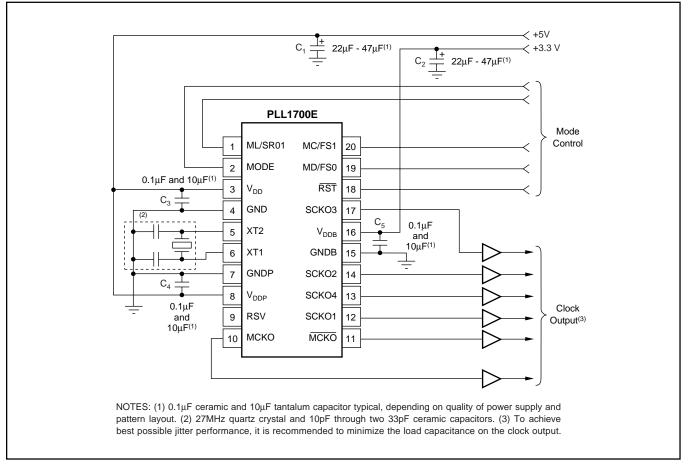

### **CONNECTION DIAGRAM**

Figure 10 shows the typical connection circuit for the PLL1700. There are three grounds for digital, analog and PLL power supply. However, the use of one common ground connection is recommended to avoid latch-up problems. Power supplies should be bypassed as close as possible to the device.

### **MPEG-2 APPLICATIONS**

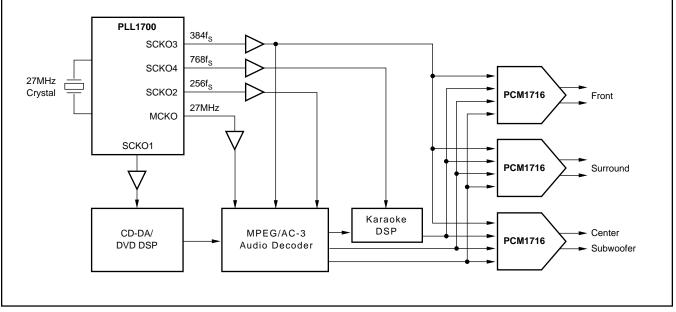

Typical applications for the PLL1700 are MPEG-2 based systems such as DVD players, DVD add-on cards for multimedia PCs, digital HDTV systems, and step-top boxes. The PLL1700 provides audio system clocks for a CD-DA DSP, DVD DSP, Karaoke DSP, and DAC(s) from a 27MHz video clock.

FIGURE 10. Typical Connection Diagram.

FIGURE 11. PLL1700 System Application Block Diagram.

### PACKAGING INFORMATION

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| PLL1700E         | ACTIVE                | SSOP            | DB                 | 20   | 65             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| PLL1700E/2K      | ACTIVE                | SSOP            | DB                 | 20   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| PLL1700E/2KG4    | ACTIVE                | SSOP            | DB                 | 20   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| PLL1700EG        | ACTIVE                | SSOP            | DB                 | 20   | 65             | Pb-Free<br>(RoHS)         | CU SNBI          | Level-1-260C-UNLIM           |

| PLL1700EG/2K     | ACTIVE                | SSOP            | DB                 | 20   | 2000           | Pb-Free<br>(RoHS)         | CU SNBI          | Level-1-260C-UNLIM           |

| PLL1700EG/2KE6   | ACTIVE                | SSOP            | DB                 | 20   | 2000           | Pb-Free<br>(RoHS)         | CU SNBI          | Level-1-260C-UNLIM           |

| PLL1700EG4       | ACTIVE                | SSOP            | DB                 | 20   | 65             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| PLL1700EGE6      | ACTIVE                | SSOP            | DB                 | 20   | 65             | Pb-Free<br>(RoHS)         | CU SNBI          | Level-1-260C-UNLIM           |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details. TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products           |                        | Applications       |                           |

|--------------------|------------------------|--------------------|---------------------------|

| Amplifiers         | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters    | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP                | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface          | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic              | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt         | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers   | microcontroller.ti.com | Security           | www.ti.com/security       |

| Low Power Wireless | www.ti.com/lpw         | Telephony          | www.ti.com/telephony      |

|                    |                        | Video & Imaging    | www.ti.com/video          |

|                    |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2007, Texas Instruments Incorporated