Distributed by:

JAMECO

ELECTRONICS

## www.Jameco.com + 1-800-831-4242

The content and copyrights of the attached material are the property of its owner.

Jameco Part Number 764545

SLUS329E - JUNE 1998 - REVISED AUGUST 2006

# ADVANCED HIGH-POWER FACTOR PREREGULATOR

## **FEATURES**

- Controls Boost PWM to Near-Unity Power Factor

- Limits Line Current Distortion To < 3%</li>

- World-Wide Operation Without Switches

- Accurate Power Limiting

- Fixed-Frequency Average Current-Mode Control

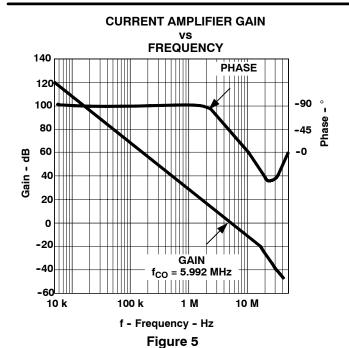

- High Bandwidth (5 MHz), Low-Offset Current Amplifier

- Integrated Current- and Voltage Amplifier Output Clamps

- Multiplier Improvements: Linearity, 500 mV

V<sub>AC</sub> Offset (Eliminates External Resistor), 0 V

to 5 V Multout Common-Mode Range

- V<sub>RFF</sub> GOOD Comparator

- Faster and Improved Accuracy ENABLE Comparator

- UVLO Options (16 V/10 V or 10.5 V/10 V)

- 300-μA Start-Up Supply Current

## DESCRIPTION

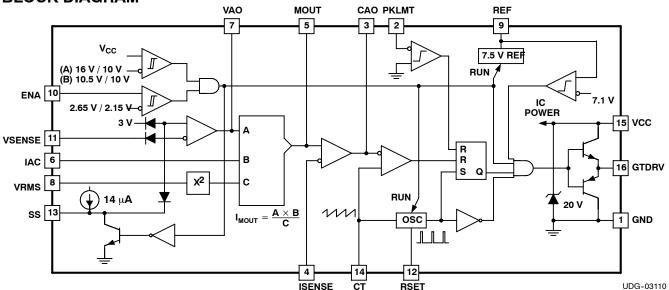

The UC3854A/B products are pin compatible enhanced versions of the UC3854. Like the UC3854, these products provide all of the functions necessary for active power factor corrected preregulators. The controller achieves near unity power factor by shaping the AC input line current waveform to correspond to the AC input line voltage. To do this the UC3854A/B uses average current mode control. Average current mode control maintains stable, low distortion sinusoidal line current without the need for slope compensation, unlike peak current mode control.

A 1% 7.5 V reference, fixed frequency oscillator, PWM, voltage amplifier with soft-start, line voltage feedforward ( $V_{RMS}$  squarer), input supply voltage clamp, and over current comparator round out the list of features.

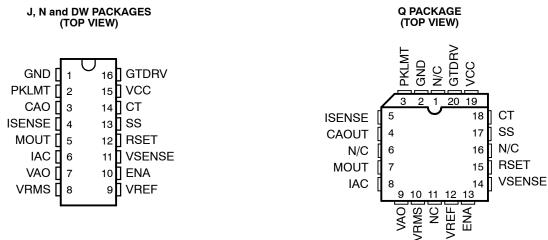

Available in the 16-pin N (PDIP), DW (SOIC-Wide), and J (CDIP) and 20-pin Q (PLCC) package. See ordering information on page 3 for availability by temperature range.

#### **BLOCK DIAGRAM**

SLUS329E - JUNE 1998 - REVISED AUGUST 2006

## **DESCRIPTION** (continued)

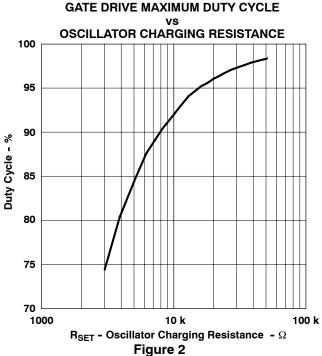

The UC3854A/B products improve upon the UC3854 by offering a wide bandwidth, low offset current amplifier, a faster responding and improved accuracy enable comparator, a VREF GOOD comparator, UVLO threshold options (16 V/10 V for offline, 10.5 V/10 V for startup from an auxiliary 12 V regulator), lower startup supply current, and an enhanced multiply/divide circuit. New features like the amplifier output clamps, improved amplifier current sinking capability, and low offset VAC pin reduce the external component count while improving performance. Improved common mode input range of the multiplier output/current amplifier input allow the designer greater flexibility in choosing a method for current sensing. Unlike its predecessor,  $R_{\rm SET}$  controls only oscillator charging current and has no effect on clamping the maximum multiplier output current. This current is now clamped to a maximum of  $2 \times I_{\rm AC}$  at all times which simplifies the design process and provides foldback power limiting during brownout and extreme low line conditions.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted(1)

|                                                     |                           | UCX854A, UCX854B | UNIT |

|-----------------------------------------------------|---------------------------|------------------|------|

| Supply voltage, V <sub>CC</sub>                     |                           | 22               | V    |

| GTDRV current, I <sub>GTDRV</sub>                   | Continuous                | 0.5              | Α    |

| GTDRV Current, I <sub>GTDRV</sub>                   | 50% duty cycle            | 1.5              | Α    |

| Land Allenda                                        | VSENSE, VRMS, ISENSE MOUT | 11               | V    |

| Input voltage                                       | PKLMT                     | 5                | V    |

| Input current                                       | RSET, IAC, PKLMT, ENA     | 10               | mA   |

| Power dissipation                                   |                           | 1                | W    |

| Junction temperature, T <sub>J</sub>                |                           | -55 to 150       |      |

| Storage temperature, T <sub>stg</sub>               | -65 to 150                | °C               |      |

| Lead temperature, T <sub>sol,</sub> 1,6 mm (1/16 in | 300                       |                  |      |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltages are with respect to GND. Currents are positive into and negative out of, the specified terminal. ENA input is internally clamped to approximately 10 V.

#### RECOMMENDED OPERATING CONDITIONS

|                                                |         | MIN | MAX | UNIT |

|------------------------------------------------|---------|-----|-----|------|

| Supply voltage, V <sub>CC</sub>                |         | 10  | 20  | V    |

|                                                | UC1854X | -55 | 125 |      |

| Operating junction temperature, T <sub>J</sub> | UC2854X | -40 | 85  | °C   |

|                                                | UC3854X | 0   | 70  |      |

## PACKAGE DESCRIPTION

N/C - No connection

## **ORDERING INFORMATION**

|                | UVLO           | UVLO            | PART NUMBERS   |                |                 |                |  |  |

|----------------|----------------|-----------------|----------------|----------------|-----------------|----------------|--|--|

| T <sub>A</sub> | TURN-ON<br>(V) | TURN-OFF<br>(V) | CDIP-16<br>(J) | PDIP-16<br>(N) | SOIC-16<br>(DW) | PLCC-20<br>(Q) |  |  |

|                | 16             | 10              | -              | -              | -               | -              |  |  |

| -55°C to 125°C | 10.5           | 10              | UC1854BJ       | -              | -               | -              |  |  |

| 1000 1 0500    | 16             | 10              | UC2854AJ       | UC2854AN       | UC2854ADW       | UC2854AQ       |  |  |

| -40°C to 85°C  | 10.5           | 10              | UC2854BJ       | UC2854BN       | UC2854BDW       | UC2854BQ       |  |  |

| 000 1- 7000    | 16             | 10              | -              | UC3854AN       | UC3854ADW       | -              |  |  |

| 0°C to 70°C    | 10.5           | 10              | -              | UC3854BN       | UC3854BDW       | -              |  |  |

<sup>(1)</sup> The DW and Q packages are available taped and reeled. Add TR suffix to device type (e.g. UC2854ADWTR) to order quantities of 2,000 devices per reel for the DW package and 1,000 devices per reel for the Q package.

## THERMAL RESISTANCE

|                        | PACKAGED DEVICES  |                |                       |                      |  |  |  |  |

|------------------------|-------------------|----------------|-----------------------|----------------------|--|--|--|--|

| RESISTANCES            | CDIP-16<br>(J)    | PDIP-16<br>(N) | SOP-16<br>(DW)        | PLCC-20<br>(Q)       |  |  |  |  |

| θ <sub>JC</sub> (°C/W) | 28 <sup>(2)</sup> | 45             | 27                    | 34                   |  |  |  |  |

| θ <sub>JA</sub> (°C/W) | 80-120            | 90(3)          | 50-130 <sup>(3)</sup> | 43-75 <sup>(3)</sup> |  |  |  |  |

$<sup>\</sup>theta_{JC}$  data values stated are derived from MIL-STD-1835B which states "the baseline values shown are worst case (mean +2s) for a 60  $\times$  60 mil microcircuit device silicon die and applicable for devices with die sizes up to 14,400 square mils. For device die sizes greater than 14,400 square mils use the following values, dual-in-line, 11°C/W; flat pack and pin grid array, 10°C/W.

<sup>(3)</sup> θ<sub>JA</sub> (junction-to-ambient) applies to devices mounted to five square inch FR4 PC board with one ounce copper where noted. When resitance range is given, lower values are for five square inch aluminum PC board. Test PWB is 0.062 inches thick and typically uses 0.635 mm trace widths for power packages and 1.3 mm trace widths for non-power packages with a 100 x 100 mil probe land are at the end of each trace.

## **ELECTRICAL CHARACTERISTICS**

$V_{CC} = 18 \text{ V}, R_T = 8.2 \text{ k}\Omega, C_T = 1.5 \text{ nF}, V_{PKLMT} = 1 \text{ V}, V_{VRMS} = 1.5 \text{ V}, I_{IAC} = 100 \text{ }\mu\text{A}, I_{ISENSE} = 0 \text{ V}, V_{CAO} = 3.5 \text{ V}, V_{VAO} = 5 \text{ V}, V_{VSENSE} = 3 \text{ V}, -40^{\circ}\text{C} < T_A < 85^{\circ}\text{C} \text{ for the UC2854A and UC2854B, and } 0^{\circ}\text{C} < T_A < 70^{\circ}\text{C} \text{ for the UC3854A and UC3854B, and } T_A = T_J \text{ (unless otherwise of the UC3854B)}$

|                 | PARAMETER                                  | TEST CONDITIONS                                           | MIN  | TYP  | MAX  | UNIT |

|-----------------|--------------------------------------------|-----------------------------------------------------------|------|------|------|------|

| OVERA           | LL                                         |                                                           |      |      |      |      |

|                 | Supply current, off                        | $CAO = 0 V$ , $VAO = 0 V$ , $V_{CC} = V_{UVLO} - 0.3 V$   |      | 250  | 400  | μΑ   |

|                 | Supply current, on                         |                                                           |      | 12   | 18   | mA   |

|                 | V . I Ib b . l . l l                       | UCx854A                                                   | 15.0 | 16.0 | 17.5 |      |

|                 | V <sub>CC</sub> turn-on threshold voltage  | UCx854B                                                   | 8.0  | 10.5 | 11.2 |      |

|                 |                                            | UCx854A                                                   | 9    | 10   | 12   |      |

|                 | V <sub>CC</sub> turn-off threshold voltage | UCx854B                                                   | 7.8  | 10.3 | 11.0 | V    |

|                 |                                            | UCx854A                                                   | 5    | 6    | 7    |      |

|                 | V <sub>CC</sub> hysteresis                 | UCx854B                                                   | 0.10 | 0.22 | 0.50 |      |

|                 | V <sub>CC</sub> clamp                      | $I_{VCC} = I_{VCC(on)} + 5 \text{ mA}$                    | 18   | 20   | 22   |      |

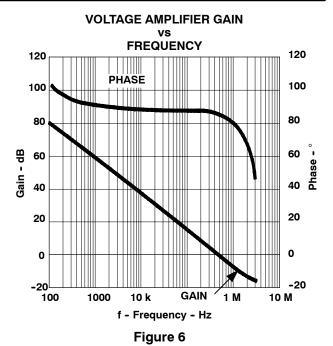

| VOLTA           | GE AMPLIFIER                               |                                                           |      | _    | _    | _    |

|                 | Input voltage                              |                                                           | 2.9  | 3.0  | 3.1  | V    |

|                 | V <sub>SENSE</sub> bias current            |                                                           | -500 | -25  | 500  | nA   |

|                 | Open loop gain                             | 2 V ≤ V <sub>OUT</sub> ≤ 5 V                              | 70   | 100  |      | dB   |

| V <sub>OH</sub> | High-level output voltage                  | $I_{LOAD} = -500 \mu$ A                                   |      | 6    |      |      |

| V <sub>OL</sub> | Low-level output voltage                   | $I_{LOAD} = 500 \mu A$                                    |      | 0.3  | 0.5  | V    |

| I <sub>SC</sub> | Output short-circuit current               | V <sub>OUT</sub> = 0 V                                    |      | 1.5  | 3.5  | mA   |

|                 | Gain bandwidth product <sup>(1)</sup>      | $f_{IN} = 100 \text{ kHz}, 	 10 \text{ mV}_{P-P}$         |      | 1    |      | MHz  |

| CURRE           | NT AMPLIFIER                               |                                                           |      |      |      |      |

|                 |                                            | $V_{CM} = 0 \text{ V}, 	 T_{A} = 25^{\circ}\text{C}$      | -4   |      | 0    | .,   |

|                 | Input offset voltage                       | V <sub>CM</sub> = 0 V, overtemperature                    | -5.5 |      | 0    | mV   |

|                 | Input bias current, I <sub>SENSE</sub>     | V <sub>CM</sub> = 0 V                                     | -500 |      | 500  | nA   |

|                 | Open loop gain                             | 2 V ≤ V <sub>OUT</sub> ≤ 6 V                              | 80   | 110  |      | dB   |

| V <sub>OH</sub> | High-level output voltage                  | $I_{LOAD} = -500 \mu$ A                                   |      | 8    |      |      |

| V <sub>OL</sub> | Low-level output voltage                   | $I_{LOAD} = 500 \mu A$                                    |      | 0.3  | 0.5  | V    |

| I <sub>SC</sub> | Output short-circuit current               | V <sub>OUT</sub> = 0 V                                    |      | 1.5  | 3.5  | mA   |

| CMRR            | Common mode rejection range                |                                                           | -0.3 |      | 5.0  | V    |

|                 | Gain bandwidth product <sup>(1)</sup>      | $f_{IN} = 100 \text{ kHz}, 	 10 \text{ mV}_{P-P}$         | 3    | 5    |      | MHz  |

| REFER           | ENCE                                       |                                                           |      |      |      |      |

|                 | Output voltage                             | $I_{REF} = 0 \text{ mA}, \qquad T_A = 25^{\circ}\text{C}$ | 7.4  | 7.5  | 7.6  | V    |

|                 | Output voltage                             | I <sub>REF</sub> = 0 mA                                   | 7.35 | 7.50 | 7.65 | V    |

|                 | Load regulation                            | $1 \text{ mA} \le I_{\text{REF}} \le 10 \text{ mA}$       | 0    | 8    | 20   | mV   |

|                 | Line regulation                            | $12 \text{ V} \leq \text{V}_{CC} \leq 18 \text{ V}$       | 0    | 14   | 25   |      |

| I <sub>SC</sub> | Short circuit current                      | V <sub>REF</sub> = 0 V                                    | 25   | 35   | 60   | mA   |

<sup>(1)</sup> Ensured by design. Not production tested.

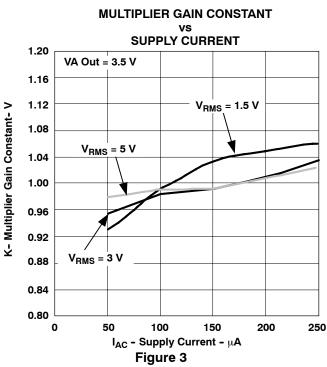

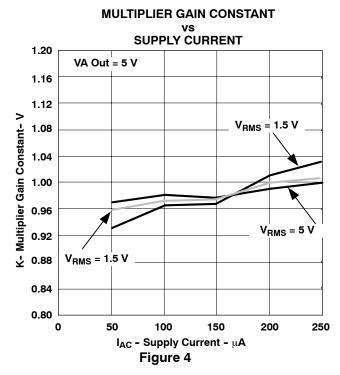

$$\text{(2) Gain constant. (K)} = \frac{I_{IAC} \times \left(V_{VAO} - 1.5 \text{ V}\right)}{\left[\left(V_{VRMS}\right)^2 \times I_{MOUT}\right]}$$

4

## **ELECTRICAL CHARACTERISTICS**

$V_{CC} = 18 \text{ V}, R_{T} = 8.2 \text{ k}\Omega, C_{T} = 1.5 \text{ nF}, V_{PKLMT} = 1 \text{ V}, V_{VRMS} = 1.5 \text{ V}, I_{IAC} = 100 \text{ }\mu\text{A}, I_{ISENSE} = 0 \text{ V}, V_{CAO} = 3.5 \text{ V}, V_{VAO} = 5 \text{ V}, V_{VSENSE} = 3 \text{ V}, -40^{\circ}\text{C} < T_{A} < 85^{\circ}\text{C} \text{ for the UC2854A and UC2854B, and } 0^{\circ}\text{C} < T_{A} < 70^{\circ}\text{C} \text{ for the UC3854A and UC3854B, and } T_{A} = T_{J} \text{ (unless otherwise the UC3854B)}$

|          | PARAMETER                                        | TEST CONDITIONS                                                                                         | MIN  | TYP  | MAX  | UNIT |

|----------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------|------|------|------|------|

| OSCIL    | LATOR                                            |                                                                                                         |      |      |      |      |

|          | Initial accuracy                                 | T <sub>A</sub> = 25°C                                                                                   | 85   | 100  | 115  | kHz  |

|          | Voltage stability                                | 12 V ≤ V <sub>CC</sub> ≤ 18 V                                                                           |      | 1%   |      |      |

|          | Total variation                                  | Line, temperature                                                                                       | 80   |      | 120  | kHz  |

|          | Ramp amplitude (peak-to-peak)                    |                                                                                                         | 4.9  |      | 5.9  |      |

|          | Ramp valley voltage                              |                                                                                                         | 0.8  |      | 1.3  | V    |

| ENABI    | _E/SOFT-START/CURRENT LIMIT                      |                                                                                                         |      |      |      |      |

|          | Enable threshold voltage                         |                                                                                                         | 2.35 | 2.55 | 2.80 | V    |

|          | Enable hysteresis                                | V <sub>FAULT</sub> = 2.5 V                                                                              |      | 500  | 600  | mV   |

|          | Enable input bias current                        | V <sub>ENA</sub> = 0 V                                                                                  |      | -2   | -5   | μΑ   |

|          | Propagation delay to disable time <sup>(1)</sup> | Enable overdrive = 100 mV                                                                               |      | 300  |      | ns   |

|          | Soft-start charge current                        | V <sub>SS</sub> = 2.5 V                                                                                 | 10   | 14   | 24   | μΑ   |

|          | Peak limit offset voltage                        |                                                                                                         | -15  |      | 15   | mV   |

|          | Peak limit input current                         | V <sub>PKLMT</sub> = -0.1 V                                                                             | -200 | -100 |      | μΑ   |

|          | Peak limit propagation delay time <sup>(1)</sup> |                                                                                                         |      | 150  |      | ns   |

| MULTI    |                                                  |                                                                                                         |      |      |      |      |

|          | Output current, I <sub>AC</sub> limited          | $\begin{split} I_{AC} &= 100 \; \mu A, & V_{RMS} &= 1 \; V, \\ R_{SET} &= 10 \; k \Omega & \end{split}$ | -220 | -200 | -170 |      |

|          | Output current, zero                             | $I_{AC}$ = 0 μA, $R_{SET}$ = 10 kΩ                                                                      | -2.0 | -0.2 | 2.0  | μΑ   |

|          | Output current, power limited                    | V <sub>RMS</sub> = 1.5 V, Va = 6 V                                                                      | -230 | -200 | -170 |      |

|          |                                                  | V <sub>RMS</sub> = 1.5 V, Va = 2 V                                                                      |      | -22  |      | μΑ   |

|          |                                                  | V <sub>RMS</sub> = 1.5 V, Va = 5 V                                                                      |      | -156 |      |      |

|          | Output current                                   | V <sub>RMS</sub> = 5 V, Va = 2 V                                                                        |      | -2   |      | μΑ   |

|          |                                                  | V <sub>RMS</sub> = 5 V, Va = 5 V                                                                        |      | -14  |      |      |

|          | Gain constant <sup>(2)</sup>                     | V <sub>RMS</sub> = 1.5 V, Va = 6V, T <sub>A</sub> = 25°C                                                | -1.1 | -1.0 | -0.9 | A/A  |

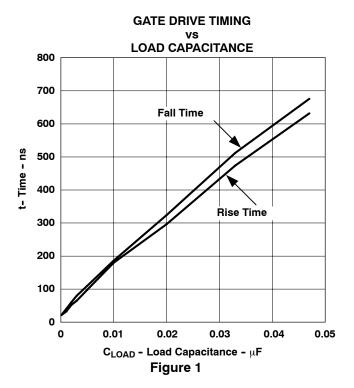

| GATE     | DRIVER                                           |                                                                                                         |      |      |      |      |

| $V_{OH}$ | High-level output voltage                        | $I_{OUT} = -200 \text{ mA},  V_{CC} = 15 \text{ V}$                                                     | 12.0 | 12.8 |      |      |

| $V_{OL}$ | Low-level output voltage                         | I <sub>OUT</sub> = 200 mA                                                                               |      | 1.0  | 2.2  | V    |

|          |                                                  | I <sub>OUT</sub> = 10 mA                                                                                |      | 300  | 500  | mV   |

|          | Low-level UVLO voltage                           | $I_{OUT} = 50 \text{ mA}, \qquad V_{CC} = 0 \text{ V}$                                                  |      | 0.9  | 1.5  | V    |

|          | Output rise time <sup>(1)</sup>                  | C <sub>LOAD</sub> = 1 nF                                                                                |      | 35   |      |      |

|          | Output fall time <sup>(1)</sup>                  | C <sub>LOAD</sub> = 1 nF                                                                                |      | 35   |      | ns   |

|          | Output peak current <sup>(1)</sup>               | C <sub>LOAD</sub> = 10 nF                                                                               |      | 1.0  |      | Α    |

<sup>&</sup>lt;sup>(1)</sup> Ensured by design. Not production tested.

$$\text{(2) Gain constant. (K)} = \frac{I_{IAC} \times \left(V_{VAO} - 1.5 \text{ V}\right)}{\left[\left(V_{VRMS}\right)^2 \times I_{MOUT}\right]}$$

## **TERMINAL FUNCTIONS**

| TERMINAL |                 | TERMINAL |          | MINAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |             |

|----------|-----------------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|

|          | <b>PACKAGES</b> |          | PACKAGES |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I/O | DESCRIPTION |

| NAME     | J/N/DW          | Q/L      |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |             |

| CAO      | 3               | 4        | 0        | Output of the wide bandwidth current amplifier and one of the inputs to the PWM duty-cycle comparator. The output signal generated by this amplifier commands the PWM to force the correct input current. The output can swing from 0.1 V to 7.5 V.                                                                                                                                                                                                                                                                                                               |     |             |

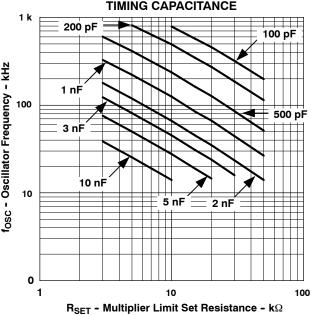

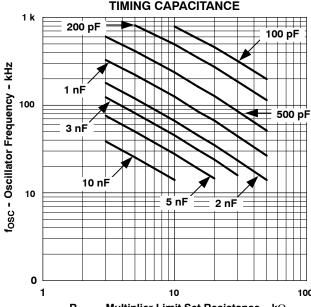

| CT       | 14              | 18       | I        | Capacitor from CT to GND sets the PWM oscillator frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |             |

| ENA      | 10              | 13       | I        | A nominal voltage above 2.65 V on this pin allows the device to begin operating. Once operating, the device shuts off if this pin goes below 2.15 V nominal.                                                                                                                                                                                                                                                                                                                                                                                                      |     |             |

| GND      | 1               | 2        | -        | All bypass and timing capacitors connected to GND should have leads as short and direct as possible. All voltages are measured with respect GND.                                                                                                                                                                                                                                                                                                                                                                                                                  |     |             |

| GTDRV    | 16              | 20       | 0        | Output of the PWM is a 1.5-A peak totem-pole MOSFET gate driver on GTDRV. Use a series gate resistor of at least 5 $\Omega$ to prevent interaction between the gate impedance and the GTDRV output driver that might cause the GTDRV output to overshoot excessively. Some overshoot of the GTDRV output is always expected when driving a capacitive load.                                                                                                                                                                                                       |     |             |

| IAC      | 6               | 8        | ı        | Current input to the multiplier, proportional to the instantaneous line voltage. This input to the analog multiplier is a current. The multiplier is tailored for very low distortion from this current input (IAC) to MOUT, so this is the only multiplier input that should be used for sensing instantaneous line voltage.                                                                                                                                                                                                                                     |     |             |

| ISENSE   | 4               | 5        | ı        | Switch current sensing input. This is the inverting input to the current amplifier. This input and the non-inverting input MOUT remain functional down to and below GND. Care should be taken to avoid taking these inputs below -0.5V, because they are protected with diodes to GND.                                                                                                                                                                                                                                                                            |     |             |

| MOUT     | 5               | 7        | I/O      | Multiplier output and current sense plus. The output of the analog multiplier and the non-inverting input of the current amplifier are connected together at MOUT. The cautions about taking ISENSE below $-0.5V$ also apply to MOUT. As the multiplier output is a current, this is a high-impedance input similar to $I_{SENSE}$ , so the current amplifier can be configured as a differential amplifier to reject GND noise. $I_{MOUT} \le 2 \times I_{AC}$                                                                                                   |     |             |

| PKLMT    | 2               | 3        | I        | Peak limit. The threshold for PKLMT is 0.0 V. Connect this input to the negative voltage on the current sense resistor. Use a resistor to REF to offset the negative current sense signal up to GND.                                                                                                                                                                                                                                                                                                                                                              |     |             |

| RSET     | 12              | 15       | ı        | Oscillator charging current and multiplier limit set. A resistor from RSET to ground programs oscillator charging current.                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |             |

| SS       | 13              | 17       | ı        | Soft-start. SS remains at GND as long as the device is disabled or $V_{CC}$ is too low. SS pulls up to over 3 V by an internal 14- $\mu$ A current source when both $V_{CC}$ becomes valid and the device is enabled. SS acts as the reference input to the voltage amplifier if SS is below VREF. With a large capacitor from SS to GND, the reference to the voltage regulating amplifier rises slowly, and increase the PWM duty cycle slowly. In the event of a disable command or a supply dropout, SS will quickly discharge to ground and disable the PWM. |     |             |

| VAO      | 7               | 9        | I        | Voltage amplifier output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |             |

| VCC      | 15              | 19       | I        | Positive supply rail                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |             |

| VREF     | 9               | 12       | 0        | Used to set the peak limit point and as an internal reference for various device functions. This voltage must be present for the device to operate.                                                                                                                                                                                                                                                                                                                                                                                                               |     |             |

| VRMS     | 8               | 10       | I        | One of the inputs into the multiplier. This pin provides the input RMS voltage to the multiplier circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |             |

| VSENSE   | 11              | 14       | I        | This pin provides the feedback from the output. This input goes into the voltage error amplifier and the output of the error amplifier is another of the inputs into the multiplier circuit.                                                                                                                                                                                                                                                                                                                                                                      |     |             |

## **FUNCTIONAL DESCRIPTION**

The UC3854A and UC3854B family of products are designed as pin compatible upgrades to the industry standard UC3854 active power factor correction circuits. The circuit enhancements allow the user to eliminate in most cases several external components currently required to successfully apply the UC3854. In addition, linearity improvements to the multiply, square and divide circuitry optimizes overall system performance. Detailed descriptions of the circuit enhancements are provided below. For in-depth design applications reference data refer to the application notes, *UC3854 Controlled Power Factor Correction Circuit Design* (SLUA144) and *UC3854A and UC3854B Advanced Power Factor Correction Control ICs* (SLUA177).

## Multiply/Square and Divide

The UC3854A/B multiplier design maintains the same gain constant  $\left(K = \frac{-1}{V}\right)$  as the UC3854. The relationship between the inputs and output current is given as:

$$I_{MOUT} = I_{iAC} \times \frac{(V_{VAO} - 1.5 V)}{K \times (V_{VRMS})^2}$$

(1)

This is nearly the same as the UC3854, but circuit differences have improved the performance and application.

The first difference is with the IAC input. The UC3854A/B regulated this pin voltage to the nominal 500 mV over the full operating temperature range, rather than the 6.0 V used on the UC3854. The low offset voltage eliminates the need for a line zero crossing compensating resistor to VREF from IAC that UC3854 designs require. The maximum current at high line into IAC should be limited to 250  $\mu$ A for best performance.

Therefore, if  $V_{VAC(max)} = 270 \text{ V}$ ,

$$R_{IAC} = \frac{270 \times 1.414}{250 \,\mu\text{A}} = 1.53 \,\text{M}\Omega \tag{2}$$

The  $V_{RMS}$  pin linear operating range is improved with the UC3854A/B as well. The input range for VRMS extends from 0 V to 5.5 V. Since the UC3854A squaring circuit employs an analog multiplier, rather than a linear approximation, accuracy is improved, and discontinuities are eliminated. The external divider network connected to VRMS should produce 1.5 V at low line (85 VAC). This puts 4.77 V on VRMS at high line (270 VAC) which is well within its operating range.

The voltage amplifier output forms the third input to the multiplier and is internally clamped to 6.0 V. This eliminated an external zener clamp often used in UC3854 designs. The offset voltage at this input to the multiplier has been raised on the UC3854A/B to 1.5 V.

The multiplier output pin, which is also common to the current amplifier non-inverting input, has a -0.3 V to 5.0 V output range, compared to the -0.3 V to 2.5 V range of the UC3854. This improvement allows the UC3854A/B to be used in applications where the current sense signal amplitude is very large.

## Voltage Amplifier

The UC3854A/B voltage amplifier design is essentially similar to the UC3854 with two exceptions. The first is with the internal connection. The lower voltage reduces the amount of charge on the compensation capacitors, which provides improved recovery form large signal events, such as line dropouts, or power interruption. It also minimizes the dc current flowing through the feedback. The output of the voltage amplifier is also changes. In addition to a 6.0 V temperature compensated clamp, the output short circuit current has been lowered to 2 mA typical, and an active pull down has replaced the passive pull down of the UC3854.

## UC1854B UC2854A, UC2854B UC3854A, UC3854B

SLUS329E - JUNE 1998 - REVISED AUGUST 2006

## **Current Amplifier**

The current amplifier for an average current PFC controller needs a low offset voltage in order to minimize AC line current distortion. With this in mind, the UC3854A/B current amplifier has improved the input offset voltage from ±4 mV to 0 V to ±3 mV. The negative offset of the UC3854A/B guarantees that the PWM circuit will not drive the MOSFET is the current command is zero (both current amplifier inputs zero.) Previous designs required an external offset cancellation network to implement this key feature. The bandwidth of the current amplifier has been improved as well to 5 MHz typical. While this is not generally an issue at 50 Hz or 60 Hz inputs, it is essential for 400 Hz input avionics applications

## Miscellaneous

Several other important enhancements have been implemented in the UC3854A/B. A  $V_{CC}$  supply voltage clamp at 20 V allows the controller to be current fed if desired. The lower startup supply current (250  $\mu$ A typical), substantially reduces the power requirements of an offline startup resistor. The 10.5 V/10 V UVLO option (UC3854B) enables the controller to be powered off of an auxiliary 12 V supply.

The VREF GOOD comparator guarantees that the MOSFET driver output remains low if the supply of the 7.5 V reference are not yet up. This improvement eliminates the need for external Schottky diodes on the PKLMT and Mult Out pins that some UC3854 designs require. The propagation delay of the disable feature has been improved to 300 ns typical. This delay was proportional to the size of the VREF capacitor on the UC3854, and is typically several orders of magnitude slower.

## **TYPICAL CHARACTERISTICS**

**OSCILLATOR FREQUENCY LIMIT SET RESISTANCE AND** TIMING CAPACITANCE

Figure 7

10

## **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| 5962-9326102M2A  | OBSOLETE              | LCCC            | FK                 | 20   |                | TBD                       | Call TI          | Call TI                      |

| 5962-9326102MEA  | ACTIVE                | CDIP            | J                  | 16   | 1              | TBD                       | A42 SNPB         | N / A for Pkg Type           |

| UC1854BJ         | ACTIVE                | CDIP            | J                  | 16   | 1              | TBD                       | A42 SNPB         | N / A for Pkg Type           |

| UC1854BJ883B     | ACTIVE                | CDIP            | J                  | 16   | 1              | TBD                       | A42 SNPB         | N / A for Pkg Type           |

| UC1854BL         | OBSOLETE              | TO/SOT          | L                  | 20   |                | TBD                       | Call TI          | Call TI                      |

| UC1854BL883B     | OBSOLETE              | TO/SOT          | L                  | 20   |                | TBD                       | Call TI          | Call TI                      |

| UC2854ADW        | ACTIVE                | SOIC            | DW                 | 16   | 40             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UC2854ADWG4      | ACTIVE                | SOIC            | DW                 | 16   | 40             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UC2854ADWTR      | ACTIVE                | SOIC            | DW                 | 16   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UC2854ADWTRG4    | ACTIVE                | SOIC            | DW                 | 16   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UC2854AN         | ACTIVE                | PDIP            | N                  | 16   | 25             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type           |

| UC2854ANG4       | ACTIVE                | PDIP            | N                  | 16   | 25             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type           |

| UC2854BDW        | ACTIVE                | SOIC            | DW                 | 16   | 40             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UC2854BDWG4      | ACTIVE                | SOIC            | DW                 | 16   | 40             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UC2854BDWTR      | ACTIVE                | SOIC            | DW                 | 16   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UC2854BDWTRG4    | ACTIVE                | SOIC            | DW                 | 16   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UC2854BJ         | ACTIVE                | CDIP            | J                  | 16   | 1              | TBD                       | A42 SNPB         | N / A for Pkg Type           |

| UC2854BN         | ACTIVE                | PDIP            | N                  | 16   | 25             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type           |

| UC2854BNG4       | ACTIVE                | PDIP            | N                  | 16   | 25             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type           |

| UC2854BQ         | ACTIVE                | PLCC            | FN                 | 20   | 46             | Green (RoHS & no Sb/Br)   | CU SN            | Level-2-260C-1 YEAR          |

| UC2854BQG3       | ACTIVE                | PLCC            | FN                 | 20   | 46             | Green (RoHS & no Sb/Br)   | CU SN            | Level-2-260C-1 YEAR          |

| UC3854ADW        | ACTIVE                | SOIC            | DW                 | 16   | 40             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UC3854ADWG4      | ACTIVE                | SOIC            | DW                 | 16   | 40             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UC3854ADWTR      | ACTIVE                | SOIC            | DW                 | 16   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UC3854ADWTRG4    | ACTIVE                | SOIC            | DW                 | 16   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UC3854AN         | ACTIVE                | PDIP            | N                  | 16   | 25             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type           |

| UC3854ANG4       | ACTIVE                | PDIP            | N                  | 16   | 25             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type           |

| UC3854BDW        | ACTIVE                | SOIC            | DW                 | 16   | 40             | Green (RoHS &             | CU NIPDAU        | Level-2-260C-1 YEAR          |

## PACKAGE OPTION ADDENDUM

12-Sep-2006

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

|                  |                       |                 |                    |      |                | no Sb/Br)                 |                  |                              |

| UC3854BDWG4      | ACTIVE                | SOIC            | DW                 | 16   | 40             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UC3854BDWTR      | ACTIVE                | SOIC            | DW                 | 16   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UC3854BDWTRG4    | ACTIVE                | SOIC            | DW                 | 16   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| UC3854BN         | ACTIVE                | PDIP            | N                  | 16   | 25             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type           |

| UC3854BNG4       | ACTIVE                | PDIP            | N                  | 16   | 25             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type           |

| UC3854BQ         | OBSOLETE              |                 | UTR                | 20   |                | TBD                       | Call TI          | Call TI                      |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products           |                        | Applications       |                           |

|--------------------|------------------------|--------------------|---------------------------|

| Amplifiers         | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters    | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP                | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface          | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic              | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt         | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers   | microcontroller.ti.com | Security           | www.ti.com/security       |

| Low Power Wireless | www.ti.com/lpw         | Telephony          | www.ti.com/telephony      |

|                    |                        | Video & Imaging    | www.ti.com/video          |

|                    |                        | Wireless           | www.ti.com/wireless       |

|                    |                        |                    |                           |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2006, Texas Instruments Incorporated