### A 607 MHz time-compressive computational pseudo-dToF CMOS image sensor

Pham Ngoc Anh<sup>1</sup>, Thoriq Ibrahim<sup>1</sup>, Keita Yasutomi<sup>2</sup>, Shoji Kawahito<sup>2</sup>, Hajime Nagahara<sup>3</sup>, Keiichiro Kagawa<sup>2</sup>

<sup>1</sup> Graduate School of Integrated Science and Technology, Shizuoka University 3-5-1 Johoku, Naka Ward, Hamamatsu, Shizuoka, Japan 432-8011

<sup>2</sup> Research Institute of Electronics, Shizuoka University 3-5-1 Johoku, Naka Ward, Hamamatsu, Shizuoka, Japan 432-8011

<sup>3</sup> Institute for Datability Science, Osaka University

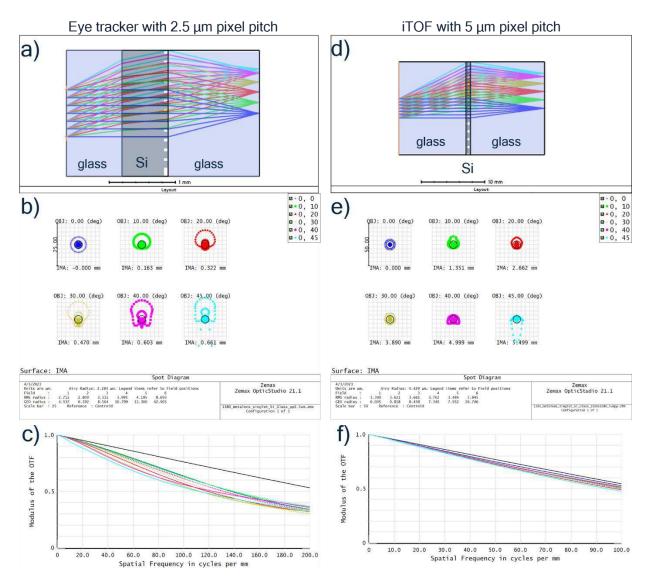

2-8, Yamadaoka, Suita, Osaka, Japan 565-0871

Email: <u>kagawa@idl.rie.shizuoka.ac.jp</u>

Abstract - This paper demonstrates a pseudo-direct time-of-flight (pseudo-dToF) CMOS image sensor that is robust to multipath interference (MPI) and has high distance accuracy and precision. This method uses an iToF-based image sensor, but can reconstruct the received light waveforms similar to those obtained by conventional dToF image sensors based on single-photon avalanche diode (SPAD). Therefore, this method has the advantages of both dToF and iToF depth image sensors such as high resolution, high accuracy, immunity to MPI, and motion-artifact-free. This paper presents a signal reconstruction scheme for our laboratory-designed timecompressive image sensor based on the charge domain compressive sensing. Two approaches to refine the depth resolution are explained: 1) Increasing the operating clock speed; 2) Oversampling in image reconstruction and quadratic fitting in depth calculation. Experimental results show the separation of two reflections 40 cm apart under an MPI condition, and a significant improvement in distance precision down to 1 cm order. These results suggest that this method could be a promising approach to virtually implement dToF imaging suitable for challenging environments with MPI.

#### I. INTRODUCTION

Time-of-flight (ToF) depth imaging calculates the distance of an object by measuring the travel time of light emitted from the camera to the object and back to the camera. This method is increasingly utilized in the fields of robotics and automotive applications. In ToF cameras, each pixel provides a specific depth value. However, the target scene may involve multiple light paths that interact with the same pixel, resulting in depth images that can contain scene-dependent errors due to multipath interference (MPI).

There are two major methodologies for traditional ToF depth imaging: direct ToF (dToF) and indirect ToF (iToF). The dToF sensor, based on the single electron avalanche diode (SPAD) [1], directly measures the reflected light waveforms, making it immune to MPI. However, it requires a larger circuit area for time-todigital converters and histogram builders. In contrast, the iToF sensor [2] has a smaller circuit area and can estimate the depth with a higher spatial resolution, but it is susceptible to MPI. This is because it calculates the depth from the number of charges that correlate the incident light waveform with a demodulation function applied to the modulator.

In this work, we propose a new measurement method called pseudo-dToF, which provides the advantages of both dToF and iToF. This method utilizes iToF-based high-speed charge modulators, allowing for high-resolution imaging similar to iToF image sensors. Moreover, the time-compressive sensing in the charge domain enables the sensor to reproduce the entire light waveform in a single shot. Therefore, pseudo-dToF realizes high accuracy in depth and motion artifact-free measurement. We also present two approaches to achieve higher temporal resolution and report the improvements in depth accuracy and precision by experiments.

#### II. PSEUDO–DTOF DEPTH IMAGING

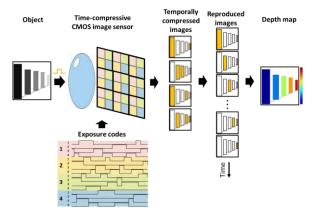

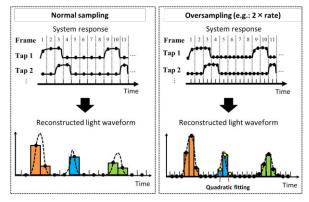

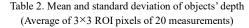

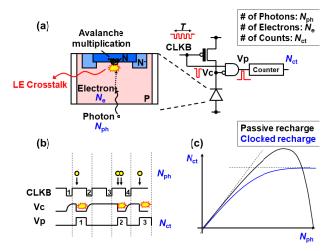

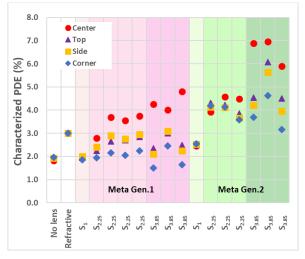

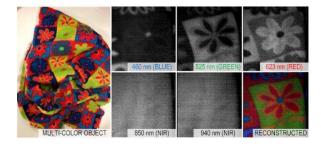

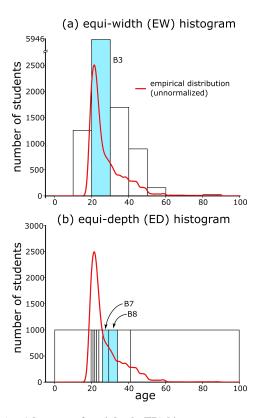

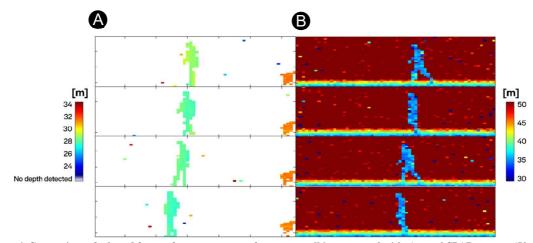

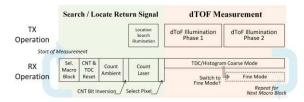

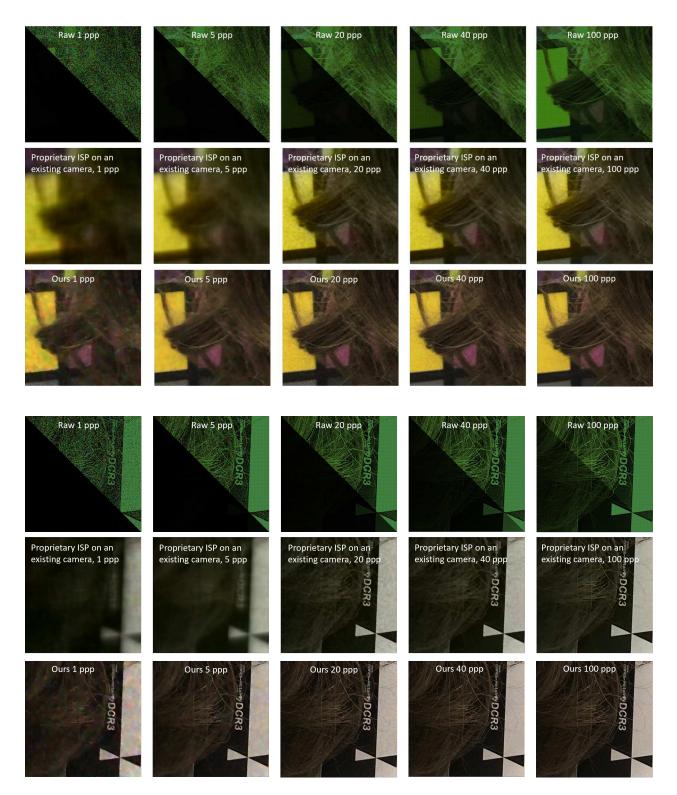

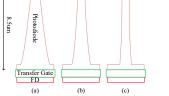

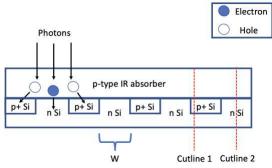

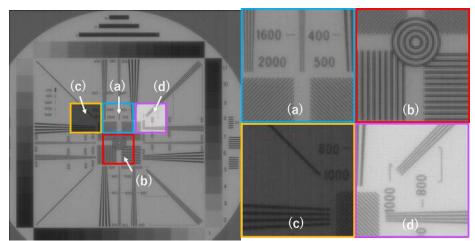

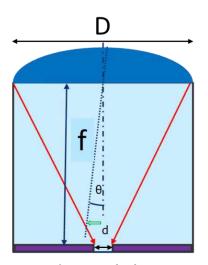

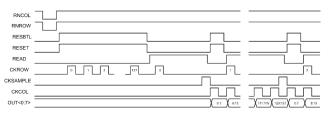

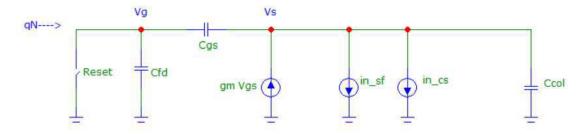

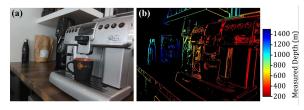

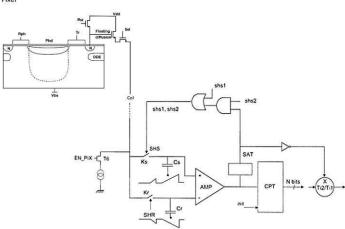

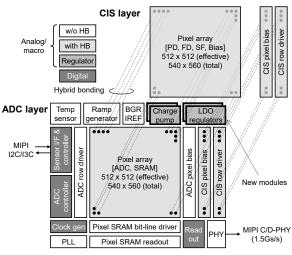

Fig. 1. Image acquisition and reconstruction flow

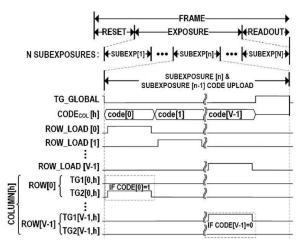

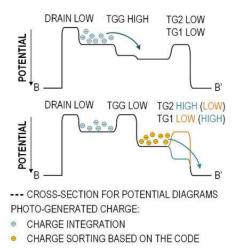

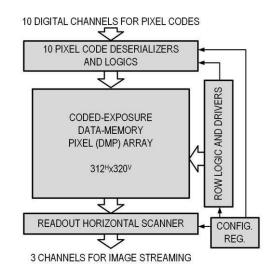

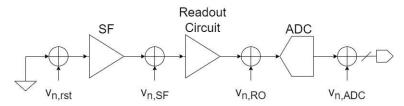

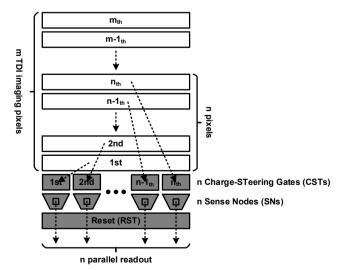

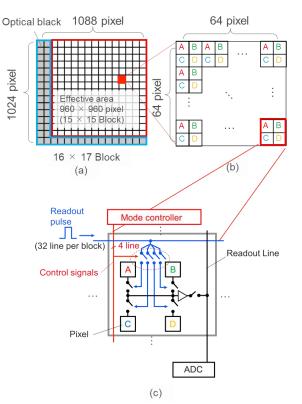

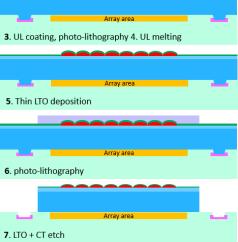

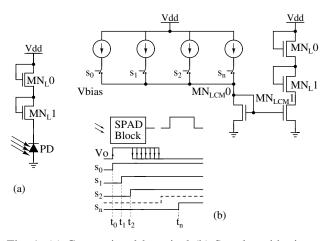

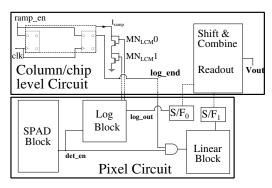

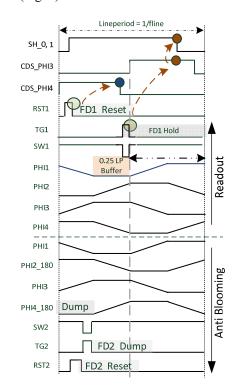

In our scheme, incident light signals are temporally compressed in the charge domain and reconstructed in three phases: pre-measurement, sensing, and signal reconstruction.

Firstly, we prepare exposure codes and measure the instrument response function (IRF) of the imaging optics and the image sensor in advance, which are used for signal reconstruction later.

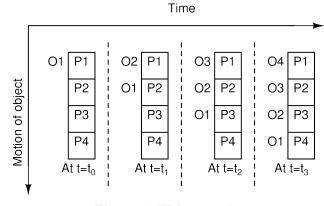

In the sensing phase, the camera captures temporal signals of light emitted from a synchronized laser and reflected from objects. As shown in Fig. 1, the image sensor is composed of macro-pixels based on charge modulators. By applying exposure codes to the pixels during the image shooting, multiple temporally compressed images (four in Fig. 1) are obtained at once.

In the reconstruction phase, the input optical waveforms for all subpixels are reproduced by solving the inverse problem based on the sparsity regularization. Thus, temporally sequential images or transient images of light are obtained. Subsequently, the temporal peak positions of the light waveform are detected with a quadratic curve fitting. Finally, they are converted to the object's depth using the speed of light.

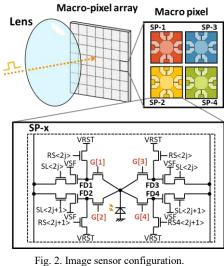

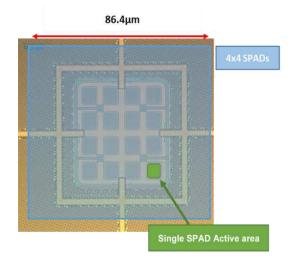

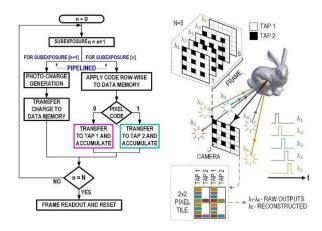

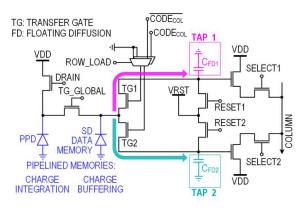

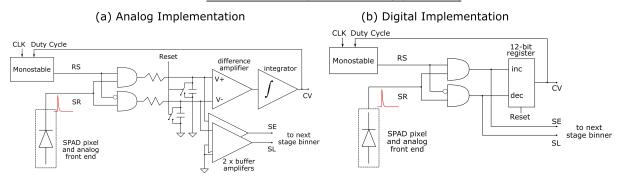

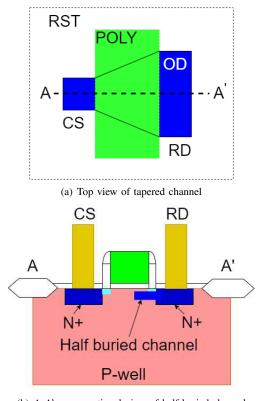

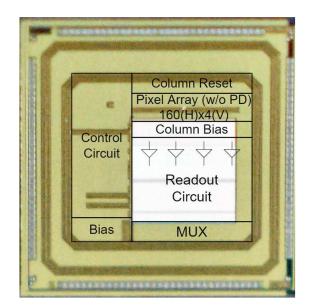

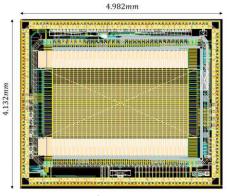

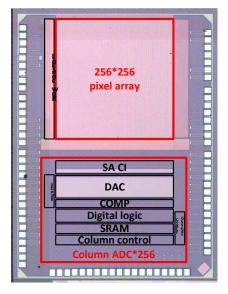

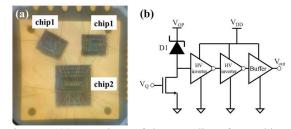

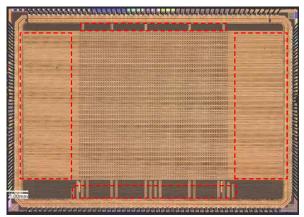

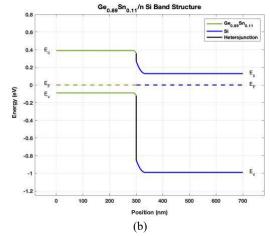

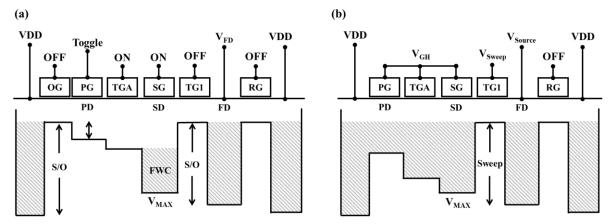

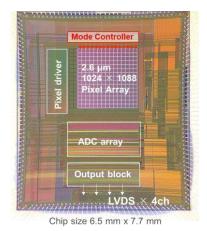

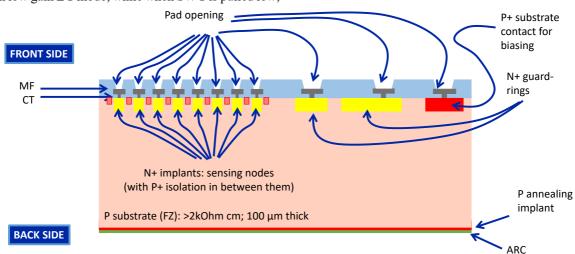

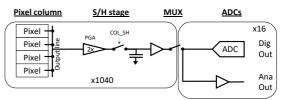

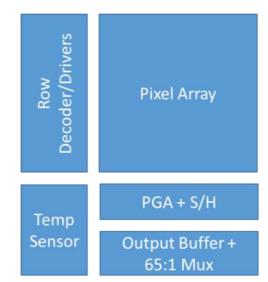

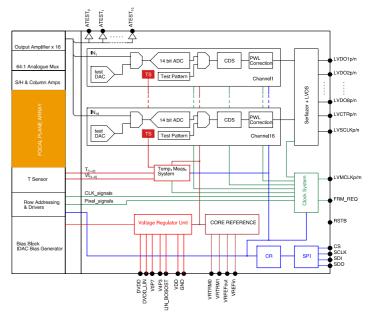

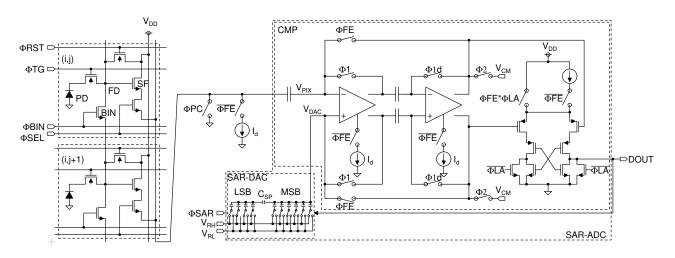

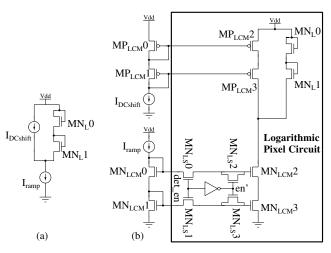

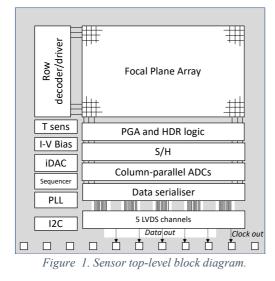

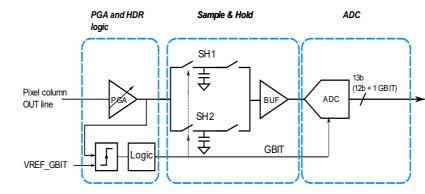

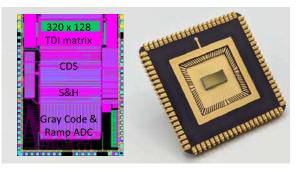

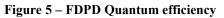

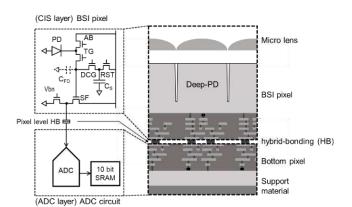

#### a) Multi-tap macro-pixel CMOS image sensor

This sensor utilizes iToF-based charge modulators, which contribute to small pixel size or high-spatialresolution imaging.

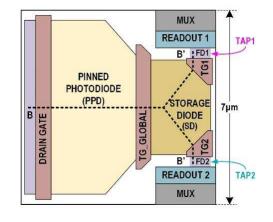

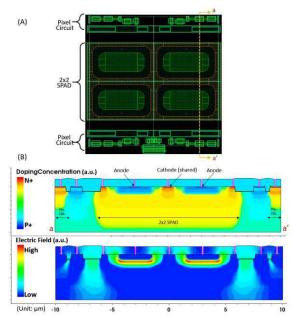

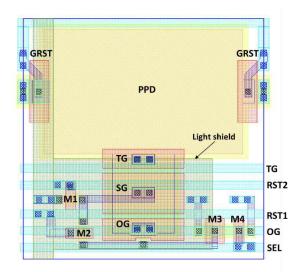

One macro pixel is composed of  $2 \times 2$  four-tap subpixels.

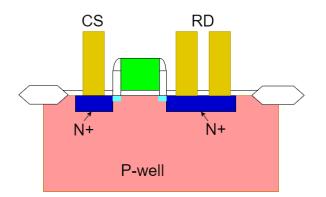

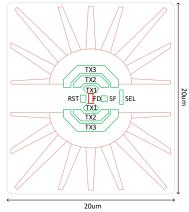

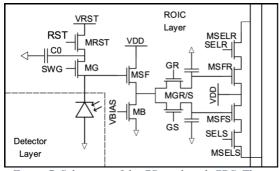

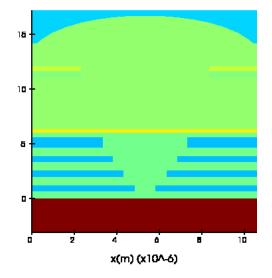

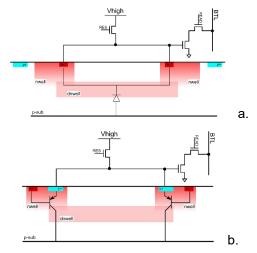

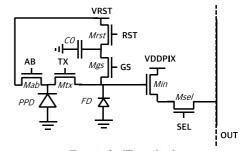

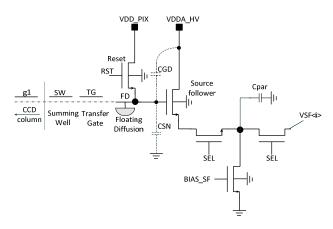

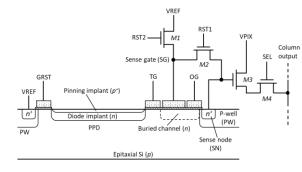

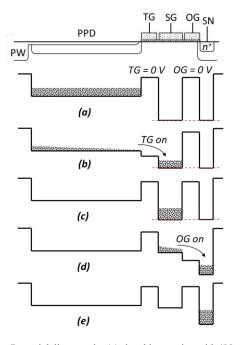

Figure 2 shows the pixel structure, which comprises an array of four sub-pixels (SPs) for each macro-pixel. Each sub-pixel is implemented by a four-tap LEFM charge modulator [3]. The LEFM charge modulator is composed of a photodiode and four sets of a charge transfer gate and a storage diode (tap). It outputs the integral value of a time-variant optical signal g(t) within a designated time window function  $\omega_i(t)$  as a pixel value  $Q_i$  (Eq. 1). Here, the index *i* identifies a tap.

$$Q_i = \int_0^{T_{exp}} g(t) \cdot \omega_i(t) dt \qquad \text{Eq. 1}$$

The high-speed operation of LEFM pixels allows for high temporal resolution. In our previous research, we confirmed that the sensor can be driven at a clock frequency of up to 303 MHz [4].

#### b) Compressive sensing

Compressive sensing [5] is an efficient sampling method that reconstructs more data points from fewer samples when the original signal is sparse. We employ this principle to reconstruct the entire incident light waveform from the compressed output images, resulting in dToF-like signals with high-depth accuracy and robustness to MPI, like the conventional dToF method. Note that compressed images are obtained in a single shot, which makes our sensor motion-artifact-free.

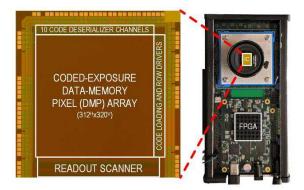

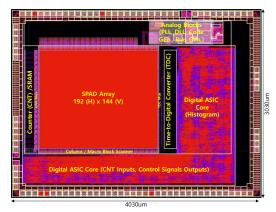

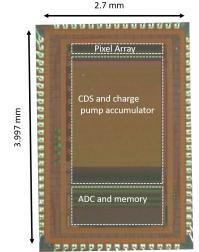

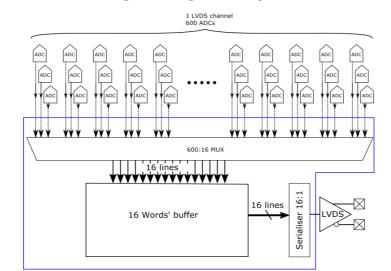

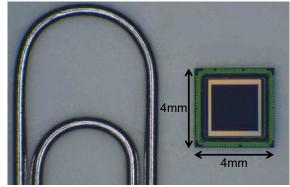

Table 1. Sensor architecture

| Technology                      | 0.11 μm FSI CIS                                |

|---------------------------------|------------------------------------------------|

| Chip size                       | $7.0 \text{ mm}^{H} \times 9.3 \text{ mm}^{V}$ |

| Macro-pixel size                | $22.4~\mu m^{H}\!\!\times\!\!22.4~\mu m^{V}$   |

| Effective sub-pixel count       | $212^{H} \times 188^{V}$                       |

| Sub-pixel count per macro-pixel | $2^{H} \times 2^{V}$                           |

| Maximum exposure code length    | 256 bits                                       |

| Maximum modulation frequency    | 303 MHz                                        |

| Maximum clock frequency         | 607 MHz                                        |

| Image readout frame rate        | 21 fps                                         |

| Power consumption               | 2.8 W                                          |

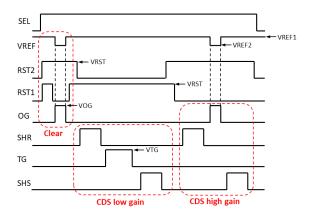

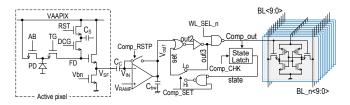

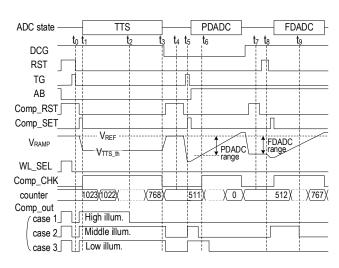

Our sensor utilizes a coded exposure pattern that is a temporal series of random binary values to create timecompressed signals. When the exposure code is 0, no charge is transferred to a specific tap, and when it is 1, the charge is stored in the tap. Therefore, the number of charges accumulated in each tap corresponds to the correlation value between the input light signal and the coded exposure pattern, resulting in temporally compressed images. The exposure codes are repeatedly applied to increase the pixel value.

Time-compressive sensing and signal reconstruction are as follows. Consider the input signal is x and the corresponding measurement signal is y, their relation can be expressed by the following linear equation:

$$y = Ax = (WH)Px$$

Eq. 2

Here, matrix A is a spatio-temporal observation matrix that includes the spatial IRF of the imaging optics P, the exposure code W and the sensor's temporal IRF H. The dimensions of x, y, and A are N, M, and  $M \times N$ , respectively. In cases where N > M, i.e., the measured signal is lower in dimensionality than the original input signal, the signal is compressed. Retrieving the original input signal x from y is an ill-posed problem. However, if x is K-sparse, meaning that only K elements have non-zero values, we can determine the estimated solution for x by optimizing the L1 norm.

Based on this principle, the reflected light waveform x of all sub-pixels is reconstructed from the four compressed images y and the pre-measured observation matrix A. In this process, total variation is minimized instead of the L1 norm as shown in Eq. 3. Here,  $D_i$  shows a spatio-temporal differential operator. This process is performed by TVAL3 [6], a compressed sensing solver, using an iterative method.

$$\widehat{x}^{(TV)} = \arg\min_{x} \sum_{i} \|D_{i}x\|_{1}$$

, s.t.  $y = Ax$  Eq. 3

Thus, transient images of light are reproduced, providing depth information. The depth accuracy and precision are dependent on the frame rate of the transient images. The temporal resolution of the reconstructed signal is determined by the reciprocal of this frame rate, which is also equal to the minimum duration of the exposure code. For example, if our sensor operates at 303 MHz and uses a 32-bit exposure code, the temporal resolution is 3.3 ns (0.5 m in depth), and the measurable distance is 16 m.

To generate a depth map from the reconstructed images, the reconstructed waveform for each pixel is analyzed to determine the temporal peak position, which corresponds to the round-trip ToF. Finally, it is converted into a depth value using the speed of light.

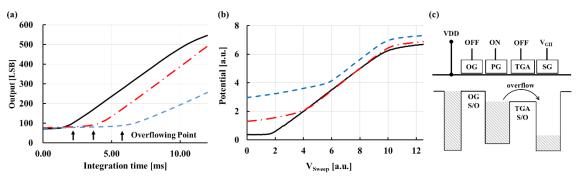

#### III. IMPROVEMENT OF DEPTH RESOLUTION

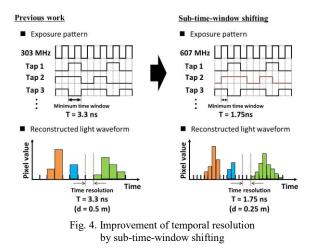

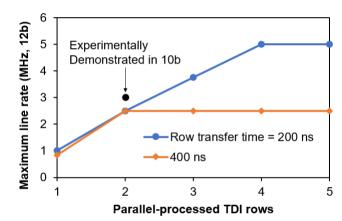

So far, we have succeeded in ToF imaging at an operating clock frequency of 303 MHz [4]. This allowed the minimum time window with a duration of 3.3 ns, which corresponded to a 0.5 m resolution. Generally, higher depth resolution can be achieved simply by increasing the operating frequency of the charge modulator. However, driving the charge modulation at a higher frequency is highly dependent on the fabrication technology and modulator structure. It was challenging to achieve a minimum time window duration of less than 3.3 ns for our modulators. To overcome such restrictions, the following two approaches were applied to obtain higher depth resolution.

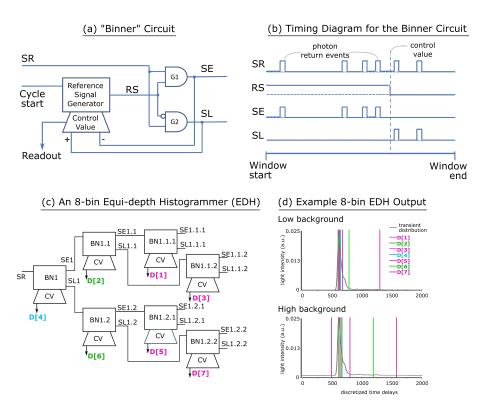

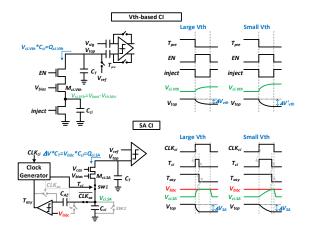

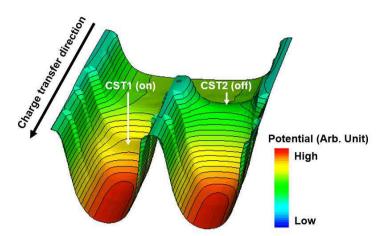

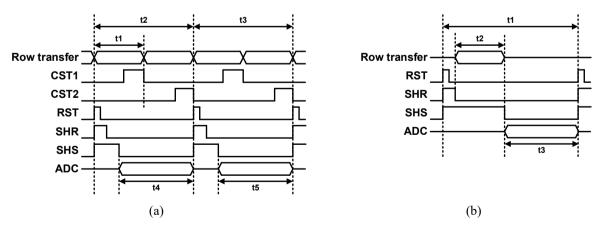

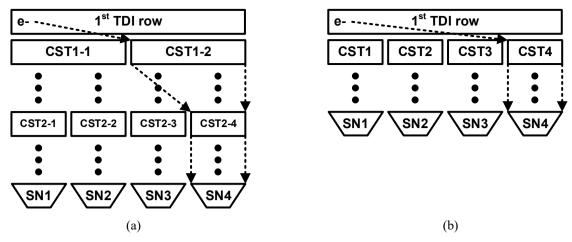

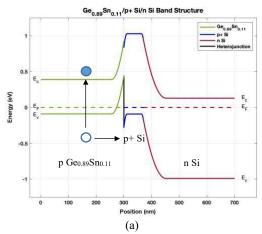

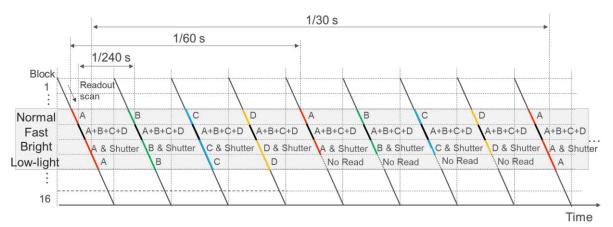

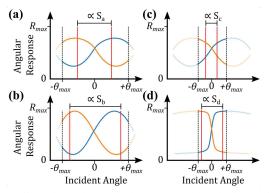

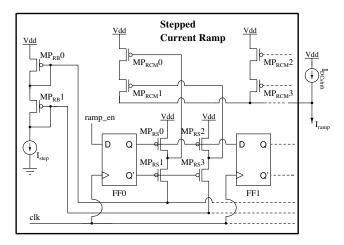

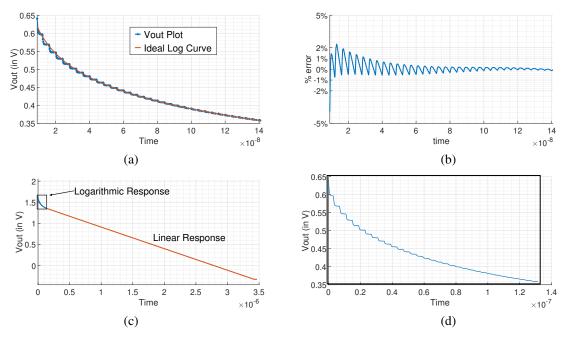

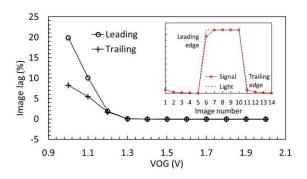

#### a) Sub-time-window shifting

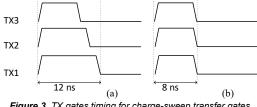

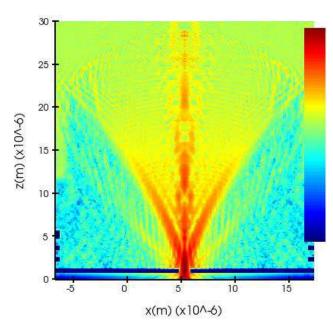

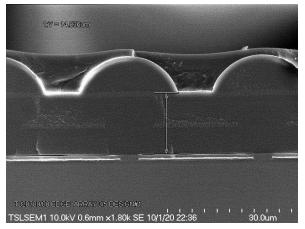

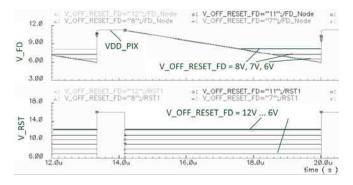

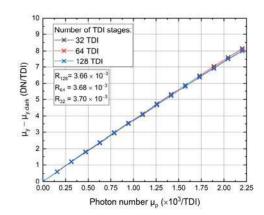

Here, sub-time-window shifting of the exposure code is introduced to enhance the temporal resolution without changing the minimum time window duration, which is determined by the modulator design. To implement the sub-time-window shifting, we double the PLL clock frequency from 303 MHz to 607 MHz, while maintaining the minimum time window duration at 3.3 ns, equivalent to two clocks. Then, as shown in Figure 4, the falling and rising edges of the time window are shifted by one clock, which is half of the minimal time window. As a result, the temporal resolution is halved down to 1.75 ns.

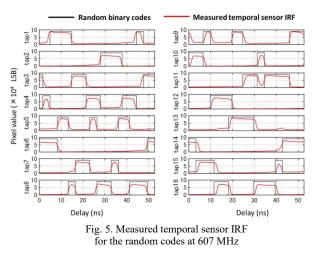

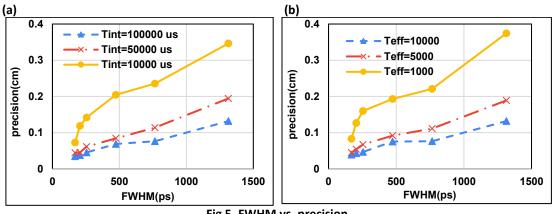

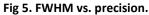

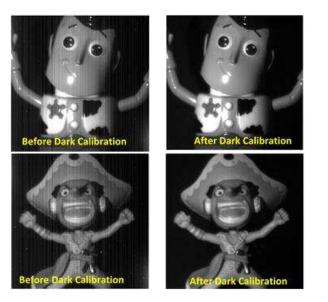

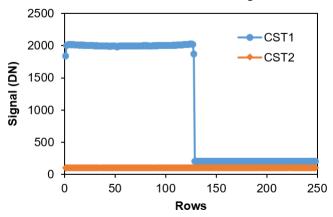

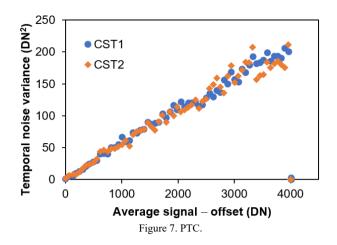

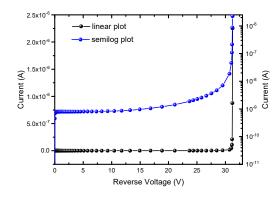

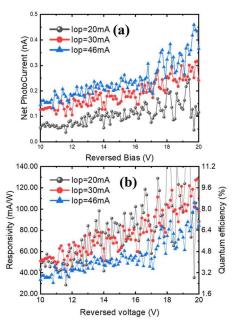

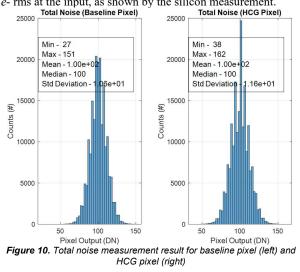

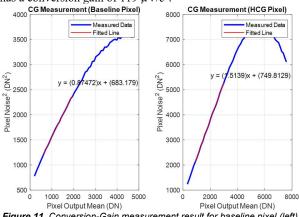

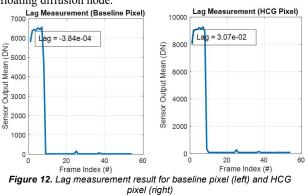

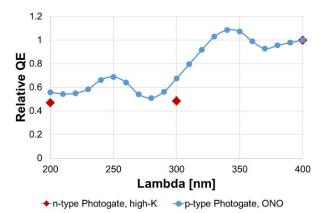

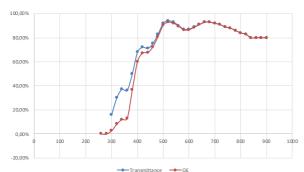

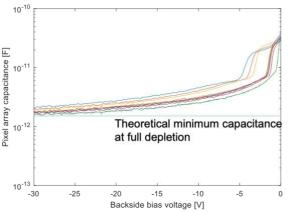

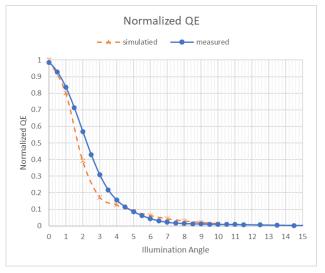

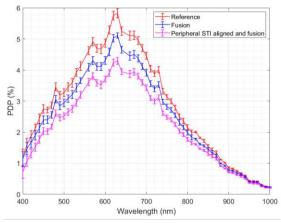

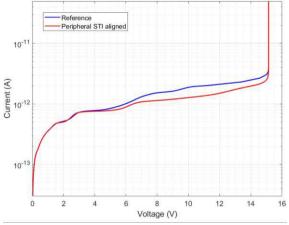

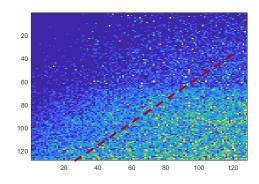

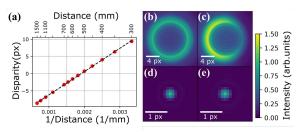

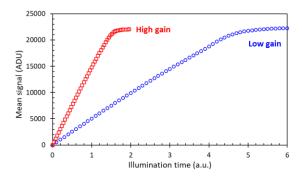

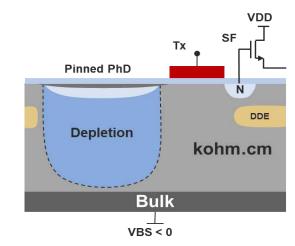

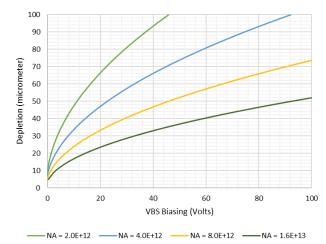

Figure 5 shows the temporal sensor IRF measured

when this sensor was operated at 607 MHz. The exposure code was a 32-bit random binary code, and a 445 nm laser with an FWHM of 60 ps was used. The results were averaged for each tap. It can be observed that charge modulation was successfully performed.

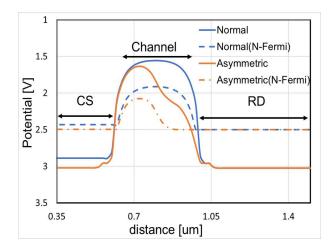

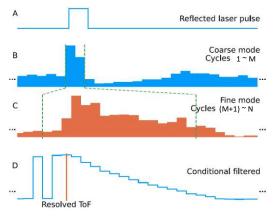

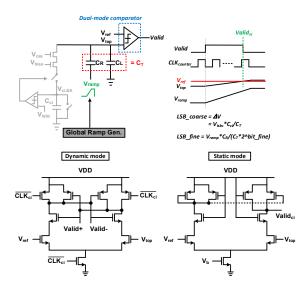

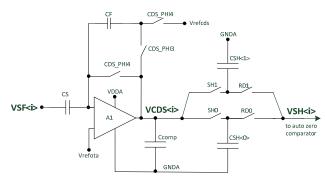

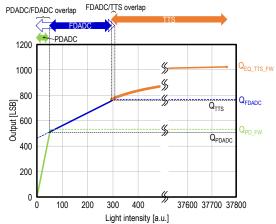

#### b) Oversampling

Another approach to improve the temporal resolution is oversampling the sensor's IRFs, i.e., increasing the number of data points of the premeasured observation matrix used for reconstruction. Previously, the sensor response was sampled once per bit of the exposure code. However, in this study, we have sub-sampled 10 points per bit ( $10 \times$  oversampling), as depicted in Fig. 6. The temporal (or depth) resolution is then improved, resulting in a denser reconstructed light waveform. Since the signal waveforms can be obtained as in dToF imaging, we can perform fitting to refine the depth. After the peak position in the waveform is detected from the reproduced signal waveform, the five data points around the peak are considered in fitting with a quadratic curve.

Fig. 6. Oversampling pre-measured sensor's IRF and fitting

The proposed method works better with oversampling, as denser light waveforms are utilized in fitting, resulting in more accurate depth estimation. Moreover, even if there are multiple peaks due to MPI, each peak can be distinguished and separately detected. Note that the depth resolution can be improved without changing the image sensor hardware or the total measurement time, although the reconstruction process takes longer.

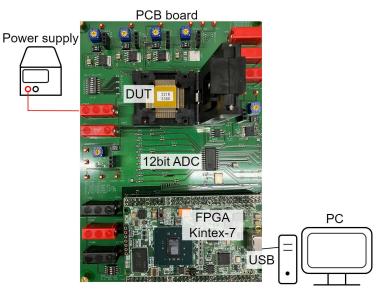

#### **IV. EXPERIMENTS**

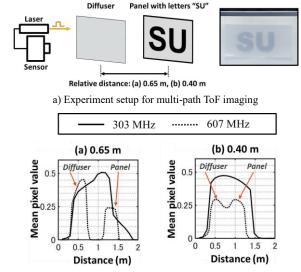

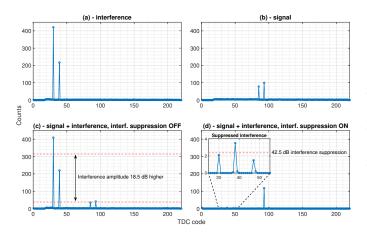

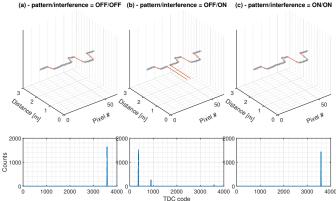

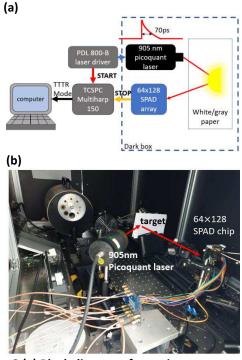

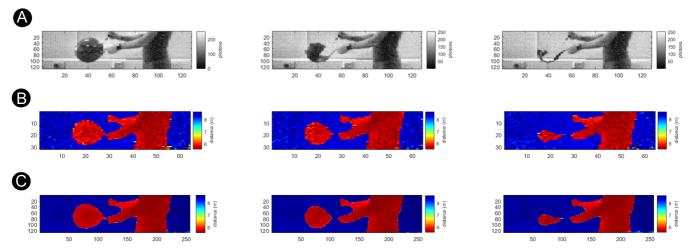

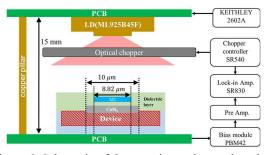

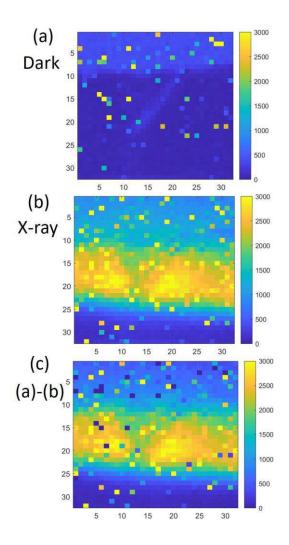

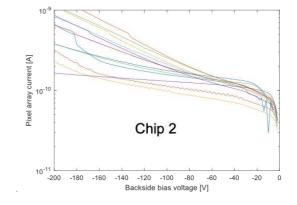

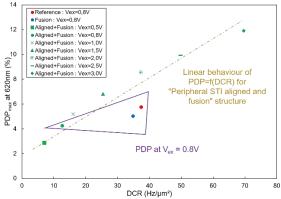

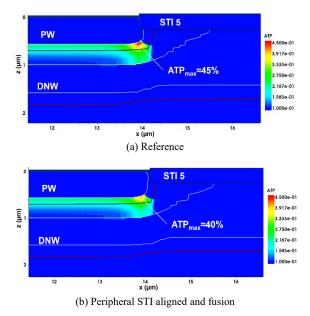

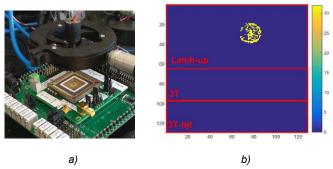

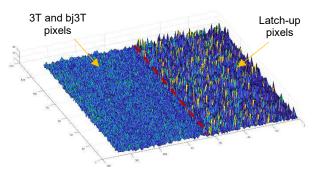

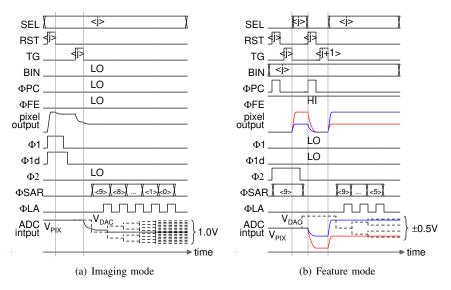

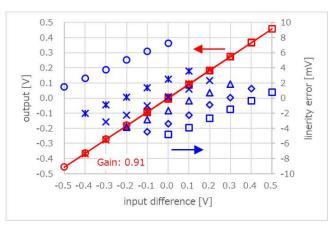

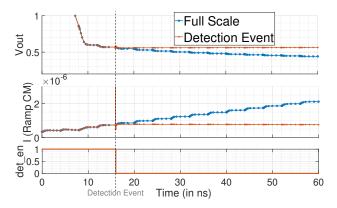

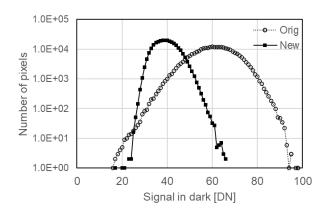

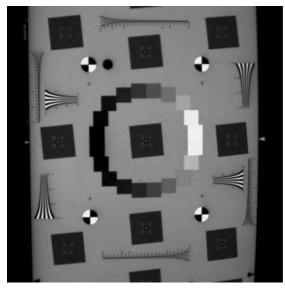

To evaluate the improvement of depth resolution after increasing the clock frequency from 303 MHz to 607 MHz, we compared the peaks separation performance under MPI conditions. In this experiment, interference light was introduced by a weak diffusive plastic sheet placed in front of an objective panel with the letters "SU" as shown in Fig. 7a. The letters look blurry due to the diffuser. The distance between the two objects was set to 0.65 m and 0.40 m, and experiments were conducted with the sensor operating at 303 MHz and 607 MHz. A short-pulse semiconductor laser (PicoQuant LDH-IB-450-M-P, 443 nm) with a pulse width of 228 ps was used.

Figure 7b shows the reconstruction of optical waveforms at two clock frequencies. At 303 MHz, the interference light due to the diffuser was merged with the objective reflection for both clearances and could not be separated. However, when the clock frequency was increased to 607 MHz, the two reflections were completely separated for the 0.65 m clearance. For the 0.40 m clearance, although there was an overlap between the two signals, the object's reflection peak could be distinguished. These results show that the MPI is resolved in the 607 MHz operations.

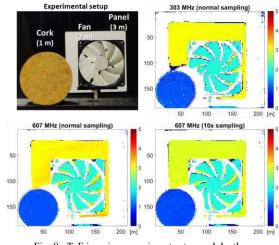

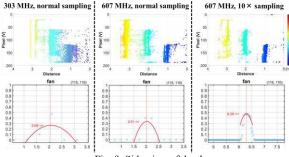

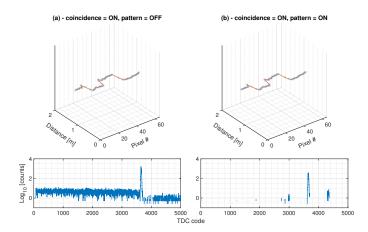

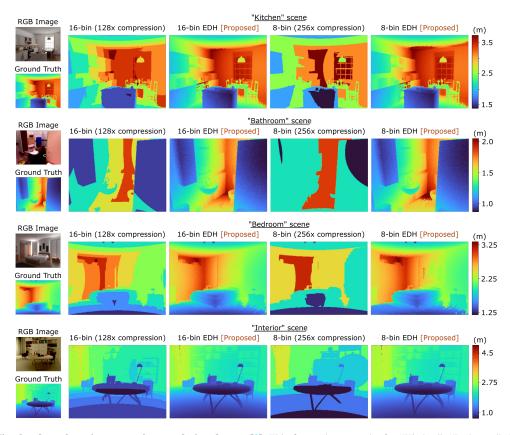

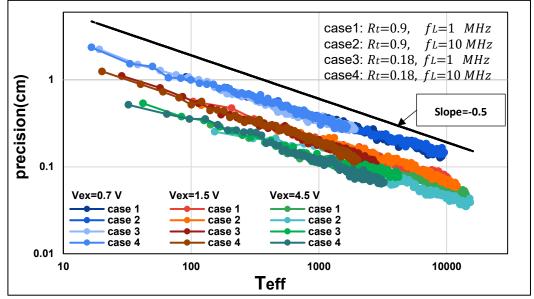

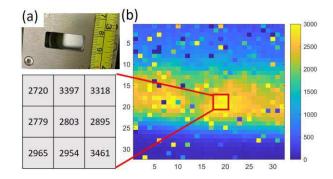

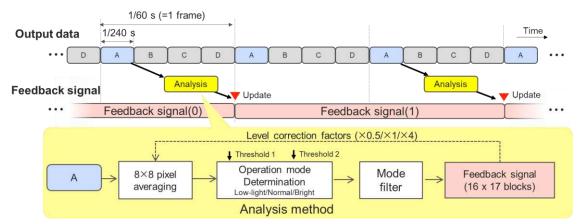

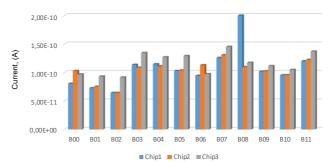

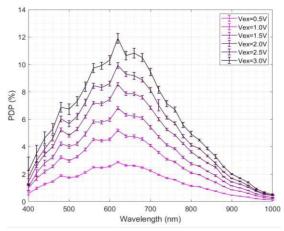

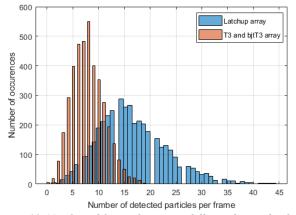

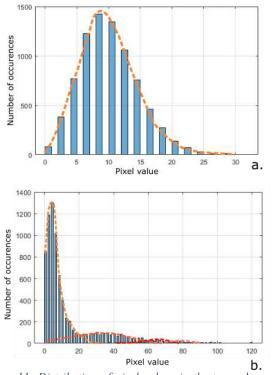

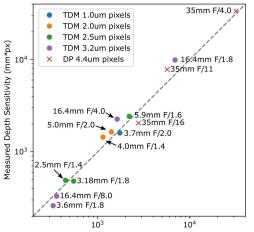

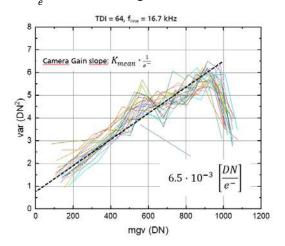

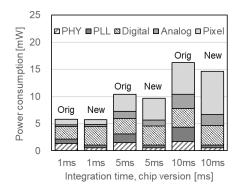

Next, a ToF imaging experiment was conducted to verify the effectiveness of oversampling for a ratio of 10. Note that the time/depth resolutions at 303 MHz, 607 MHz, and 607 MHz with 10× sampling are 3.3 ns/0.5 m, 1.75 ns/ 0.25 m, and 0.175 ns/ 0.025 m respectively. A pulsed semiconductor laser with a wavelength of 660 nm and an FWHM of 2.5 ns was used. Figure 8 shows the configuration of the targets and the depth maps for each condition. 100-image averaging was applied to improve the SNR. Fig. 9 compares the reconstructed optical waveforms and their fitting curves with a quadratic approximation. The mean and standard deviation of the depth is quantitatively compared in Table 1, which demonstrates the effectiveness of the proposed method.

#### IV. CONCLUSION

In this paper, we demonstrated the concept, benefits, and implementation of pseudo-dToF imaging. Several techniques such as increasing clock frequency from 303 MHz to 607 MHz and oversampling have been applied to improve the depth resolution and estimated depth precision. While there are still some issues such as long processing time, vulnerability to ambient light and so on, the proposed method remains a promising technique for applications like autonomous vehicles, and robotics in challenging environments with MPI.

#### ACKNOWLEDGMENTS

This work was supported by JST, CREST, JPMJCR22C1, and in part by Grants-in-Aid for Scientific Research (S), numbers 17H06102 and 18H05240. This work was also supported by VLSI Design and Education Center (VDEC), The University of Tokyo, with the collaboration with Cadence Corporation, Synopsys Corporation, and Mentor Graphics Corporation.

#### REFERENCES

- A. R. Ximenes, et al., "A 256 × 256 45/65nm 3D-Stacked SPAD-Based Direct TOF Image Sensor for LiDAR Applications with Optical Polar Modulation for up to 18.6 dB Interference Suppression", ISSCC 2018, pp. 96–98.

- [2] Z. Zhao, et al., "A Novel Imaging Method for Two-Tap Pulsed-Based Indirect Timeof-Flight Sensor," IEEE Sensors Journal, Vol. 23, No. 7, pp. 7017-7030, 2023.

- [3] S. Kawahito, et al., "CMOS Lock-In Pixel Image Sensors with Lateral Electric Field Control for Time Resolved Imaging," Proc. 2013 IISW, Vol. 361, 10-6.

- [4] K. Kagawa, et al., "A dual mode 303 Megaframes per second charge domain time compressive computational CMOS image sensor," Sensors 2022, Vol. 22.5, 1953.

- R. Baranuk, "Compressive sensing [lecture notes]," IEEE Signal Processing Magasize, Vol. 24, No. 4, pp. 118-121, 2007.

- [6] C. Li, et al., "An efficient augmented Lagrangian method with applications to total variation minimization," Computational Optimization and Applications, Vol. 56, 2013.

b) Reconstructed light waveform at relative distances of 0.65 m and 0.40 m (Average of ROI 5×5 pixel values)

Fig. 7. MPI interference separation at 303 MHz and 607 MHz

Fig. 9. Side view of depth maps and an example of peaks of reconstruction signal

|       | Real  | 303 MHz<br>Normal<br>sampling |             | 607 MHz<br>Normal<br>sampling |             | 607 MHz<br>10 ×<br>sampling |             |

|-------|-------|-------------------------------|-------------|-------------------------------|-------------|-----------------------------|-------------|

|       | depth | Mean<br>[m]                   | Std<br>[cm] | Mean<br>[m]                   | Std<br>[cm] | Mean<br>[m]                 | Std<br>[cm] |

| Cork  | 1.00  | 1.04                          | 2.53        | 1.01                          | 1.17        | 1.00                        | 0.94        |

| Fan   | 2.00  | 1.66                          | 5.59        | 1.98                          | 1.14        | 1.99                        | 0.72        |

| Panel | 3.00  | 3.03                          | 3.67        | 3.08                          | 5.60        | 3.00                        | 0.57        |

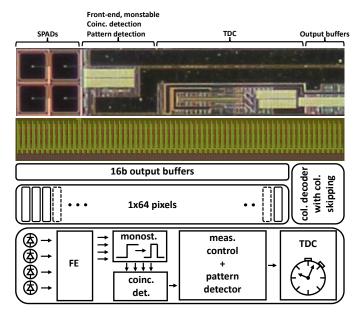

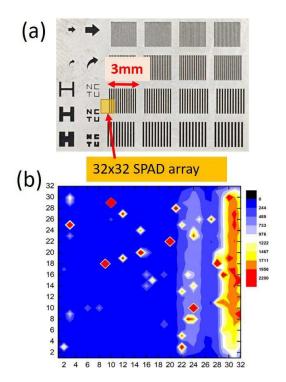

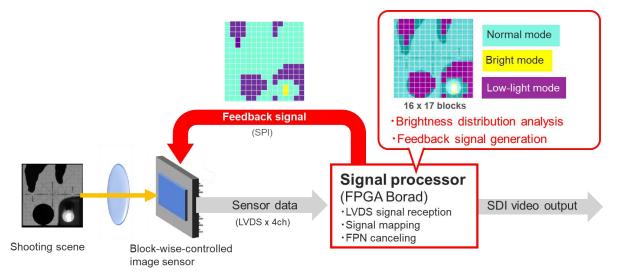

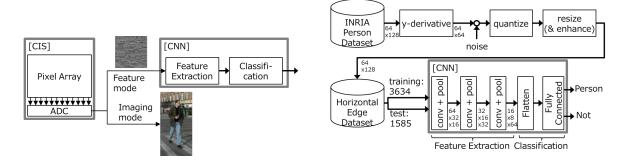

### Histogram-less direct time-of-flight imaging based on a machine learning processor on FPGA

Tommaso Milanese\*, Jiuxuan Zhao\*, Brent Hearn<sup>†</sup>, Edoardo Charbon\*

\*AQUA laboratory, École Polytechnique Fédérale de Lausanne, Neuchâtel

{tommaso.milanese, jiuxuan.zhao, edoardo.charbon}@epfl.ch

<sup>†</sup>Imaging division, STMicroelectronics, Edinburgh, U.K.

{brent.hearn}@st.com

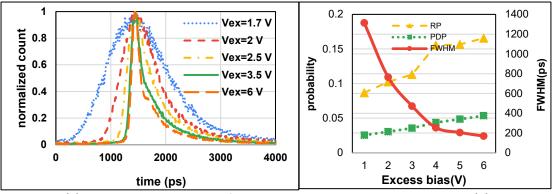

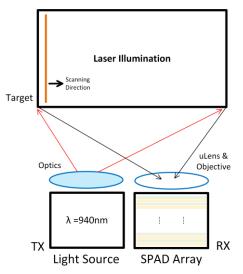

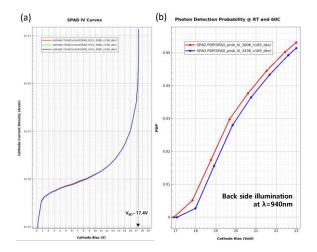

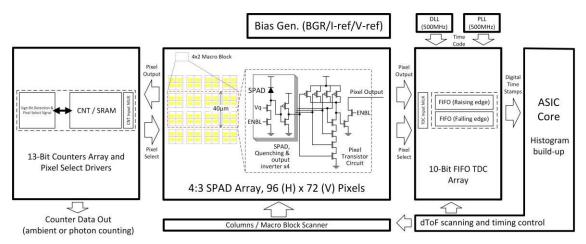

*Abstract*—The investigation of a novel architecture for direct time-of-flight (TOF) SPAD based imaging systems is presented. In the proposed architecture, a pulsed laser source illuminates a scene and the reflected light is captured by a SPAD, which detects photons and converts them to a digital pulse. Like in timecorrelated single-photon counting (TCSPC), for each detected photon a timestamp is generated, however, unlike TCSPC, it is fed to an machine-learning processor (MLP) that was trained to recognize SPAD responses in direct TOF. The MLP generates the distance to the target directly, taking into account potential nonidealities in timestamp generation and processing. Finally, the proposed architecture was demonstrated in practical scenes and its performance reported using standard LiDAR characterization methods.

#### I. INTRODUCTION

SPADs are the sensor of choice in many direct TOF and LiDAR systems, thanks to their compactness and picosecond timing resolution, which enables millimetric precision. In TC-SPC, timestamps are generated whenever a photon is detected and organized in a histogram. A histogram approaches the true response of the SPAD upon for a very large - ideally infinite - number of detected photons. In practice, an estimate of the TOF is extracted from the histogram after a finite time and thus its precision is also limited. In addition, due to dark noise and background illumination, a typical histogram contains large data, much of it not useful for computing TOF. Hence, the memory allocation for a histogram is generally overestimated and thus inefficient [1], [2]. Indeed, the memory scales exponentially with respect to full scale range (FSR) and hardware timing precision and linearly with the number of depth-dots, leading to a large, possibly on-chip memory [3], [4]. To address this issue, partial histograms have been devised [5]. This approach however, in its simplest embodiment, may prevent the detection of multiple targets at separate depths. To address this shortcoming, more complex partial histograms are needed, along with complex tracking algorithms. An alternative to direct TOF, is the use of indirect TOF and frequency modulated continuous wave (FMCW) techniques, however, these techniques perform averaging at various levels of sophistication, which in effect prevents multiple depth detection as well. In this paper, we propose to use machine learning to process all photon timestamps directly, as soon as they are generated by a time-to-digital converter (TDC) driven by the SPAD image sensor. The objective is the elimination

of the histograms needed in a direct TOF configuration, as shown in Fig.1. This approach provides the same advantages

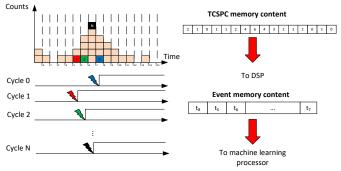

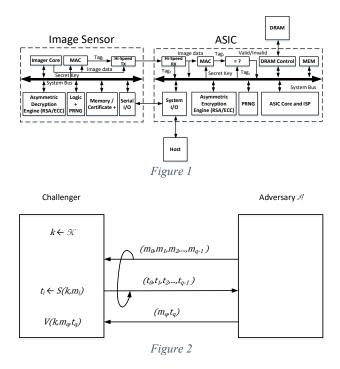

Figure 1. Standard TCSPC and proposed event-processing.

of direct TOF with full histograms, but with much lower requirements in terms of memory and processing power. At the same time, non-idealities associated with the generation and processing of timestamps are intrinsically accounted for. Moreover, the machine-learning processor (MLP) can also be reconfigured to other tasks at a higher level, such as shape and object recognition. The novel machine learning processor was optimized for the long short-term memory (LSTM) execution. We show how to implement the LSTM efficiently in a commercial FPGA, so as to integrate it in the SPAD image sensor in the near future. In the current prototype, photon-detection is performed by a CMOS SPAD, whose raw signals are routed to the FPGA implementing an array of on-demand TDCs, which are then passed on to the LSTM accelerator, as shown in the remainder of the paper.

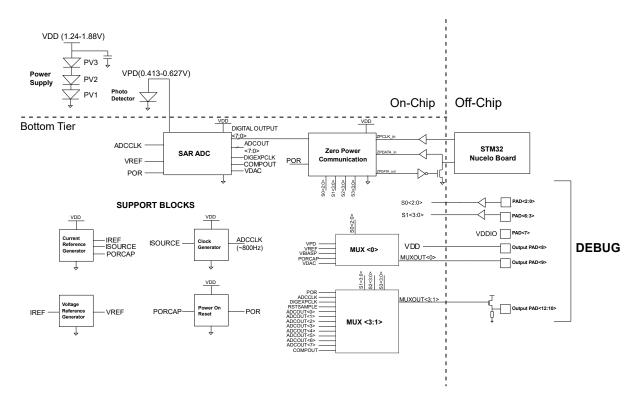

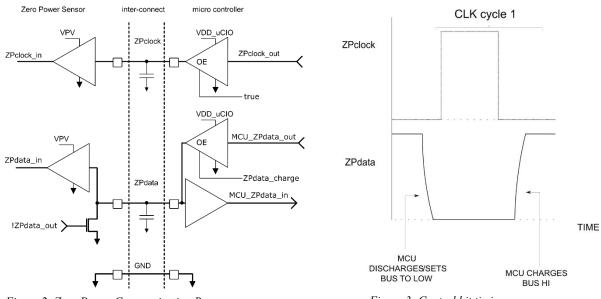

#### **II. SYSTEM ARCHITECTURE**

The general architecture is depicted in Fig.2. The SPAD signal is timestamped by the TDC and the timing data is saved into a  $512 \times 32b$  event memory. The host controls the system by means of a state machine, sending a start signal through the Opal Kelly C++ interface and waiting the end of the acquisition and data processing. The LSTM accelerator starts the processing when the event memory is filled, otherwise it stays in sleep mode, reducing the processing power consumption. When the depth retrieval ends the system sends a signal to the host and is ready to get a new depth-dot.

Figure 2. System architecture.

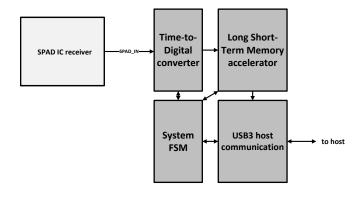

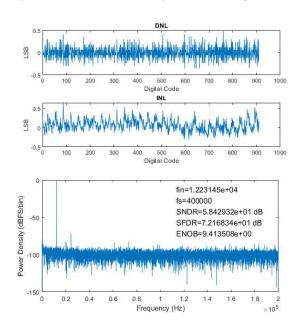

#### A. Time-to-Digital converter

The TDC is based on a tapped delay-line (TDL) latched at 400 MHz. A chain of Carry4 modules is instantiated in adjacent slices, following the place&route (PnR) tool provided by Xilinx for the ripple carry additions. The thermometer output of the TDL is sampled twice, first by a flip-flop (FF) in the same logic slice as the Carry4 and then by another FF placed by the PnR tool, so as to decrease the probability of metastability in the thermometer code.

Figure 3. TDC block diagram. Two synchronized clock domains are used operating at 100 and 400  $\rm MHz.$

A pipelined thermometer-to-binary encoder (T2B) converts the thermometer to binary code at 400 MHz and passes the data to a clock domain crossing synchronizer, reducing the data rate from the TDL sampling clock to the 100 MHz system clock. At the end of the signal flow the data is written in the event memory at system clock speed.

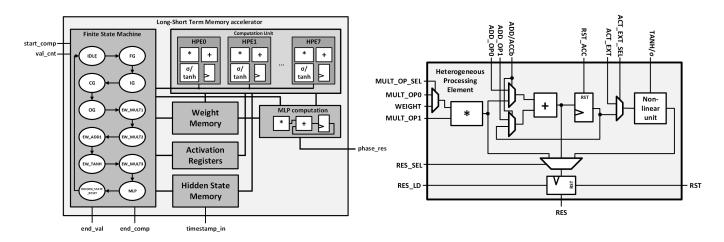

#### B. LSTM accelerator

The LSTM is a recurrent neural network (RNN), a particular type of artificial neural network (ANN) [6]. Since its conception, this processing layer has been used extensively for the processing of time series data, for instance ECG signal classification [7] and speech recognition [8]. The time series in consideration for SPAD-based D-TOF is the raw timestamp data stream, the same data that is commonly organized in a histogram for peak finding. The governing equations for this network are stated as:

$$f_t = \sigma(\mathbf{W}_{\mathbf{xf}}x_t + \mathbf{W}_{\mathbf{hf}}h_{t-1} + b_f) \tag{1}$$

$$i_t = \sigma(\mathbf{W}_{\mathbf{x}i}x_t + \mathbf{W}_{\mathbf{h}i}h_{t-1} + b_i) \tag{2}$$

$$\tilde{c}_t = \tanh(\mathbf{W}_{\mathbf{x}\mathbf{c}}x_t + \mathbf{W}_{\mathbf{h}\mathbf{c}}h_{t-1} + b_c) \tag{3}$$

$$p_t = \sigma(\mathbf{W}_{\mathbf{xo}}x_t + \mathbf{W}_{\mathbf{ho}}h_{t-1} + b_o) \tag{4}$$

$$c_t = f_t \odot c_{t-1} + i_t \odot \tilde{c}_t \tag{5}$$

$$h_t = o_t \odot \tanh(c_t) \tag{6}$$

The bold quantities are matrices and the others are vectors.  $\odot$ represents the element-wise multiplication between 2 vectors,  $\sigma(\cdot)$  represents the element-wise sigmoid activation for all the vector elements and  $tanh(\cdot)$  is the element-wise hyperbolic tangent activation. After the LSTM layer a final fully connected layer (FCN) is used to transform the final hidden state vector into a regression value, that for this application is a number ranging from 0 to 1 representing the phase of the backscattered light pulse with respect to the laser emitter. This number is then multiplied by the FSR to extract the distance in post-processing. Eqs.1-6 embed matrix-vector multiplications, element-wise additions and multiplications and element-wise non-linear activations, all completely parallelizable operations. The design of this accelerator is based on a row-stationary data flow for the matrix-vector multiplication: each processing elements (PEs) compute one row of the multiplication, acting all in parallel. For the LSTM algorithm execution the resources needed are multipliers, adders, and non-linear activation LUTs, which form the basis of the PE design, Fig.4; muxes are added before the three operators to be able to perform elementwise vector operations. Referring to Eqs.1-6  $f_t$ ,  $i_t$ ,  $\tilde{c}_t$ ,  $o_t$ and  $c_t$  are stored in the activation registers,  $h_t$  in the hidden state memory, all W and b in the weight memory and  $x_t$ in the separate event-memory (not shown in the figure). By reprogramming the PEs scalar and vector calculations can be performed in parallel, lowering the processing time per timestamp. The memories in the design have been laid out in such a way that each PE has its own memory space, both in the weight memory and in the activation registers needed for the LSTM execution. A program counter dictates the state machine execution and, exploiting a masking operation, it controls the address of the weight memory. The weight memory for this design is a  $42 \times 128$  bit block RAM Xilinx IP, but in the future it will be substituted by a single port SRAM for solid state implementations. The activation registers are implemented with logic, and they are subdivided in two subbanks per PE in order to decrease the algorithm execution time. The total memory allocated for these registers is  $80 \times 28$ bits, sub-divided in  $10 \times 28$  bits for each of the eight PEs.

#### **III. SYSTEM TRAINING AND QUANTIZATION**

The LSTM based network has been trained off-line after the creation of a dataset from a MATLAB simulator [9]. The

Figure 4. (Left) LSTM accelerator block diagram. (Right) Processing element RTL schematic.

LiDAR signal return is modeled as a Gaussian distribution :

$$P(t;d) = R(d) \exp\left\{\frac{(t - \frac{2d}{c})^2}{\sigma}\right\},\tag{7}$$

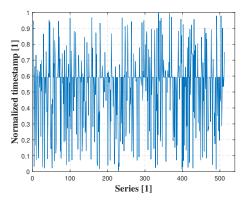

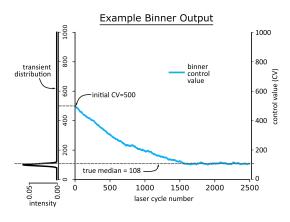

where R(d) represents a constant embedding the physical scene/SPAD parameters, d is the target distance,  $\sigma$  is the parameter related to system jitter and c is the speed of light. A background light of 1klux was chosen and a reference white target with 97% reflectivity has been used. The background is assumed to be a uniformly distributed noise source over the laser period with Poisson statistics, where the  $\lambda$  parameter corresponds to the background lux intensity. A gamut of distances ranging from 0 to 15 m with a step of 60  $\mu$ m was selected and histograms of these distances were constructed and sampled, to obtain 10k time-series per each distance point, containing 512 timestamp values. Fig.5 shows an example of the training data, for the corresponding distance of 8.89 m. The network was implemented in PyTorch and then trained in Google Colab using mean squared error (MSE) loss function:

$$MSE(y_{p,i}, y_t) = \frac{1}{N_s} \sum_{i=1}^{N_s} (y_{p,i} - y_t)^2,$$

(8)

with  $N_s$  being the number of timestamps processed by the network (512 in our case),  $y_{p,i}$  the predicted value of the network for every time step and  $y_t$  the target ground truth. Note that the ground truth does not change through time, since the whole time series belongs to a single distance distribution, which we want to predict. Adam optimizer with a 0.001 learning rate was used, setting a total of 50 epochs to allow training convergence and input time series have been divided in batches of 64. After training, the network weights were quantized in fixed point arithmetic using simple truncation, in a Q6.10 format. After quantization the weights have been loaded into the weight memory as a memory initialization file for practical reasons, even if a simple DMA has been implemented to allow weight memory reconfigurability on-

the-fly for solid state implementations.

Figure 5. Example of a simulated time series used for the network training. Time values have been scaled with respect to the maximum range. In this example the distance label is 8.89 m (scaled to 0.593).

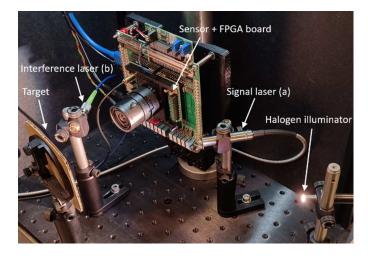

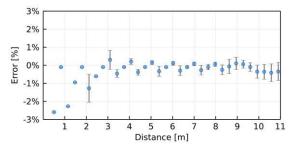

#### **IV. RANGING RESULTS**

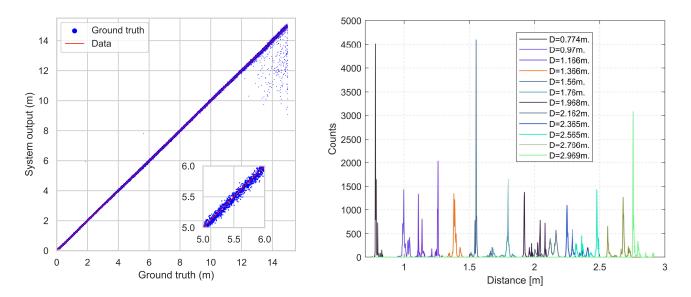

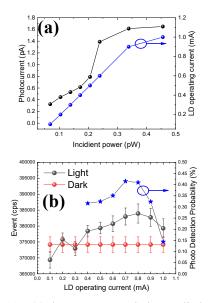

The system-level ranging performance of a single point SPAD sensor has been characterized. The scratchpad buffer processed by the accelerator was loaded with simulated data coming from different probability distributions for different distances, ranging from 0.05 m to 15 m with a step of 60  $\mu$ m. To simulate a real-life scenario, a scanning confocal setup was built similar to [10] and a statistics of 10,000 points have been acquired for 12 different distances. The field-of-view (FoV) was covered by a generic target consisting of a white paper. The ground truth was acquired with a commercial rangefinder placed below the scanning mirrors, while parallax and offset errors were removed in post-processing. Results for the ranging measurements are shown in Fig.6.

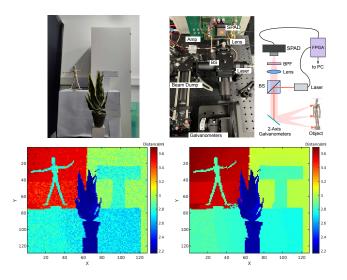

#### V. 3D IMAGING RESULTS

Using the same optical setup, a 3D image was acquired. The timestamps generated by the TDCs were fed to the MLP and a standard histogram-based center-of-mass (CoM) algorithm. Since the system is event-based, no integration time is set,

Figure 6. (Left) Simulated data. Input time series step size is  $60\mu$ m. (Right) Ranging measurements. For each distance 10,0000 points are acquired and organized in a histogram, to characterize the ranging distribution of the implemented LiDAR architecture.

meaning that the acquisition proceeds when the single point has been acquired and processed. To achieve a fair comparison, for each point, we used the same scratchpad buffer where timestamps had been stored for both MLP and CoM. As expected, CoM showed less variability, while the proposed architecture can clearly distinguish the different objects in the scene. The results are shown in Fig.7.

Figure 7. 3D imaging results. Top left: RGB intensity image of the target. Top right: Optical setup. Bottom left: LSTM accelerator. Bottom right: CoM.

#### VI. CONCLUSIONS

We presented a new histogram-less Direct Time-of-Flight architecture based on timing event processing through a machine learning processor. The processor enables individual photon timestamp processing and it is optimized for LSTM algorithm execution, with the possibility of repurposing it for other high-speed event-based applications requiring machine learning.

#### REFERENCES

- A. R. Ximenes, P. Padmanabhan, M.-J. Lee, Y. Yamashita, D.-N. Yaung, and E. Charbon, "A 256× 256 45/65nm 3d-stacked spad-based direct tof image sensor for lidar applications with optical polar modulation for up to 18.6 db interference suppression," in 2018 IEEE International Solid-State Circuits Conference-(ISSCC). IEEE, 2018, pp. 96–98.

- [2] P. Padmanabhan, C. Zhang, M. Cazzaniga, B. Efe, A. R. Ximenes, M.-J. Lee, and E. Charbon, "7.4 a 256× 128 3d-stacked (45nm) spad flash lidar with 7-level coincidence detection and progressive gating for 100m range and 10klux background light," in 2021 IEEE International Solid-State Circuits Conference (ISSCC), vol. 64. IEEE, 2021, pp. 111–113.

- [3] I. Gyongy, N. A. Dutton, and R. K. Henderson, "Direct time-of-flight single-photon imaging," *IEEE Transactions on Electron Devices*, vol. 69, no. 6, pp. 2794–2805, 2021.

- [4] G. Chen, C. Wiede, and R. Kokozinski, "Data processing approaches on spad-based d-tof lidar systems: A review," *IEEE Sensors Journal*, vol. 21, no. 5, pp. 5656–5667, 2020.

- [5] C. Zhang, S. Lindner, I. M. Antolović, J. M. Pavia, M. Wolf, and E. Charbon, "A 30-frames/s, 252 × 144 spad flash lidar with 1728 dual-clock 48.8-ps tdcs, and pixel-wise integrated histogramming," *IEEE Journal of Solid-State Circuits*, vol. 54, no. 4, pp. 1137–1151, 2018.

- [6] S. Hochreiter and J. Schmidhuber, "Long short-term memory," Neural computation, vol. 9, no. 8, pp. 1735–1780, 1997.

- [7] S. A. Mirsalari, N. Nazari, S. A. Ansarmohammadi, S. Sinaei, M. E. Salehi, and M. Daneshtalab, "Elc-ecg: Efficient lstm cell for ecg classification based on quantized architecture," in 2021 IEEE International Symposium on Circuits and Systems (ISCAS). IEEE, 2021, pp. 1–5.

- [8] D. Kadetotad, S. Yin, V. Berisha, C. Chakrabarti, and J.-s. Seo, "An 8.93 tops/w lstm recurrent neural network accelerator featuring hierarchical coarse-grain sparsity for on-device speech recognition," *IEEE Journal* of Solid-State Circuits, vol. 55, no. 7, pp. 1877–1887, 2020.

- [9] A. Aßmann, B. Stewart, and A. M. Wallace, "Deep learning for lidar waveforms with multiple returns," in 2020 28th European Signal Processing Conference (EUSIPCO). IEEE, 2021, pp. 1571–1575.

- [10] J. Zhao, T. Milanese, F. Gramuglia, P. Keshavarzian, S. S. Tan, M. Tng, L. Lim, V. Dhulla, E. Quek, M.-J. Lee *et al.*, "On analog silicon photomultipliers in standard 55-nm bcd technology for lidar applications," *IEEE Journal of Selected Topics in Quantum Electronics*, vol. 28, no. 5, pp. 1–10, 2022.

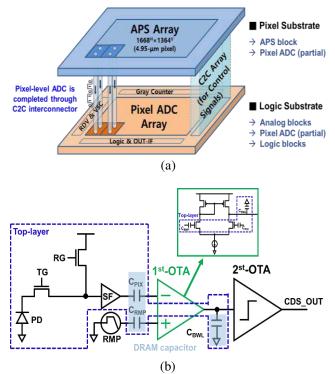

### A 9-shared 3x3 Nonacell Image Sensor with 0.64µm unit pixels for Read Noise and Low-illuminance SNR enhancement

Wonchul Choi, Munhwan Kim, Junoh Kim, Junho Seok, Younguk Song, Dukseo Park, Hyeonseop Yoo, Minyoung Jung, Jieun Lee, Juha Kim, Heegeun Jeong, Kyungho Lee, Eunsang Cho, Howoo Park, Bumsuk Kim, Kyungmin Koh, Sangil Jung, Jungchak Ahn, and Joonseo Yim

Samsung Electronics Co., Ltd., Yongin-city, Gyeonggi-do, Korea, E-mail: wc83.choi@samsung.com

#### Abstract

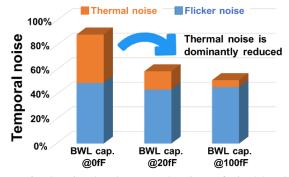

A 0.64µm pitch 108 mega pixels CMOS image sensor has been demonstrated and the advanced nonacell structure is used to maximize low-light performance. In this work, a new 9 charge-sum (9S) method is employed, and operation method and parameters for determining signal to noise ratio (SNR) are compared with the conventional 3 charge-sum 3 voltageaverage (3S3A). The image characteristics have been examined as the binning method, the enhancement of the device performance due to the generated signal and conversion gain effect have been quantitatively analyzed. Compared to 3S3A, read noise of 9S is reduced by 45%, and improved SNR value is confirmed at low-light operating condition.

Keywords: CMOS image sensor, Nonacell, binning method, charge-sum, read noise, SNR.

#### Introduction

In recent years, CMOS image sensors (CIS) have attracted great attentions as a mobile application since it is considered as one of the important feature in selecting mobile devices. For this reason, CIS performance improvement is continuously required, and various efforts are underway to improve quality [1]. The demand for high resolution is increasing for instance, however, the pixel size should be shrank due to the limitation of optical format of the lens module [2]. The sub-micron pixel was mass-produced for the first in 2018 [3], and recently, 0.64µm pixel is the smallest one under mass production [4]. However, as the pixel size shrinks down, characteristics such as full well capacity (FWC), sensitivity, and signal-to-noise ratio (SNR) are inevitably degraded. As a way to solve this problem, a pixel summation method such as 2x2, 3x3, and etc. has been proposed and is widely used.

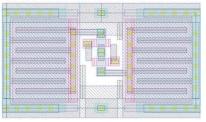

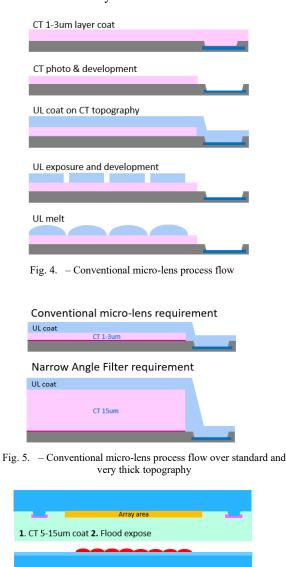

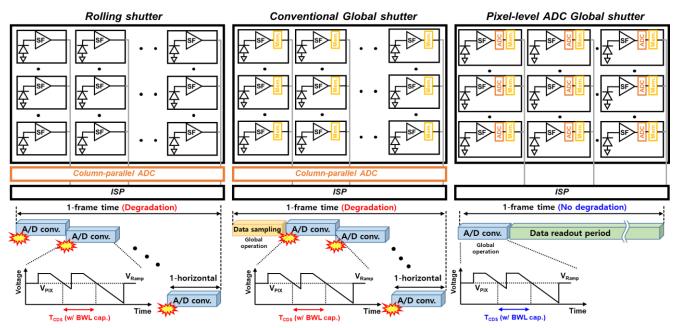

3x3 nona binning is firstly introduced with  $0.8\mu$ m pixel [5], and it can switch full and binning resolution of 108Mp and 12Mp, respectively. By merging 9 photo-diodes (PDs), especially in low illuminance condition, it improves sensitivity. However, the previous 3x3 nonacell suffered from relatively poor image quality in low illumination condition due to high read noise. In this work, the noise characteristics according to the 3x3 binning method are analyzed in the nonacell structure, and the low-light SNR improvement with new 9 charge sum method is proposed and demonstrated in  $0.64\mu$ m pixel.

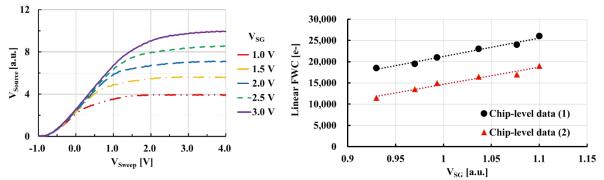

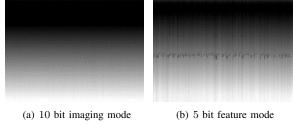

#### **Pixel architecture**

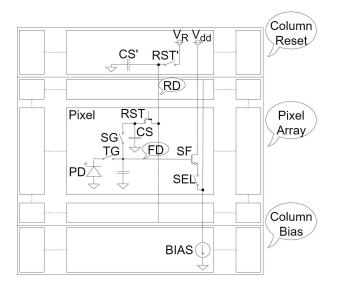

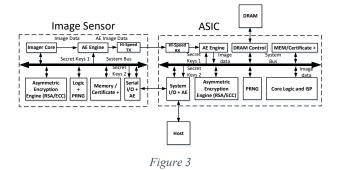

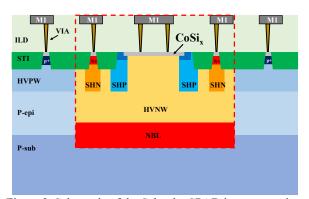

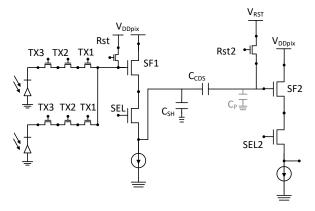

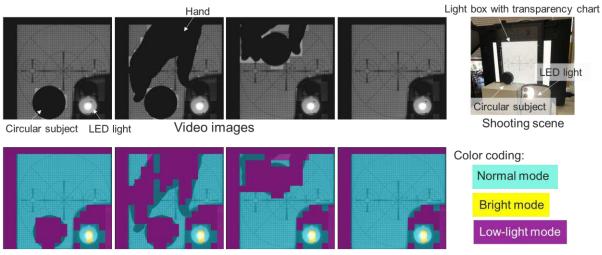

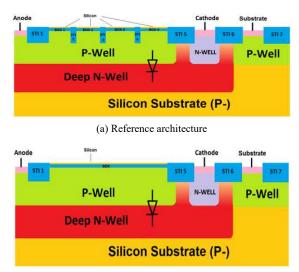

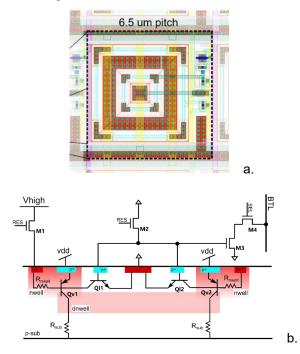

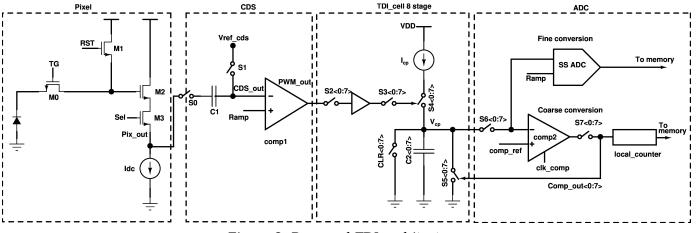

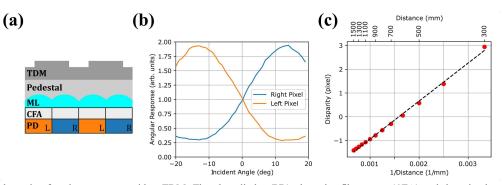

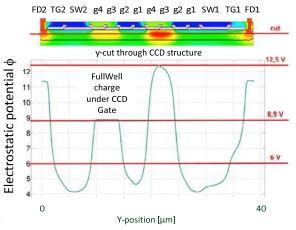

In the previous work [5], three 1x3 shared pixel units are merged to generate a 3x3 pixel with the same color. In nonabinning mode, we used 3 charge-sum 3 voltage-average mode (denoted by 3S3A), which indicates that signal electrons in shared 3 PDs are added in the floating diffusion (FD), and the three vertical outputs are averaged at the voltage domain. In this work, on the other hand, 9 charge-sum (denoted by 9S) for

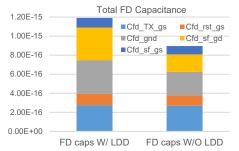

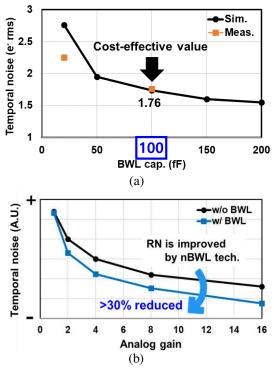

Fig. 1 Nonacell structures with (a) 1x3, (b) 3x3 shared pixels are compared, and the pixel schematic is shown in (c), (d) respectively.

nona-binning is adopted, and the main difference of the 9S between 3S3A is the number of 9 PDs commonly shared to the FD node. The physical structures are compared in Fig. 1(a) and (b).

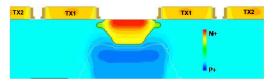

Since 9 pixels share the same FD, the FWC in binning mode that affects the SNR of high-illumination condition is determined by the FD dynamic range, not the PD's FWC. Therefore, it is important to increase FD capacitance so that it can take as many electrons as possible. In order to make FD capacitance larger, a technique of simultaneously using the capacitance of the adjacent FD node is controlled by reset (RG) and dual conversion gain (DCG) transistors.

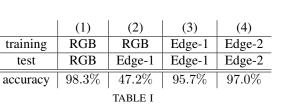

| TABLE I         3-sum 3-average vs 9-sum mode |        |                                             |                                             |                                               |

|-----------------------------------------------|--------|---------------------------------------------|---------------------------------------------|-----------------------------------------------|

|                                               | Unit   | Full                                        | 3S3A                                        | 9S                                            |

|                                               | lsb/e- | - C.G                                       | ¼₃·C.G                                      | C.G                                           |

| Signal                                        | lsb    | S                                           | 35                                          | 9S                                            |

| Shot noise                                    | lsb    | $\sqrt{S}$                                  | $\sqrt{3S}/\sqrt{3}$                        | $\sqrt{9S}$                                   |

| SF noise                                      | lsb    | N <sub>SF</sub>                             | $N_{SF}/\sqrt{3}$                           | $N_{SF}$                                      |

| ADC noise                                     | lsb    | N <sub>ADC</sub>                            | N <sub>ADC</sub>                            | N <sub>ADC</sub>                              |

| S/N ratio                                     | -      | $\frac{S}{\sqrt{S + N_{SF}^2 + N_{ADC}^2}}$ | $\frac{9S}{\sqrt{9S+3N_{SF}^2+9N_{ADC}^2}}$ | $\frac{9S}{\sqrt{9S + N_{SF}^2 + N_{ADC}^2}}$ |

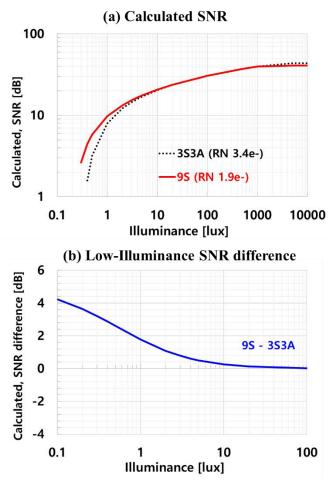

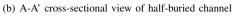

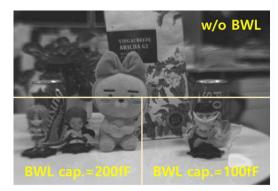

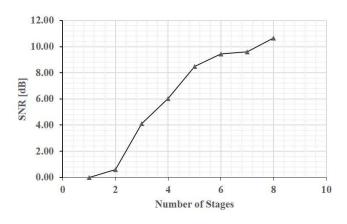

Fig. 2 Calculated SNR difference between 9S and conventional 3S3A as a function of illuminance and the same pixel size is assumed.

In the mode where FD capacitance is largely used, the FD node is connected to adjacent 9-shared FD node and total 18pixels are connected with a single node. Using this method, FD capacitance is increased more than 4 times compared with 9shared FD capacitance, and the circuit schematic is shown in Fig. 1(c) and (d).

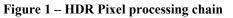

The characteristics of the 9S and conventional 3S3A mode are simply compared in Table I. The conversion gain decreases to 1/3 due to a result of the average, even though the physical FD capacitance is the same. As a consequence, the input referred noise (unit of electron, to be specific) of 3S3A is 3 times larger than that of 9S. In order to compare the SNR between 9S and 3S3A, the signal and noise are analyzed by dividing them in the unit of lsb. Photon shot noise of 9S is relatively large due to its signal, and the dark noise of 3S3A is less than 9S mode since 3S3A averages noise. The signal level takes over the total noise in low-illumination condition (N>>S), and as a consequence, SNR of 9S is superior to that of 3S3A. Fig. 2 shows the differences of SNR between 9S and conventional 3S3A as a function of illuminance. Notice that, for illuminance <10 lux, SNR of 9S is higher than that of 3S3A as we discussed.

#### **Result and discussion**

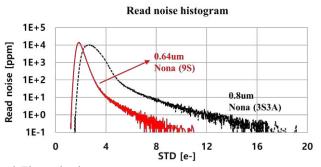

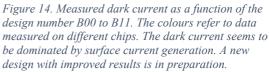

Fig. 3 The read noise histogram, and  $0.64 \mu m$  for 9S and  $0.8 \mu m$  for 3S3A are compared.

The 9-shared pixel structure has advantages in the placement of transistors, such as source follower (SF), RG, DCG, SEL transistors, in the pixel. As the number of shared pixels increased, there is an additional space for transistors, which is used to apply multi-finger SF. By using multi-finger SF, the channel area of SF is increased, and the width increases as much as it is used in parallel to maximize trans-conductance. As consequence, random telegraph noise of 0.64µm pixel is similar to that of 0.8µm one, even though pixel pitch is reduced down to 0.64µm. Furthermore, it is confirmed that the read noise is reduced from 3.4 to 1.9e-, and the histogram is shown in Fig. 3. Note that read noise in electron unit is increased due to the effect of reducing conversion gain affected by averaging, and it can be represented by  $N/\sqrt{3}$  and  $\sqrt{3}N$  for lsb and electron units, respectively, where N denotes full mode noise.

The measured characteristics of 9S mode are compared with those of conventional 3S3A as shown in Table II, and we can clearly notice that 9S mode is superior to conventional 3S3A one. SNR characteristic, especially in low illuminance (1lux), is improved due to the read noise. FWC, dark current, and white spot which are key factors in CIS performance remained at the same level as previously published studies [4].

| TABLE II<br>Comparison of pixel characteristics. |              |        |       |        |  |

|--------------------------------------------------|--------------|--------|-------|--------|--|

|                                                  | Unit -       | Tetra  | No    | na     |  |

|                                                  | Unit         | 0.64µm | 0.8µm | 0.64µm |  |

| Linear<br>FWC                                    | e-           | 6,000  | 6,000 | 6,000  |  |

| Dark current                                     | e-/s         | 1.1    | 1.5   | 1.1    |  |

| Read Noise                                       | e-           | 1.4    | 3.4   | 1.9    |  |

| RTS                                              | ppm          | 4      | 2     | 0      |  |

| White spot                                       | ppm          | 15     | 10    | 10     |  |

| 1lux SNR                                         | $dB/\mu m^2$ | 4.3    | 3.3   | 4.1    |  |

White spot : # of pixels  $\geq 160$  lsb @1-frame, gain x 16, 200 msec, Tj=60°C RTS : # of pixels  $\geq 30$  lsb @difference between 2-frame, gain x 8, 0 msec, Tj=60°C Read noise : 20-frame, gain x 16, 33 msec, Ta=25°C

#### Conclusion

In conclusion, we have demonstrated the read noise and SNR characteristics of 9S CMOS image sensor with  $0.64 \mu m$

unit pixels. A new binning scheme has been introduced to improve SNR at low illuminance, and the 9S and conventional 3S3A are compared in terms of conversion gain, noise, and SNR. The proposed 9 charge sum binning method can dramatically improve read noise, and a 3x3 nonacell structure that can provide image quality equivalent to big pixels at low illumination condition and high resolution at high illumination condition has been completed.

#### References

[1] I. S. Joe, 2021 Symposium on VLSI Technology, 2021, pp. 1-2 [2]

S. Choi, 2017 Symposium on VLSI Technology, 2017, pp. T104-T105

[3] Y. Kim, 2018 IEEE International Solid - State Circuits Conference - (ISSCC), 2018, pp. 84-86 [4] J. E. Park. 2021 IEEE International Solid- State Circuits Conference (ISSCC), 2021, pp. 122-124 [5] Y. Oh, 2020 IEEE International Electron Devices Meeting (IEDM), 2020, pp. 16.2.1-16.2.4

### Light-Emission Crosstalk Model and Dynamic Correction Algorithm for Large-Scale SPAD Image Sensors

A. Abdelghafar, K. Morimoto, H. Sekine, H. Tsuchiya, M. Shinohara, Y. Ota, J. Iwata, Y. Matsuno, K. Sakurai, and T. Ichikawa

> Canon Inc., Kanagawa, Japan, TEL: +81-3-3758-2111 E-mail: abdelghafar.aymantarek@mail.canon

Abstract—We present a new dynamic correction algorithm to suppress the impact of light-emission (LE) crosstalk in single-photon avalanche diode (SPAD) image sensors. The proposed algorithm demonstrated a capability of correcting both LE crosstalk and nonlinearity in a SPAD sensor, minimizing the effect of hot clusters and color shift that could potentially appear over the array. The results demonstrated a significant improvement in dark signal non-uniformity and color reproducibility. The proposed algorithm allows large-scale SPAD sensors to be implemented in various fields of imaging applications such as surveillance, biomedical and automotive.

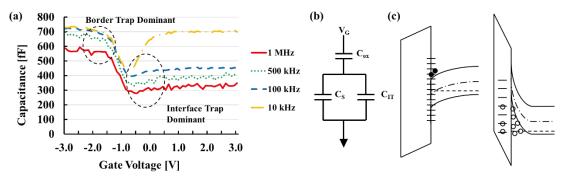

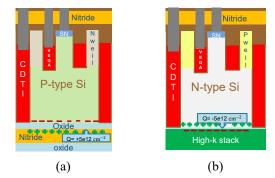

#### I. INTRODUCTION

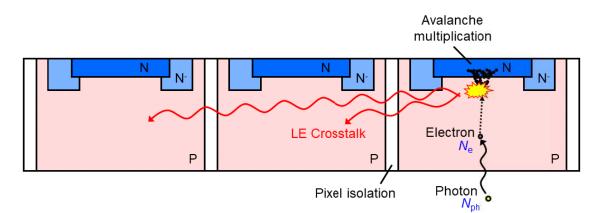

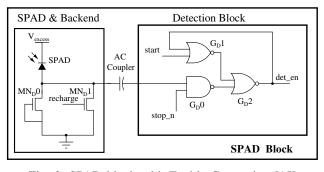

Single-photon avalanche diode (SPAD) image sensor provides a fully-digital 2D imaging solution, and is a promising candidate for a next generation of photon-counting image sensors for low-light and high dynamic range (HDR) imaging applications. A key challenge in high-definition SPAD cameras is the suppression of light-emission (LE) crosstalk that originates from electron-hole recombination around avalanche multiplication region. Pixel miniaturization leads to enhanced LE crosstalk, and it is thereby critical to mitigate the impact on image quality towards further scaling of the array. In recent decades, many studies have been conducted on the basic principle of LE crosstalk in SPAD arrays [1,2,3]. It has been observed that the spectrum of light emission contains a wide range of wavelengths from visible to near infrared. Unlike typical optical crosstalk and charge crosstalk discussed in CMOS image sensors, LE crosstalk observed in SPAD sensors can generate spurious counts not only to adjacent pixels but to distant pixels. Due to this unique property, there are several issues induced specific to SPAD image sensors. Fig. 1 shows a schematic representation of SPAD pixels with possible LE crosstalk contributions to adjacent pixels. LE crosstalk could cause enhanced hot clusters, increased apparent signal counts or dark counts, color shift, and reduced modulation transfer function (MTF), leading to image quality degradation. Nonlinear photoresponse of SPAD pixels gives additional complexity when estimating a magnitude of LE crosstalk over the array.

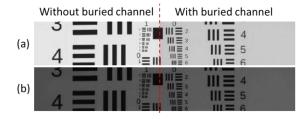

To mitigate the impact of LE crosstalk, several approaches have been proposed, including optimization and improvement of process, device, circuit and operation. An important countermeasure is to reduce the amount of LE crosstalk by introducing buried metal full trench isolation between pixels, to prevent emitted light to propagate from one pixel to another [4]. Another approach is the implementation of hot pixel elimination function into pixel circuits [5]. Alternative approach is to adaptively control a frequency of avalanche event through a modified recharging operation [6]. Yet, it is challenging for any of those approaches to thoroughly eliminate the effect of LE crosstalk. To minimize the image quality degradation, an appropriate correction method must be considered. To this date, a systematic method to correct the effect of LE crosstalk in the post-processing has not been presented.

In this paper, we propose a versatile correction algorithm for large-scale SPAD image sensors that suppresses the impact of LE crosstalk. A prototype megapixel SPAD array is used to examine the feasibility of this proposed algorithm.

#### II. PRINCIPLES & METHODS

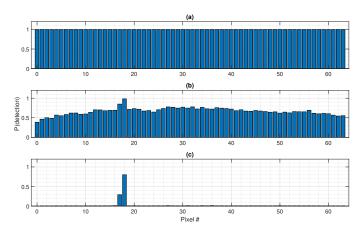

A common approach to quantify the level of LE crosstalk is to introduce a crosstalk matrix; a spatial map of crosstalk probability. To obtain the crosstalk matrix for SPAD array, averaged dark frame is captured to extract addresses of isolated hot pixels. For each hot pixel, relative signal levels of the surrounding pixels are mapped around the extracted hot pixel. Based on each signal distribution created from the extracted hot pixels, a spatial map of crosstalk probability can be derived. Crosstalk count at the surrounding pixels is proportional to the signal count at the core hot pixel. This indicates that LE crosstalk contribution is predictable based on the core hot pixel level and the predefined crosstalk map.

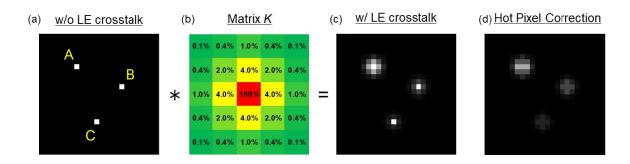

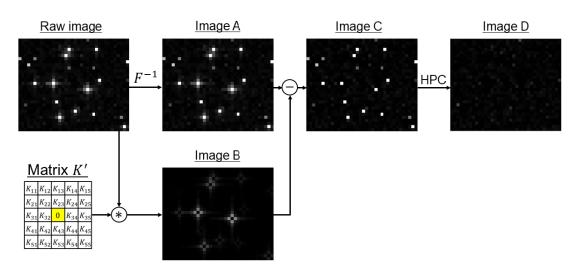

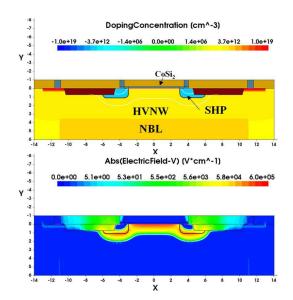

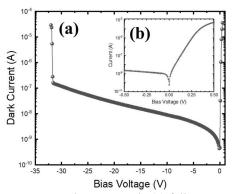

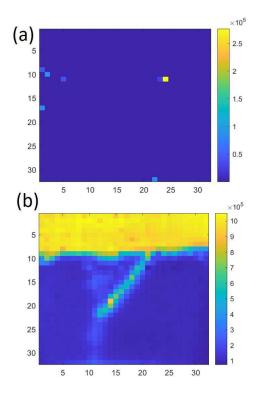

Fig. 2(a) illustrates the isolated hot pixels using a synthetic dark image. Due to high reverse bias operation, SPAD image sensors tend to suffer from higher hot pixel population compared to CMOS image sensors. Fig. 2(b) shows an example of LE crosstalk matrix K, representing the crosstalk percentage from central to adjacent pixels. Fig. 2(c) shows the effect of LE crosstalk which can be represented by a convolution of Fig. 2(a) and (b). Each isolated hot pixel behaves as light emitting source to form a hot cluster. Fig. 2(d) shows the result of conventional hot pixel correction (HPC) based on a selective 1D median filtering. LE crosstalk-induced hot clusters spread over multiple pixels, and hence the conventional approach cannot fully eliminate the defective pixels.

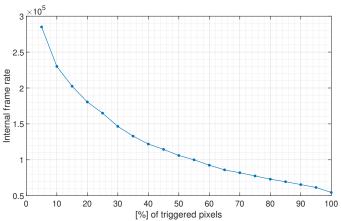

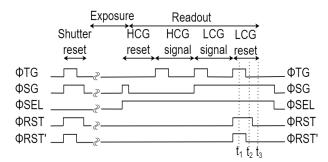

To apply a precise correction to LE crosstalk, active recharging-based operation must be employed instead of passive recharging-based operation, where non-monotonic photoresponse precludes a unique estimation of crosstalk contribution. As one of the examples of active recharging, clocked recharging is conducted by providing a periodic recharging clock fed to a gate of recharge transistors [6]. In contrast to the conventional passive recharging, the clocked recharging-based sensor restricts the maximum photon counts per frame allowing to reduce power consumption, which makes it a viable option for megapixel resolution sensor suited for imaging applications.

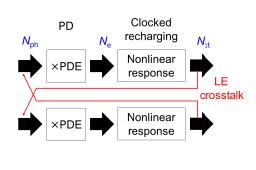

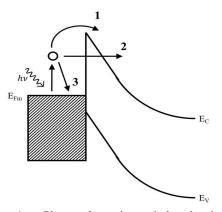

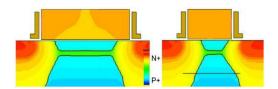

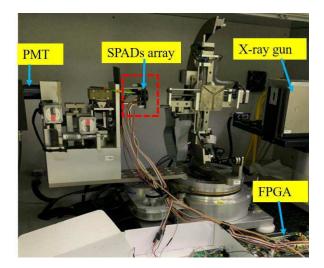

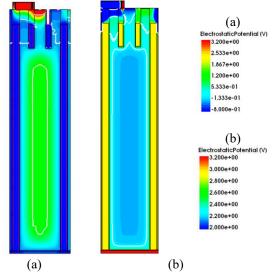

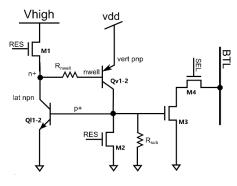

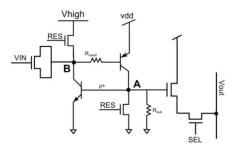

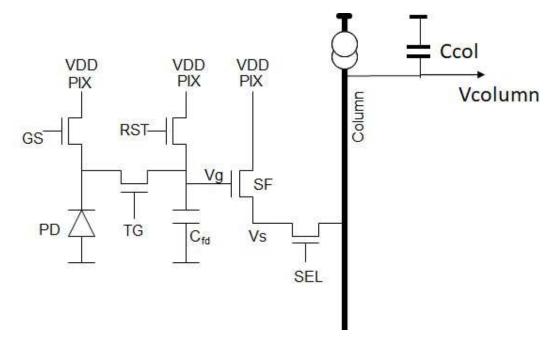

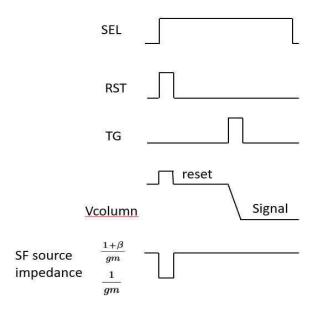

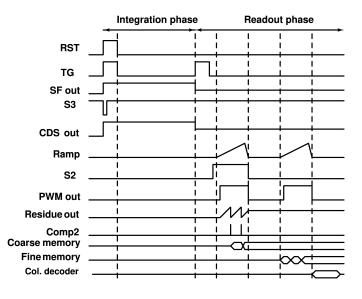

Fig. 3(a) and (b) represents a cross-section, a pixel circuit, and a timing diagram of clocked recharging-based SPAD sensor; a photo-electron triggers avalanche multiplication which induces LE crosstalk to adjacent pixels. Fig. 3(c) depicts a relation between the number of detected avalanche events  $(N_{ct})$  and the number of incident photons  $(N_{ph})$  for active and passive recharging-based operations. In passive recharging,  $(N_{ct})$  decreases at high-light condition. In clocked recharging, one recharging event allows only one avalanche event at maximum, leading to a nonlinear monotonic photoresponse.

Fig. 4 shows a signal conversion flow for the clocked recharging-based SPAD pixels in the presence of LE crosstalk. The number of LE events is equivalent to  $N_{ct}$ , and contribution of the secondary photons is fed back to  $N_{ph}$  in the adjacent pixels. This feedback process could induce higher-order crosstalk events, and complicates analytical formulation of LE crosstalk contribution. However, the correction algorithm for LE crosstalk can be simplified when the aforementioned crosstalk matrix *K* is introduced.

Fig. 5 shows an image processing flow of the proposed LE crosstalk correction algorithm. First, a raw image is converted to "Image A" through nonlinear correction function  $F^{-1}$ . In parallel, the same raw image is convolved with matrix K' to create "Image B", where matrix K' represents a contribution of the LE crosstalk, obtained by replacing the central element of matrix K with 0. "Image B" is subtracted from "Image A" to create "Image C", which shows the result of both nonlinear correction and LE crosstalk correction applied. Finally, "Image C" is converted to "Image D" through conventional HPC. The proposed correction algorithm for LE crosstalk is represented by a following equation:

$$I_t = F^{-1}(I_{raw}) - I_{raw} * K'$$

where  $I_{\text{raw}}$  is the initial raw image, and  $I_{\text{t}}$  is the reconstructed image. Benefit of this algorithm is that it can simultaneously correct nonlinearity and LE crosstalk-induced artifacts, such as hot cluster and color shift, irrelevant to light intensity distribution.

To evaluate the feasibility of the proposed algorithm, a variant of 3.2Mpixel 3D-stacked back-illuminated SPAD sensor is used, which has relatively higher crosstalk probability than those presented in a previous report [7].

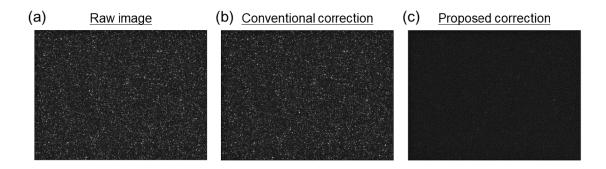

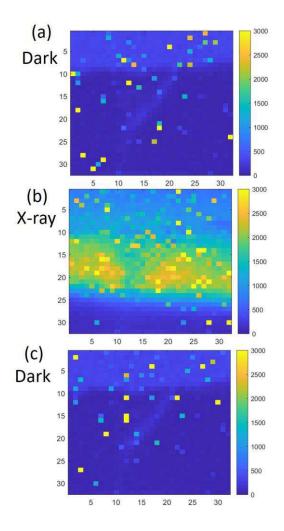

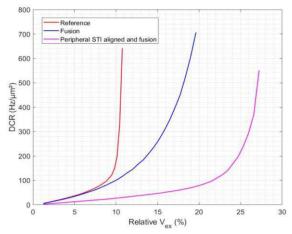

#### **III. RESULTS**

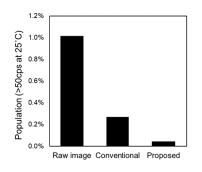

Fig. 6 shows the results of conventional HPC and the proposed correction applied to a 100-frame-averaged dark image captured by the 3.2Mpixel SPAD image sensor. In contrast to the conventional HPC, the proposed algorithm shows a significant improvement in the dark signal non-uniformity. Fig. 7 illustrates the diagram of measured hot pixel population over the array in each image presented in Fig. 6. The hot pixel population (>50cps at  $25\Box$ ) of the proposed algorithm has been reduced by more than 6 times with respect to the conventional HPC method.

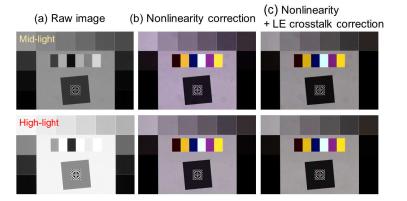

Fig. 8 shows the images obtained using a SPAD sensor with on-chip Bayer color filter in mid-light (top images) and high-light (bottom images) conditions. Fig. 8(a) shows raw images, representing their relative difference in light intensity. Fig. 8(b) and (c) show the result of nonlinearity correction applied, and the result of LE crosstalk correction additionally applied, respectively. Fig. 8(b) shows a color shift towards magenta, where a degree of shift is dependent on the light level. Fig. 8(c), in contrast, shows robust color reproduction for different light levels. This result indicates that the proposed correction algorithm can properly compensate LE crosstalk-induced nonlinear color shift.

#### **IV. CONCLUSION**

In this paper, a dynamic correction algorithm to reduce the effect of LE crosstalk is presented. The algorithm demonstrated a significant suppression of LE crosstalk-induced hot cluster and color shift, in the presence of nonlinear photoresponse. The proposed algorithm allows the implementation of multi-megapixel SPAD image sensors into various fields of imaging and sensing applications, including electronic industry, surveillance, biomedical and automotive.

#### V. REFERENCES

[1] I. Rech *et al.*, "Optical crosstalk in single photon avalanche diode arrays: A new complete model," *Opt. Express*, 16 (12) 8381-8394, 2008.

[2] R. Younger *et al.*, "Crosstalk analysis of integrated Geiger-mode avalanche photodiode focal plane arrays," *Defense + Commercial Sensing*, 2009.

[3] S. Jahromi and J. Kostamovaara, "Timing and probability of crosstalk in a dense CMOS SPAD array in pulsed TOF applications," *Opt. Express*, 26 (16), 20622-20632, 2018.

[4] K. Ito *et al.*, "A Back Illuminated 10µm SPAD Pixel Array Comprising Full Trench Isolation and Cu-Cu Bonding with Over 14% PDE at 940nm," *IEEE Int. Electron Devices Meeting (IEDM)*, 16.6.1-16.6.4, 2020.

[5] Y. Maruyama *et al.*, "A  $1024 \times 8$ , 700-ps Time-Gated SPAD Line Sensor for Planetary Surface Exploration With Laser Raman Spectroscopy and LIBS," *IEEE J. Solid-State Circuits*, 49 (1), 179-189, 2014.

[6] Y. Ota *et al.*, "A 0.37W 143dB-Dynamic-Range 1Mpixel Backside-Illuminated Charge-Focusing SPAD Image Sensor with Pixel-Wise Exposure Control and Adaptive Clocked Recharging," *IEEE Int. Solid- State Circuits Conference* (*ISSCC*), 94-96, 2022.

[7] K. Morimoto *et al.*, "3.2 Megapixel 3D-Stacked Charge Focusing SPAD for Low-Light Imaging and Depth Sensing," *IEEE Int. Electron Devices Meeting (IEDM)*, 20.2.1-20.2.4, 2021.

Fig. 1. Schematic representation of SPAD pixels and LE crosstalk contributions from one pixel to its adjacent pixels.

Fig. 2. Schematic views describing impact of LE crosstalk on image quality. (a) Synthetic image representing isolated hot pixels. (b) Conceptual example of  $5 \times 5$  LE crosstalk matrix showing LE crosstalk percentage from central to adjacent pixels. (c) Synthetic image simulating the effect of LE crosstalk applied on (a). (d) Result of conventional hot pixel correction on (c) based on selective 1D median filtering.

Fig. 3. Conceptual views of clocked recharging-based operation. (a) Cross-section and pixel circuit of SPAD pixel. (b) Timing diagram. (c) Schematic plot of relation between  $N_{\rm ct}$  and  $N_{\rm ph}$  for clocked and passive operations.

Fig. 4. Signal conversion flow for SPAD pixels in the presence of nonlinearity and LE crosstalk.

Fig. 5. Image processing flow of the proposed LE crosstalk correction algorithm.

Fig. 6. Results of LE crosstalk correction. (a) Averaged full-resolution dark image captured by 3.2Mpixel SPAD image sensor. (b) Result of the conventional hot pixel correction. (c) Result of the proposed LE crosstalk correction.

Fig. 7. Diagram of measured hot pixel population for raw image, conventional correction and the proposed correction.

Fig. 8. Results of nonlinearity correction and LE crosstalk correction in color image under mid-light (top images), and high-light (bottom images) conditions. (a) Raw images captured by 3.2Mpixel SPAD image sensor. (b) Results of nonlinearity correction. (c) Results of the LE crosstalk correction simultaneously applied. Digital gain is applied to compare the color tone under equivalent contrast for (b) and (c).

# Optimal biasing and physical limits of DVS event noise

Rui Graca, Brian McReynolds, Tobi Delbruck

Sensors Group, Inst. of Neuroinformatics, UZH-ETH Zurich, Zurich, Switzerland rpgraca,bmac,tobi@ini.uzh.ch, https://sensors.ini.uzh.ch

Abstract—Under dim lighting conditions, the output of Dynamic Vision Sensor (DVS) event cameras is strongly affected by noise. Photon and electron shot-noise cause a high rate of non-informative events that reduce Signal to Noise ratio. DVS noise performance depends not only on the scene illumination, but also on the user-controllable biasing of the camera. In this paper, we explore the physical limits of DVS noise, showing that the DVS photoreceptor is limited to a theoretical minimum of 2x photon shot noise, and we discuss how biasing the DVS with high photoreceptor bias and adequate source-follower bias approaches optimal noise performance. We support our conclusions with pixel-level measurements of a DAVIS346 and analysis of a theoretical pixel model.

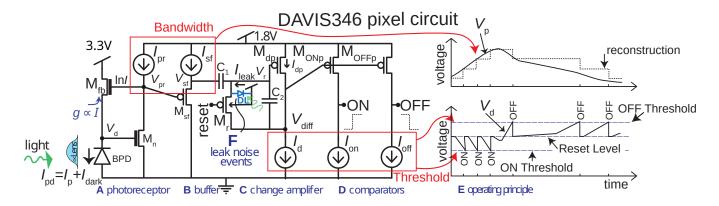

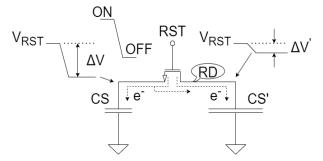

#### I. INTRODUCTION

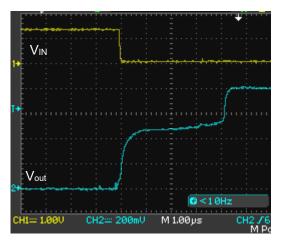

The Dynamic Vision Sensor (DVS) [1]–[4] is a neuromorphic event-based vision sensor, which consists of an array of asynchronously operating pixels as the one in Fig. 1 [4]. Each pixel independently encodes instantaneous changes in its input light into an asynchronous steam of ON and OFF events. More specifically, a pixel outputs an ON event when the relative Temporal Contrast (TC) [1] of light intensity at its input increases by a user defined ON threshold since the last event, or an OFF event when the relative TC increases by a user defined OFF threshold since the last event. When its input is static, a DVS pixel ideally outputs no event. More extensive description of the DVS pixel operation can be found in [1], [5], [6].

Characteristics of the DVS such as sparse data encoding and low latency make it a good candidate for scientific applications such as space situational awareness and widefield voltage and calcium imaging. The adequacy of the DVS for some applications is potentially limited by a too high rate of parasitic Background Activity (BA). BA consists of events that do not encode changes in the input. These events are undesirable because they decrease the Signal-to-Noise Ratio (SNR) and increase data volume [5], [8]. The BA of the DVS pixel strongly depends on both light intensity and camera biasing [3], [6], [9]–[11]. It is predominantly caused by photon and electron shot noise in dark settings [9], and by leakage in the reset transistor (Fig. 1F) in brighter settings [10].

A good understanding of the phenomena resulting in BA is important for improving camera models that can aid pixel design, optimization of the camera utilization, or learning algorithms [5], [6], [12], [13].

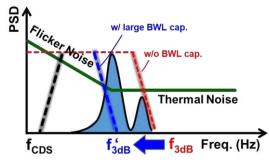

In [9], noise power at the output of the photoreceptor ( $V_{pr}$  in Fig. 1) and noise event rate are explored as a function of

illumination and photoreceptor bias  $I_{pr}$ . There, we observe that both noise power and event rate are lower for lower  $I_{pr}$ . This occurs because the bandwidth is lower for lower  $I_{pr}$ .

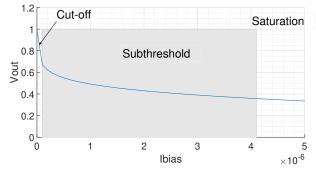

These observations suggest that using a small I<sub>pr</sub> to limit bandwidth reduces noise, and this assumption has been used as an optimization rule for bias control [13]. In this paper, we go a step further into understanding the optimal conditions and biasing of the DVS pixel, and show that in fact the opposite is generally true – even though strongly reducing  $I_{pr}$  leads to a decrease in noise events, noise performance is more optimal for high  $I_{pr}$ . We show that the DVS photoreceptor topology is bounded with a theoretical minimum of 2x photon shot noise, and we discuss bias optimization regarding bandwidth and its implications on noise and signal. In this paper, we focus on the biasing of the photoreceptor (Fig. 1A) by  $I_{pr}$ and the Source-Follower buffer (SF) (Fig. 1B) by  $I_{sf}$ . A more general discussion about bias optimization is presented in [6], and considerations about threshold and refractory biases are discussed in [11].

#### II. OPTIMAL PHOTORECEPTOR BIASING

#### A. PSD Measurements and modeling

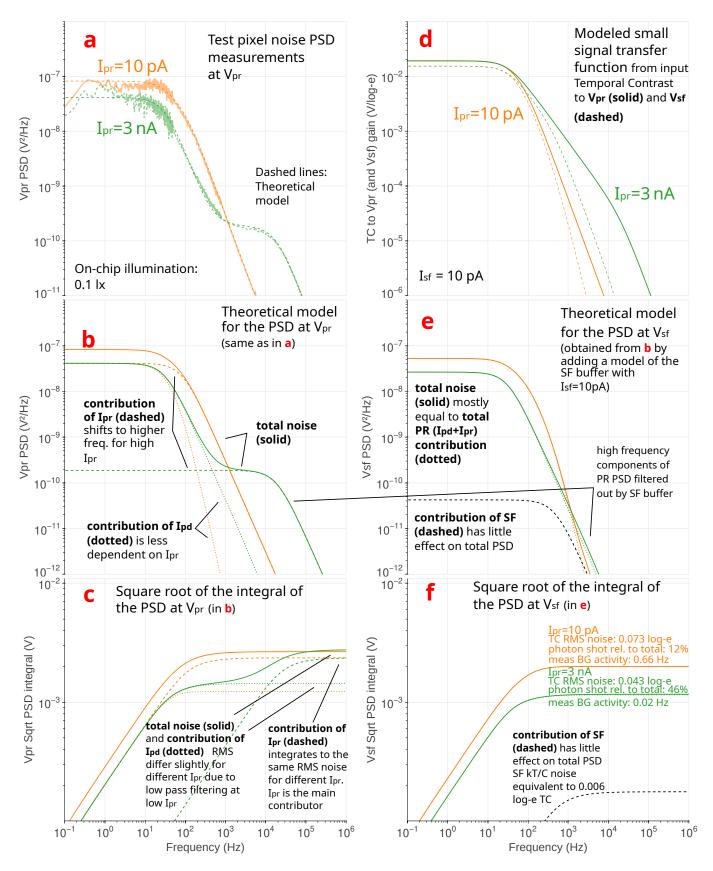

Fig. 2a shows the noise PSD measured at  $V_{\rm pr}$  of a test pixel isolated from a DAVIS346 array under an on-chip illuminance of 0.1 lx for two different  $I_{\rm pr}$  settings: one high (3 nA) and one low (10 pA). The dashed lines in the figure show the PSD predicted by a theoretical physically-realistic model operating under the same conditions. The theoretical model was obtained by circuit analysis considering the sources of shot noise in the photoreceptor and applying the transfer function that relates them to  $V_{\rm pr}$ . The parameters for the model were then estimated and fitted based on SPICE simulation and pixel measurements.

Since the theoretical model generally matches both measured and simulated data, we utilize it to further infer about the noise contribution of each noise source to the total output noise. In Fig. 2b, we see how the contribution of the photocurrent  $I_{pd}$  (depicted by the dotted lines and consisting of photon shot noise at the photodiode and electron shot noise added by M<sub>fb</sub>) and the contribution of  $I_{pr}$  (depicted by the dashed lines, and consisting of noise introduced by M<sub>n</sub> and the transistor implementing  $I_{pr}$ ) add up to the total PSD. Here, we observe that the level of the contribution of  $I_{pd}$  is independent of  $I_{pr}$ , but its bandwidth may depend on  $I_{pr}$  – for a bias of 10 pA,  $I_{pr}$  is right at the edge of starting to filter out the  $I_{pd}$  contribution. That is, this contribution would be

Fig. 1. Typical DVS pixel circuit [7]. The active logarithmic photoreceptor (A) is buffered by a source-follower (B), which drives a cap-feedback change amplifier (C), which is reset on each event by a low-going *reset* pulse. A finite refractory period holds the change amplifier in reset for the refractory period  $\Delta_{\text{refr.}}$ . Comparators (D) detect ON and OFF events as seen in E. Periodic leak events result from junction and parasitic photocurrent  $I_{\text{leak}}$  in diode DL (F).

significantly reduced for lower  $I_{\rm pr}$ , and would become constant for higher  $I_{\rm pr}$  (as happens for  $I_{\rm pr}$  of 3 nA. On the other hand, the contribution of  $I_{\rm pr}$  moves to higher frequencies when  $I_{\rm pr}$ increases.

Fig. 2c shows the square root of the integral of the different components of the PSD in Fig. 2b. The final value of the square root of the integral is the RMS voltage noise contribution of its respective source. We see that the contribution of  $I_{\rm pr}$  converges to a value independent of  $I_{\rm pr}$  - the contribution is only shifted to higher frequencies. The contribution of  $I_{\rm pd}$  is lower for lower  $I_{\rm pr}$ , which happens due to filtering by  $I_{\rm pr}$  [9]. For higher values of  $I_{\rm pr}$ , filtering would stop occurring and the contribution of  $I_{\rm pd}$  converges to the constant value observed at  $I_{\rm pr}$  of 3 nA.

Figs. 2e and 2f show the modeled PSDs and the square root of their integrals for the contributors at the output of the SF,  $V_{sf}$ . The PSDs were obtained by filtering the ones at  $V_{pr}$  using a model of the SF estimated by circuit inspection and simulation. Also, the noise contribution of  $I_{sf}$  is added in the dashed line. However, its value is much smaller than the contribution of the photoreceptor (the summation of the contributions of  $I_{pd}$  and  $I_{pr}$ ).

Fig. 2d shows the modeled signal transfer function from logarithmic changes in light intensity to voltages at  $V_{pr}$  and  $V_{sf}$ . As described in [9], it can be approximately modeled as a second order system with one pole dependent on  $I_{pd}$  and the other dependent on  $I_{pr}$ . At  $I_{pr}$  of 3 nA, the pole controlled by  $I_{pd}$  is clearly dominant, while for  $I_{pr}$  of 10 pA the two poles lie very close to each other. The SF add another pole, which for the bias used is close to the dominant of the photoreceptor.

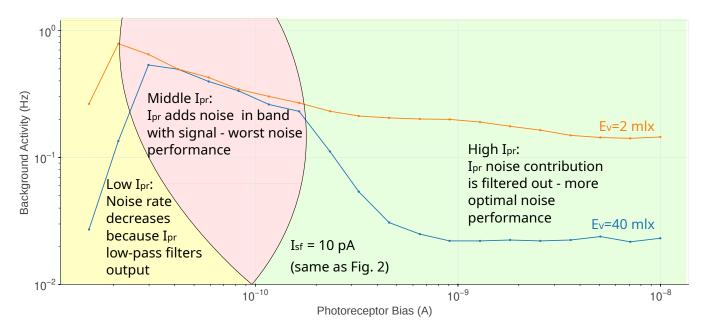

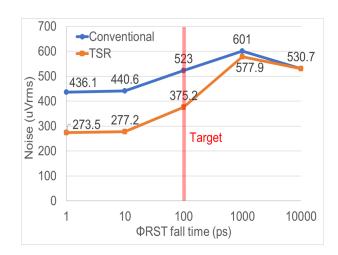

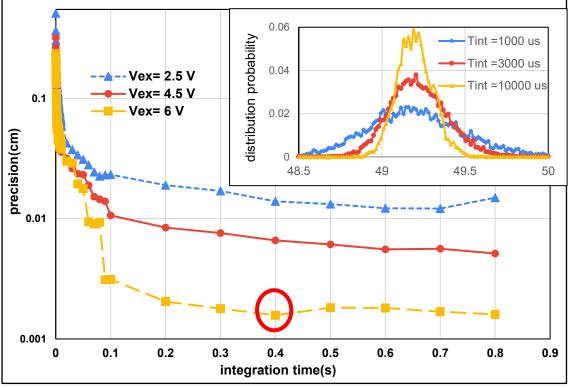

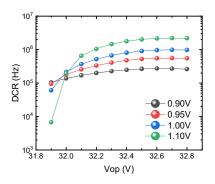

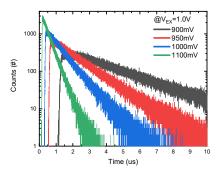

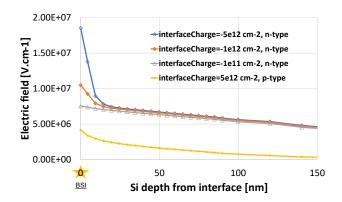

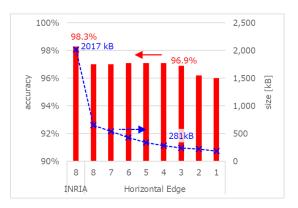

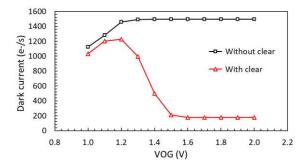

Fig. 3 show the noise rates measured from the same test pixel for varying  $I_{pr}$  for two different on-chip illumination levels. We observe that for high  $I_{pr}$ , noise rate becomes mostly constant, since all the noise components of  $I_{pr}$  are filtered out. For middle  $I_{pr}$  values, the noise contributions of  $I_{pr}$  lie within the signal bandwidth and are not filtered out, and the noise rates peak. For lower  $I_{pr}$  the noise rates decrease because  $I_{pr}$  limits the bandwidth.

#### B. Optimal biasing and optimality analysis

From Fig. 2c we can see how strongly biasing  $I_{pr}$  results in shifting the noise components added by  $I_{pr}$  to higher frequencies outside the bandwidth of interest for signal. This means that we can filter them out using the SF without consequences for signal. In the limit, if we bias  $I_{pr}$  so strongly that all its contribution is removed by SF, the output noise consists of only the noise contribution of  $I_{pd}$  (which consists itself on equal parts of photon shot noise and M<sub>fb</sub> noise), and the much smaller noise contribution of  $I_{sf}$ . In this case, we are theoretically limited to a minimum of 2x photon shot noise when the contribution of  $I_{sf}$  becomes negligible.

The clear advantage of strongly biasing  $I_{\rm pr}$  is illustrated in Fig. 2f. For  $I_{\rm pr}$  of 3 nA, the model predicts a contribution of photon shot noise of 46% (approximating the theoretical limit of 50%), resulting in a noise event rate of 0.02 Hz under nominal threshold and refractory biases [6] versus 12% for  $I_{\rm pr}$  of 10 pA, resulting in a noise event rate of 0.66 Hz.

The model predicts an RMS noise contribution equivalent to TC log-e units of 0.006 for  $I_{\rm sf}$ . The contributions of  $I_{\rm pd}$  and  $I_{\rm pr}$ depend on filtering, but for the case where the pole controlled by  $I_{pd}$  is dominant and filtering by the SF is not considered, they are respectively 0.04 and 0.06 for most values of  $I_{pd}$  and  $I_{\rm pr}$ . Although **RMS** noise alone is not enough to characterize DVS noise, since it does not contain information about the noise frequency [9], these numbers are useful to evaluate design limitations to the event sensitivity (i.e. the minimum event threshold with acceptable noise rates). One important conclusion is that  $I_{sf}$  should be adjusted to the minimum acceptable bandwidth for each application and  $I_{pr}$  should be adjusted so that all its contributions are filtered out. Given that increasing  $I_{pr}$  increases power consumption,  $I_{pr}$  should be optimized to trade off power with noise performance. In the limit where the photoreceptor bandwidth is much higher than the SF bandwidth (which happens for very high illuminance, high  $I_{pr}$  and nominal or low  $I_{sf}$ ) the noise, noise introduced by  $I_{pd}$  and  $I_{pr}$  is filtered out and SF becomes the main noise contributor.

Fig. 2. (a) shows noise PSDs measured from a DAVIS346 test pixel for two different  $I_{pr}$  biases for an on-chip illuminance of 0.1 lx and the PSDs estimated by a theoretical model for the same conditions. (b) shows the estimated contributions of  $I_{pr}$  and  $I_{pd}$  to the total PSD for the same model in the same conditions, and (c) shows the square root of the integral of the curves in (b). The final value of these curves is the respective contribution to the RMS noise voltage at  $V_{pr}$ . (c) and (f) show the same quantities as (b) and (c), but relative to  $V_{sf}$ . (d) shows the estimated signal transfer function from TC (in log-e units) to  $V_{pr}$ and  $V_{sf}$ .

Fig. 3. Background activity measured from a DAVIS346 test pixel under constant on-chip illuminance of 2 mlx (orange line) and 40 mlx (blue line) for  $I_{sf}$  of 10 pA (as in Fig. 2) and nominal threshold and refractory bias settings (see [6] for a characterization of these parameters, nominal settings corresponds to tweaks of 0 there).

Filtering with SF and not with  $I_{pr}$  is generally a better idea since it introduces significantly less noise, and the noise it introduces is not filtered out in any case. However, in practical DVS implementations operating in very dark settings, very low  $I_{pr}$  may result in a lower bandwidth than the minimum achievable by the SF, and minimizing both  $I_{pr}$  and  $I_{sf}$  may result in less BA.

#### III. CONCLUSION

The measurements and analysis presented show that the DVS pixel is limited to a minimum of 2x photon shot noise, and that using high  $I_{pr}$  and adequate  $I_{sf}$  approximates this limit. We also discuss the limits imposed to event sensitivity by each noise contributor.

#### REFERENCES

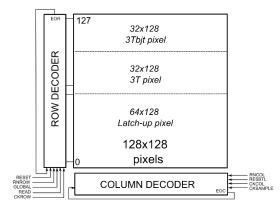

- P. Lichtsteiner, C. Posch, and T. Delbruck, "A 128×128 120 dB 15 μs latency asynchronous temporal contrast vision sensor," *IEEE Journal* of Solid-State Circuits, vol. 43, no. 2, pp. 566–576, 2008.

- [2] Y. Suh, S. Choi, M. Ito, *et al.*, "A 1280×960 dynamic vision sensor with a 4.95-μm pixel pitch and motion artifact minimization," in 2020 *IEEE International Symposium on Circuits and Systems (ISCAS)*, 2020, pp. 1–5. DOI: 10.1109/ISCAS45731.2020.9180436.

- [3] T. Finateu, A. Niwa, D. Matolin, et al., "5.10 a 1280×720 backilluminated stacked temporal contrast event-based vision sensor with 4.86µm pixels, 1.066GEPS readout, programmable event-rate controller and compressive data-formatting pipeline," in 2020 IEEE International Solid- State Circuits Conference - (ISSCC), 2020, pp. 112–114. DOI: 10.1109/ISSCC19947.2020.9063149.

- [4] C. Brandli, R. Berner, M. Yang, S. Liu, and T. Delbruck, "A 240 x 180 130 dB 3 μs latency global shutter spatiotemporal vision sensor," *IEEE Journal of Solid-State Circuits*, vol. 49, no. 10, pp. 2333–2341, 2014. DOI: 10.1109/JSSC.2014.2342715.

- [5] Y. Hu, S.-C. Liu, and T. Delbruck, "V2e: From video frames to realistic DVS events," in *Proceedings of the IEEE/CVF Conference* on Computer Vision and Pattern Recognition (CVPR) Workshops, Jun. 2021, pp. 1312–1321.

- [6] R. Graca, B. McReynolds, and T. Delbruck, "Shining light on the DVS pixel: A tutorial and discussion about biasing and optimization," in 2023 IEEE/CVF Conference on Computer Vision and Pattern Recognition Workshops (CVPRW), Jun. 2023. DOI: 10.48550/arXiv. 2304.04706.

- [7] G. Taverni, D. Paul Moeys, C. Li, et al., "Front and back illuminated dynamic and active pixel vision sensors comparison," *IEEE Trans*actions on Circuits and Systems II: Express Briefs, vol. 65, no. 5, pp. 677–681, 2018.

- [8] S. Guo and T. Delbruck, "Low cost and latency event camera background activity denoising," *IEEE Transactions on Pattern Analysis* and Machine Intelligence, vol. 45, no. 1, pp. 785–795, 2023. DOI: 10.1109/TPAMI.2022.3152999.

- [9] R. Graca and T. Delbruck, "Unraveling the paradox of intensitydependent DVS pixel noise," in 2021 International Image Sensor Workshop (IISW), Sep. 2021. DOI: 10.48550/ARXIV.2109.08640.

- [10] Y. Nozaki and T. Delbruck, "Temperature and parasitic photocurrent effects in dynamic vision sensors," *IEEE Transactions on Electron Devices*, vol. 64, no. 8, pp. 3239–3245, Aug. 2017, ISSN: 1557-9646. DOI: 10.1109/TED.2017.2717848.

- [11] B. McReynolds, R. Graca, and T. Delbruck, "Exploiting alternating DVS shot noise event pair statistics to reduce background activity," in 2023 International Image Sensor Workshop (IISW), May 2023. DOI: 10.48550/arXiv.2304.03494.

- [12] B. J. McReynolds, R. P. Graca, and T. Delbruck, "Experimental methods to predict dynamic vision sensor event camera performance," *Optical Engineering*, vol. 61, no. 7, p. 074 103, 2022. DOI: 10.1117/ 1.OE.61.7.074103.

- [13] T. Delbruck, R. Graca, and M. Paluch, "Feedback control of event cameras," in 2021 IEEE/CVF Conference on Computer Vision and Pattern Recognition Workshops (CVPRW), 2021, pp. 1324–1332. DOI: 10.1109/CVPRW53098.2021.00146.

# Metasurface-based planar microlenses for SPAD pixels

Jérôme Vaillant Univ. Grenoble Alpes CEA, LETI 38000 Grenoble, France jerome.vaillant@cea.fr

Quentin Abadie Univ. Grenoble Alpes CEA, LETI 38000 Grenoble, France <u>quentin.abadie@cea.fr</u>

Mickaël Cavelier Univ. Grenoble Alpes CEA, LETI 38000 Grenoble, France mickael.cavelier@cea.fr Lucie Dilhan STMicroelectronics Imaging division Grenoble, France Iucie.dilhan@st.com

Lilian Masarotto Univ. Grenoble Alpes CEA, LETI 38000 Grenoble, France lilian.masarotto@cea.fr

Cyril Bellegarde Univ. Grenoble Alpes CEA, LETI 38000 Grenoble, France cyril.bellegarde@cea.fr

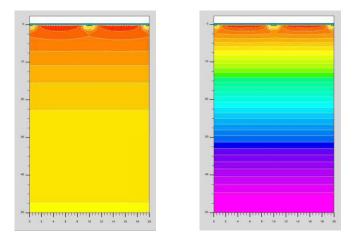

Abstract— In this paper we present two design generations of metasurface-based planar microlenses implemented on Front-Side Illumination SPAD pixels. This kind of microlens is an alternative to conventional reflow microlens. It offers more degrees of freedom in term of design, especially the capability to design off-axis microlens to gather light around the SPAD photodiode. The two generations of microlenses have been fabricated on STMicroelectronics SPAD and characterized. We validated the sensitivity improvement offered by extended metasurface-based microlens. We also confirmed the impact of lithography capability on metasurface performances, highlighting the need have access to advance deep-UV lithography.

Keywords— metasurface, planar microlens, pixel, SPAD

#### I. INTRODUCTION

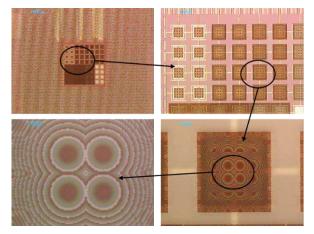

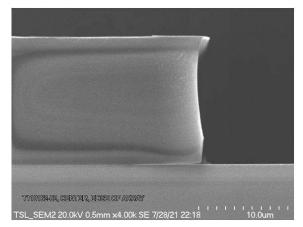

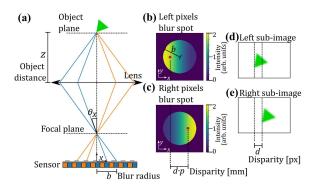

Planar microlenses are well suited for SPAD pixels, which usually work under monochromatic illumination (Time-of-Flight or Fluorescence-Lifetime applications) and exhibit rather large pixel size with lower fill-factor compared to state-of-the-art CMOS pixels. We previously demonstrated Fresnel Zone Plate lenses[1] and proposed metasurface based[2] microlenses[3], [4]. In this paper, we present the design, fabrication and characterization results of two generations of metasurface-based planar microlenses on STMicroelectronics SPAD[5] array.

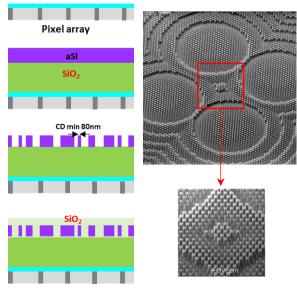

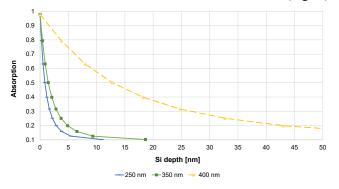

### II. META-ATOM AND PLANAR MICROLENS DESIGN

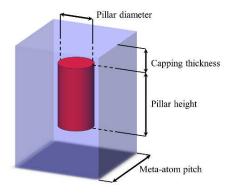

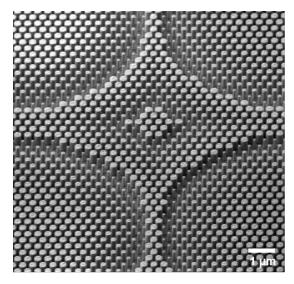

Our unitary structure, or meta-atom, is a nanoscale pillar of high refractive index material (amorphous silicon) embedded in a low refractive index medium (silicon oxide). The phase shift induced by a pillar is controlled by its geometry which is defined by the pitch, Alain Ostrovsky STMicroelectronics TR&D Crolles, France alain.ostrovsky@st.com

Romain Paquet Univ. Grenoble Alpes CEA, LETI 38000 Grenoble, France romain.paquet@cea.fr

the capping thickness and the pillar's parameters: height and diameter (see Fig. 1).

Fig. 1. Geometry of meta-atom defined by the meta-atom pitch, the thickness of silicon oxide capping and the pillar height and diameter

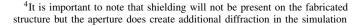

We have also considered the paving strategy. For the first generation of metasurface-based microlens, we considered square paving for meta-atom arrangement. In order to improve the spatial sampling, triangular paving (see Fig. 2) was also implemented in the second generation.

Fig. 2. Paving geometries used to design metasurface: square paving (left) and triangular paving (right)

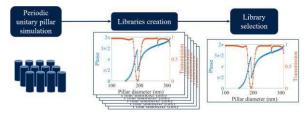

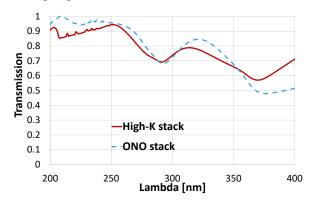

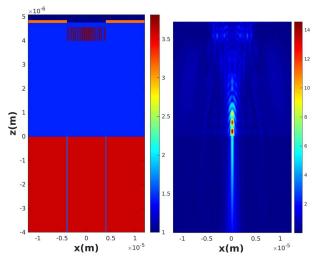

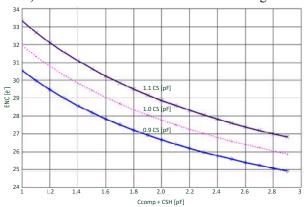

We defined pillar libraries as sets of pillar with the paving and the first three parameters fixed and the pillar's diameter varies inside the range achievable by lithography: the minimal diameter is defined by the minimal Critical Dimension (CD) and the maximal diameter is defined as meta-atom pitch minus the minimal space. Among all possible libraries, we select the ones that cover a phase shift from 0 to  $2\pi$  while offering the best transmission (see Fig. 3).

Fig. 3. Library generation and selection workflow

First generation of libraries is based on 500nm and 420nm pitches whereas the second generation is more aggressive with meta-atom pitch of 370nm. In both case, the minimum CD and space considered are 100nm.

#### **III. PLANAR MICROLENS DESIGNS**

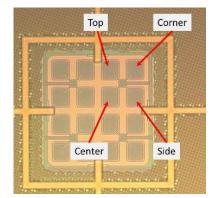

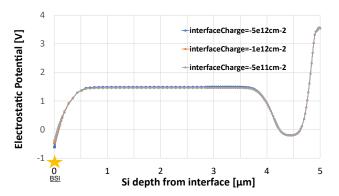

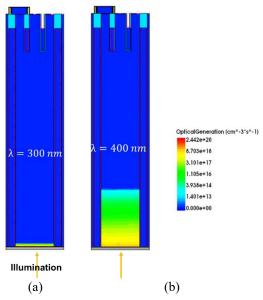

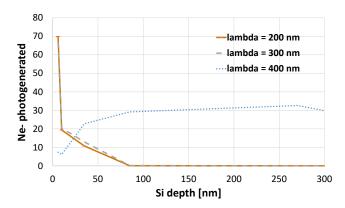

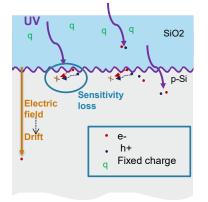

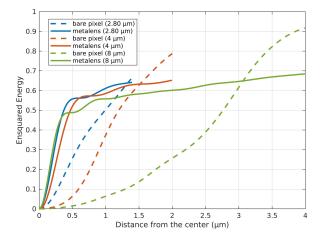

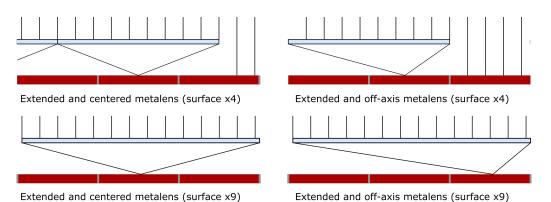

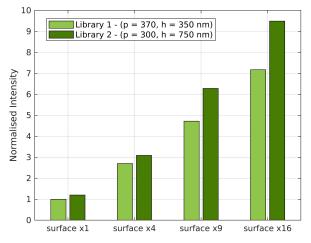

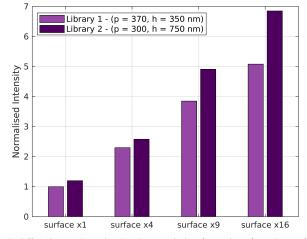

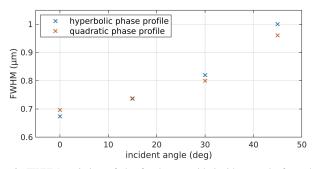

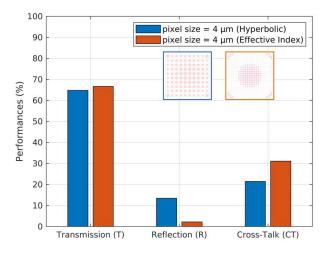

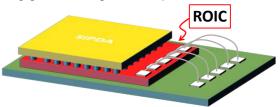

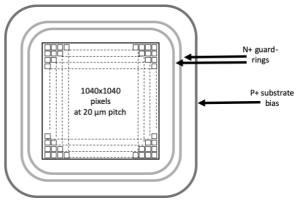

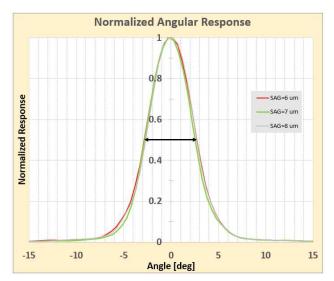

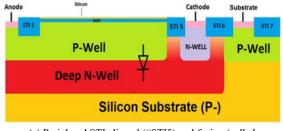

#### A. SPAD pixel